使用 Verilog HDL 进行数字逻辑设计、综合、仿真的步骤及

工具软件使用简要说明

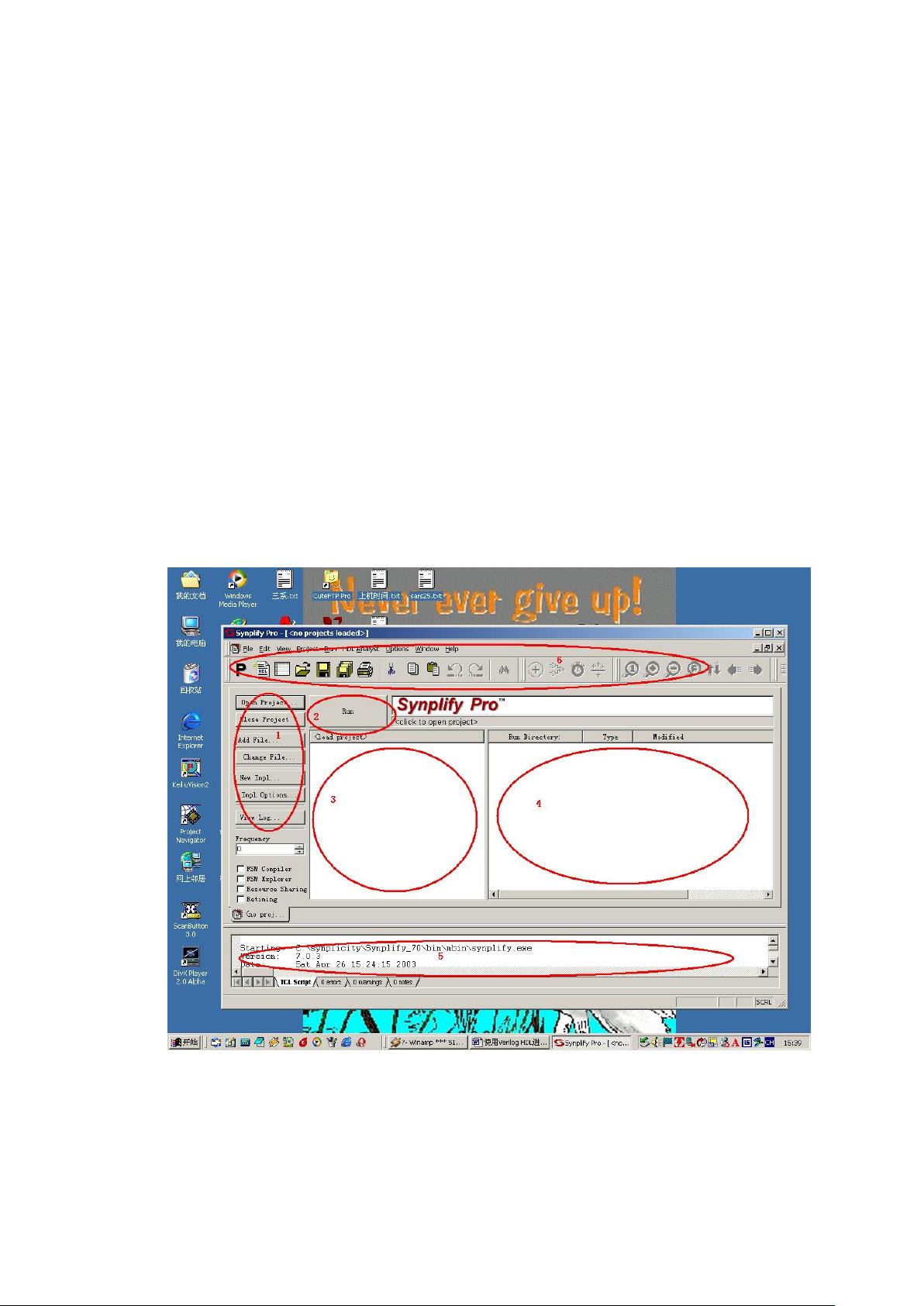

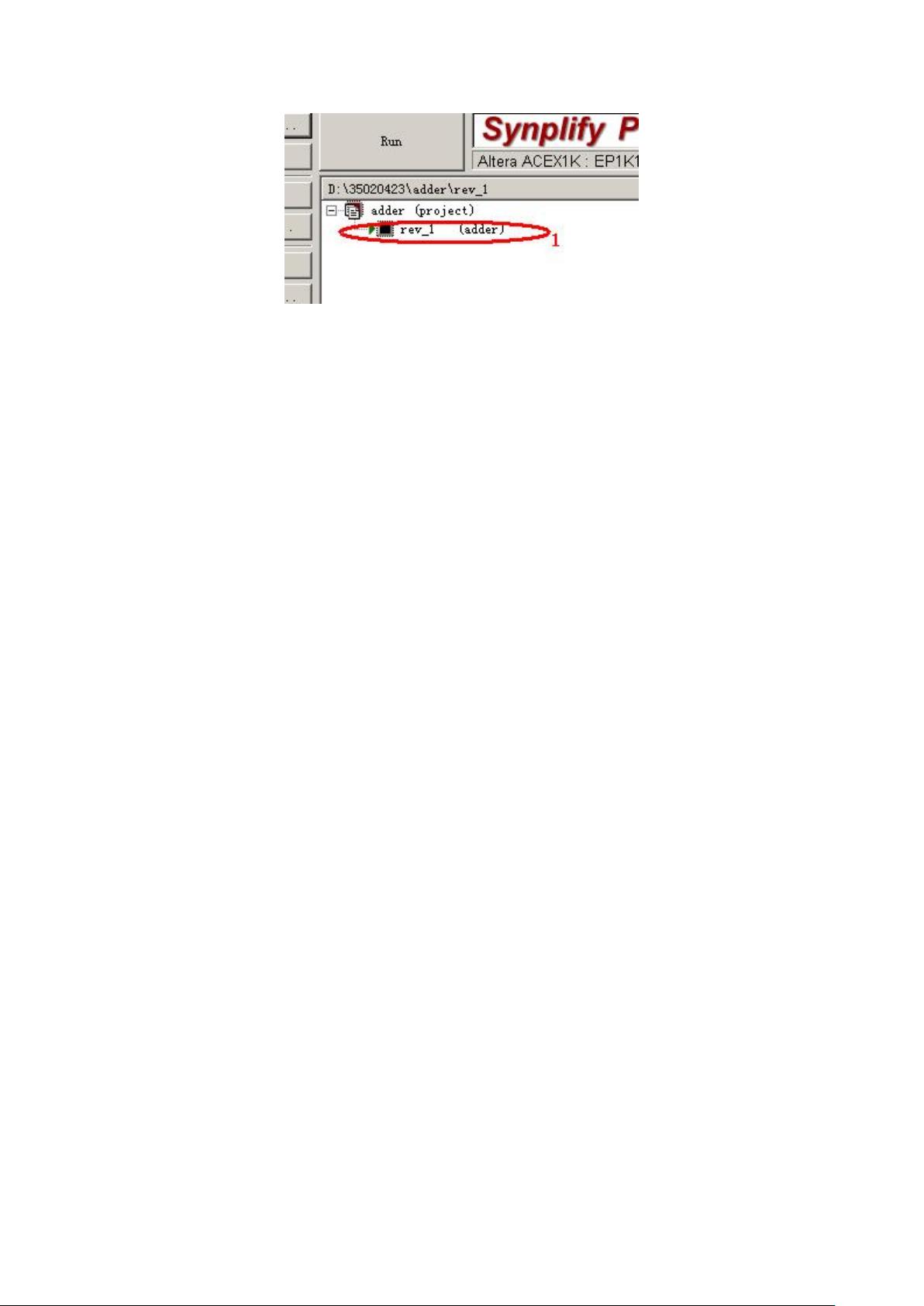

综合工具使用 synplify pro 7.0

仿真工具使用 modelsim 5.5e (几个菜单排列与 5.6 有不同,文中有介绍)

布局布线工具及时序仿真模型生成使用 maxplusII 10.0

一.写在开干之前

1. 涉及到的文件

a. 源程序 (*.v)

用户编写的用于描述所需电路的 module (可能有多个文件,多个 module 相互调用)

如果用于综合,则源程序内用于描述的 Verilog 语言必须是可综合风格的。否则将

只能做功能仿真(前仿真),而不能做综合后的仿真和时序仿真(后仿真)。

b. 综合后的 Verilog HDL 模型(网表) (*.vm)

用综合工具 synplify 对 a 进行综合后生成的电路的 Verilog HDL 描述。由 synplify

自动生成(必须在 Implementation Option — Implementation results 选项中选中 write

mapped verilog netlist 后才会生成 vm 文件)。

此文件用于作综合后的仿真

c. 布局布线后生成的时序仿真模型(网表) (*.vo)文件

使用 maxplusII 对设计进行布局布线之后,生成的带有布局布线及具体器件延迟特

性等参数的电路模型的 Verilog HDL 描述。

要让 maxplusII 生成 vo 文件,必须在 maxplusII 的 compile interface 中选中 verilog

netlist writer。

此文件用于作时序仿真(后仿真)

d. 测试文件(*.v 或*.tf)

用户编写的 Verilog HDL 源程序。用于测试源程序(a,b,c)中所描述电路。

在测试文件中调用被测试的 module,生成被测点路所需的输入信号。

所用 Verilog HDL 语句不需要是可以综合的,只需语法正确。

如果被测试的模型为 a,则对应的仿真为前仿真(功能仿真)

如果被测试的模型为 b, 则对应的仿真为综合后仿真

如果被测试的模型为 c, 则对应的仿真为后仿真

2. 强烈建议

a. 在写用于综合的源程序时,一个源程序文件里只写一个 module

b. 源 程 序 文 件 名 与 其 内 所 描 述 的 module 名 相 同 ( 如 module myadder 文 件 名

myadder.v)

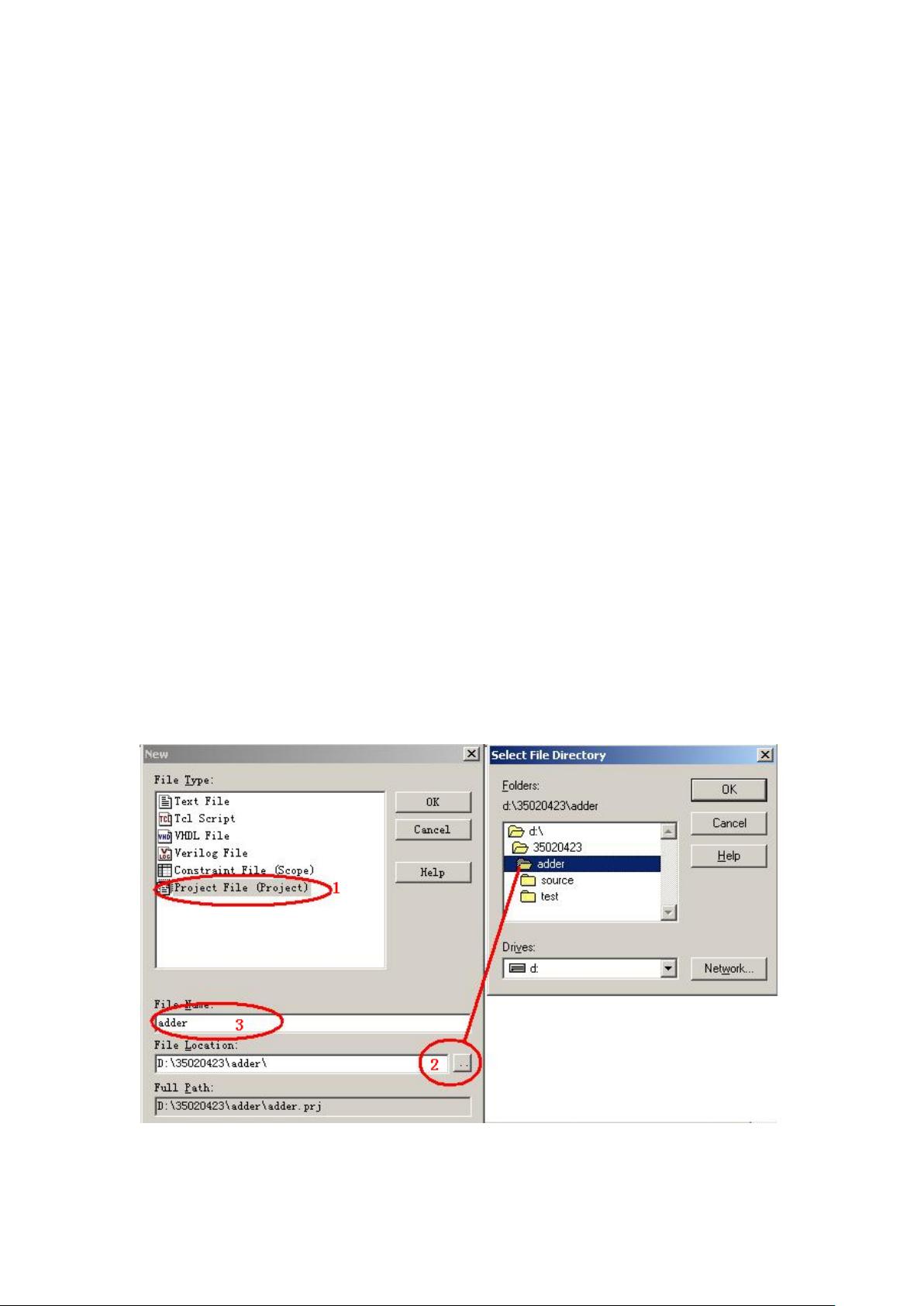

c. 为了方便管理文件,为每一个设计都单独创建一个目录,目录内创建 source, test 子

目录分别用于存放源程序(用于综合的)和测试文件。

d. 在 F 盘创建一个以自己学号为名的目录,将自己的设计都存放在这个目录下面

e. 不要使用包含中文字符或空格的目录名和文件名,因为有些工具软件不支持

f. 以上建议不一定是必须的,但是可以减少设计中的很多麻烦,请各位同学尽量采纳。