Copyright Notice and Proprietary Information

Copyright © 2010 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information

that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or

copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced,

transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written

permission of Synopsys, Inc., or as expressly provided by the license agreement.

Destination Control Statement

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals

of other countries contrary to United States law is prohibited. It is the reader’s responsibility to determine the applicable regulations and

to comply with them.

Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS

MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A

PARTICULAR PURPOSE.

Registered Trademarks (®)

Synopsys, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, CRITIC, Certify, CHIPit, Design Compiler,

DesignWare, Formality, HDL Analyst, HSIM, HSPICE, Identify, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Physical

Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Syndicated, Synplicity, the Synplicity Logo, Synplify,

Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered

trademarks of Synopsys, Inc.

Trademarks (™)

AFGen, Apollo, Astro, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Confirma, Cosmos, CosmosLE,

CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision,

DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, Galaxy Custom Designer,

HANEX, HAPS, HapsTrak, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping Ssytem,

HSIMplus, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library

Compiler, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, Physical Analyst, Planet,

Planet-PL, Polaris, Power Compiler, Raphael, Saturn, Scirocco, Scirocco-i, Star-RCXT, Star-SimXT, StarRC, Taurus, TotalRecall,

TSUPREM-4, VCS Express, VCSi, VHDL Compiler, VirSim, and VMC are trademarks of Synopsys, Inc.

Service Marks (

SM

)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license.

ARM and AMBA are registered trademarks of ARM Limited.

Saber is a registered trademark of SabreMark Limited Partnership and is used under license.

PCI Express is a trademark of PCI-SIG.

All other product or company names may be trademarks of their respective owners.

Synopsys, Inc.

700 E. Middlefield Road

Mountain View, CA 94043

www.synopsys.com

2 Synopsys, Inc. September 2010

DesignWare DW_apb_timers Databook

September 2010 Synopsys, Inc. 11

DesignWare DW_apb_timers Databook Product Overview

SolvNet

DesignWare.com

1

Product Overview

The DW_apb_timers is a programmable timers peripheral. This component is an AMBA 2.0-compliant

Advanced Peripheral Bus (APB) slave device and is part of the family of DesignWare Synthesizable

Components.

1.1 DesignWare System Overview

The Synopsys DesignWare Synthesizable Components environment is a parameterizable bus system

containing AMBA version 2.0-compliant AHB (Advanced High-performance Bus) and APB (Advanced

Peripheral Bus) components, and AMBA version 3.0-compliant AXI (Advanced eXtensible Interface)

components.

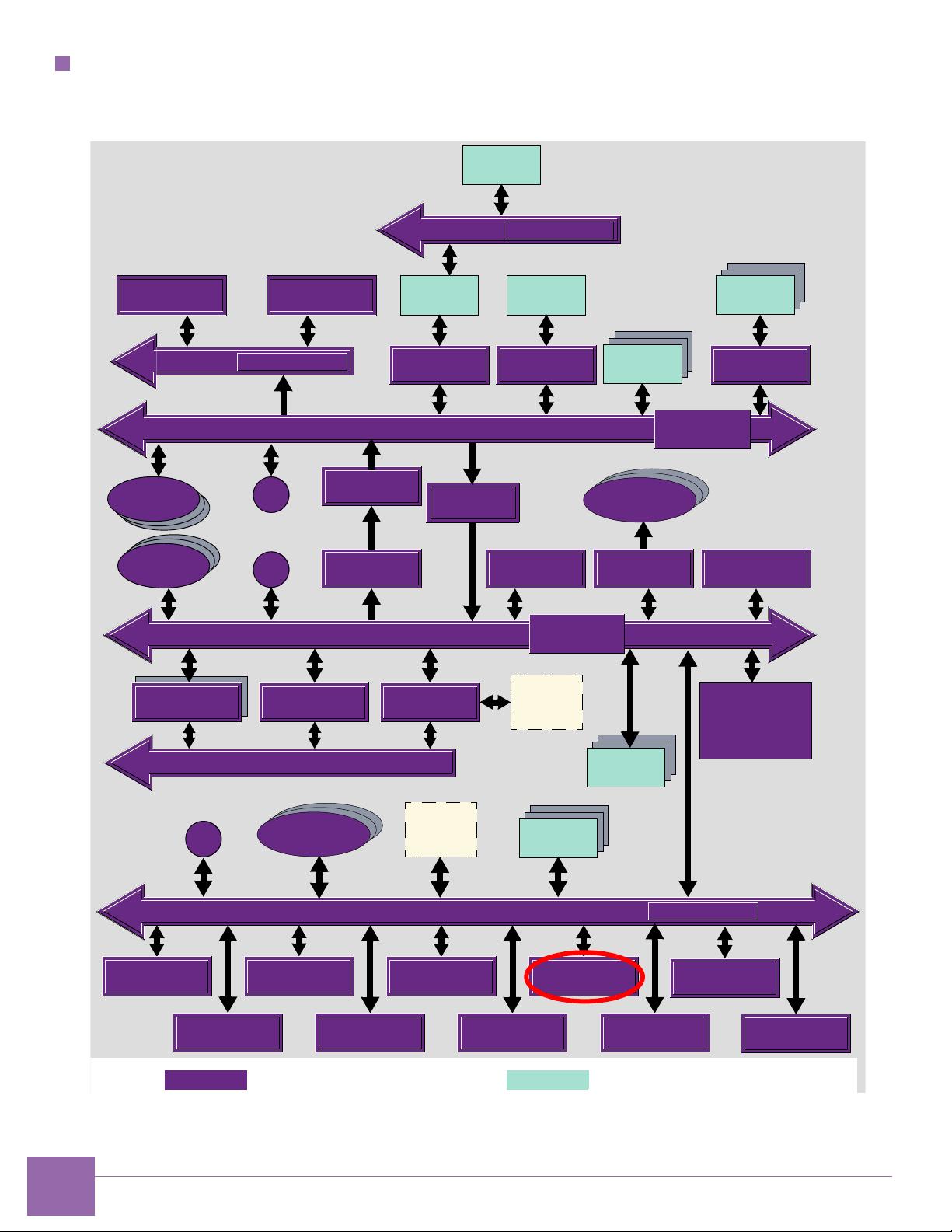

Figure 1-1 illustrates one example of this environment, including the AXI bus, the AHB bus, and the APB

bus. Included in this subsystem are synthesizable IP for AXI/AHB/APB peripherals, bus bridges, and an

AXI interconnect and AHB bus fabric. Also included are verification IP for AXI/AHB/APB master/slave

models and bus monitors.

Attention

12 Synopsys, Inc. September 2010

Product Overview DesignWare DW_apb_timers Databook

SolvNet

DesignWare.com

Figure 1-1 Example of DW_apb_timers in a Complete System

apb_monitor_vmt

DW_ahb (2)

DW_ahb_icm

DW_ahb_h2h,

DW_ahb_eh2h

Application-

Specific

Third-party

Peripherals

Logic

Application-

Specific

Logic

High-speed

USB, Ethernet,

PCI-X, and so on

Peripherals

DW_ahb

DW_ahb

Arbitration,

Decode, & Mux

Third-party

Peripherals

DW_ahb_dmac

APB Slave

VIP

AHB

VIP

Master/Slave

Third-party

Master

Third-party

Slave

DW_axi_gm DW_axi_gs

DW_ahb

DW_axi

Arbitration,

Decode, & Mux

axi_monitor_vmt

– Synopsys components – 3rd-party components

Third-party

Master/Slave

DW_axi_rs

Third-party

Master/Slave

AXI

VIP

Master/Slave

DW_ahb_eh2h

DW_axi_hmx

DW_axi_x2p

AMBA 3 Bridge

DW_apb_uart DW_apb_i2c

…

ahb_monitor_vmt

DW_memctl DW_ahb_dmacDW_ahb_ictl

RAM

Memory Models

DW_axi_x2h

Third-party

Slave

DW_axi_x2x

AMBA 3 Bridge

DW_ahb

DW_apb AHB/APB Bridge

DW_apb_ictl

DW_apb_rtc

DW_apb_uart

DW_apb_ssi

DW_apb_rap DW_apb_timers

DW_apb_wdtDW_apb_gpio

DW_apb_i2c

DW_apb_i2s

September 2010 Synopsys, Inc. 13

DesignWare DW_apb_timers Databook Product Overview

SolvNet

DesignWare.com

1.2 General Product Description

The Synopsys DW_apb_timers is a component of the DesignWare Advanced Peripheral Bus (DW_apb).

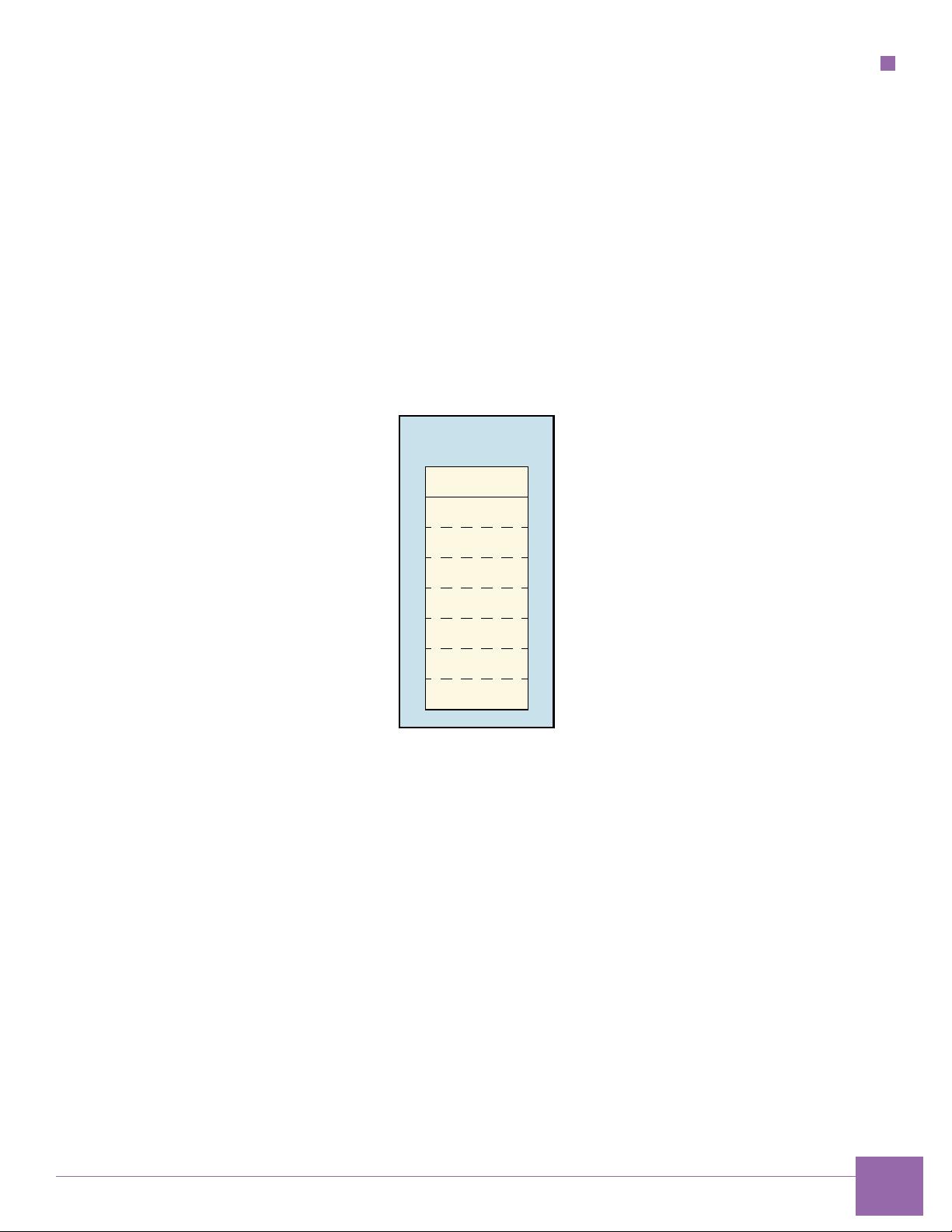

1.2.1 DW_apb_timers Block Diagram

Figure 1-2 shows the block diagram of the DW_apb_timers.

Figure 1-2 DW_apb_timers Block Diagram

1.3 Features

DW_apb_timers has the following features:

❖ Up to eight programmable timers

❖ Configurable timer width: 8 to 32 bits

❖ Support for two operation modes: free-running and user-defined count

❖ Support for independent clocking of timers

❖ Configurable polarity for each individual interrupt

❖ Configurable option for a single or combined interrupt output flag

❖ Configurable option to have read/write coherency registers for each timer

❖ Configurable option to include timer toggle output, which toggles whenever timer counter reloads

Source code for this component is available on a per-project basis as a DesignWare Core. Please contact your

local sales office for the details.

DW_apb_timers

Timer1

TimerN*

Timer2

*

N <= 8

评论17