FPGA管脚分配需要考虑的因素.rar_FPGA管脚分配

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

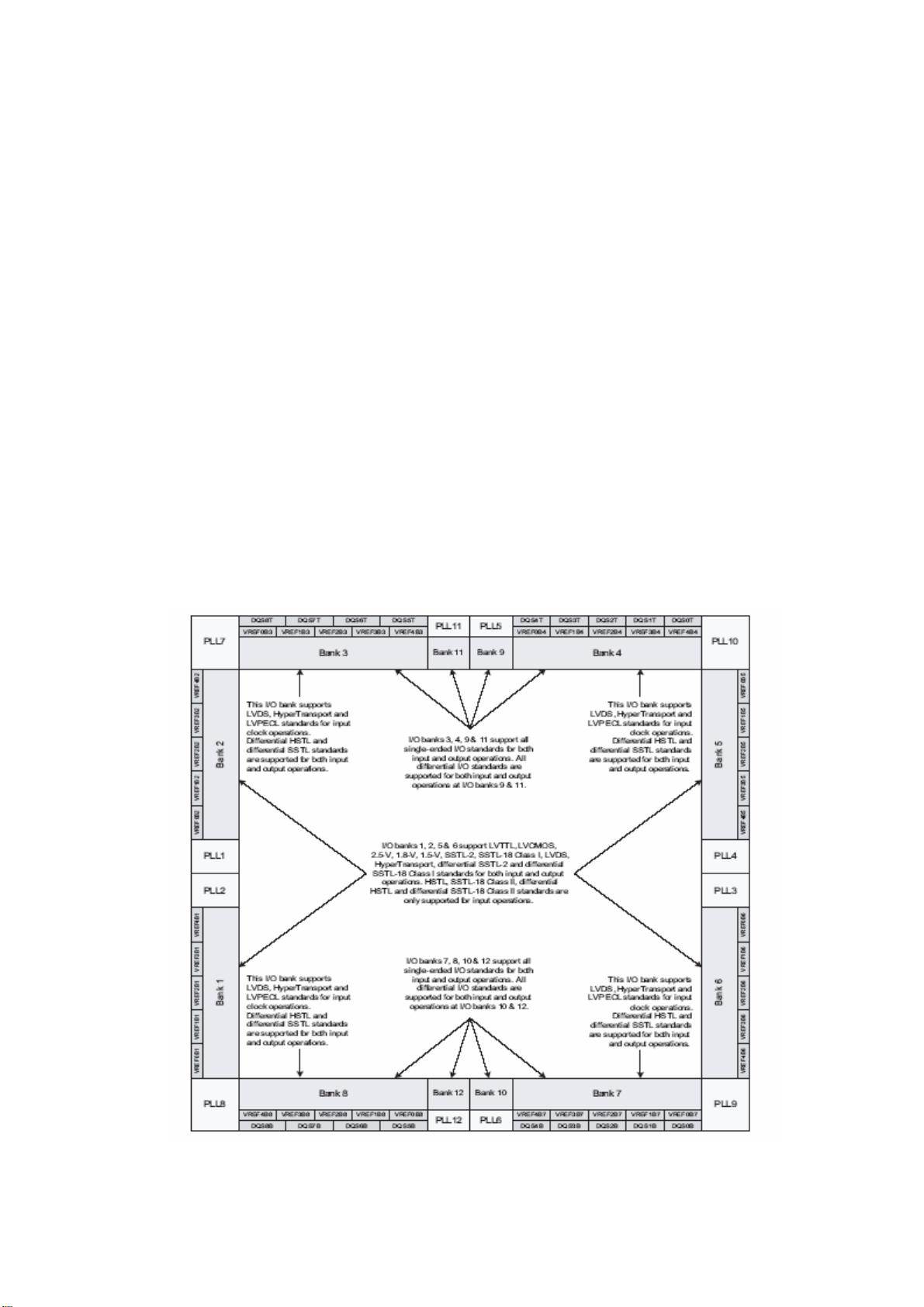

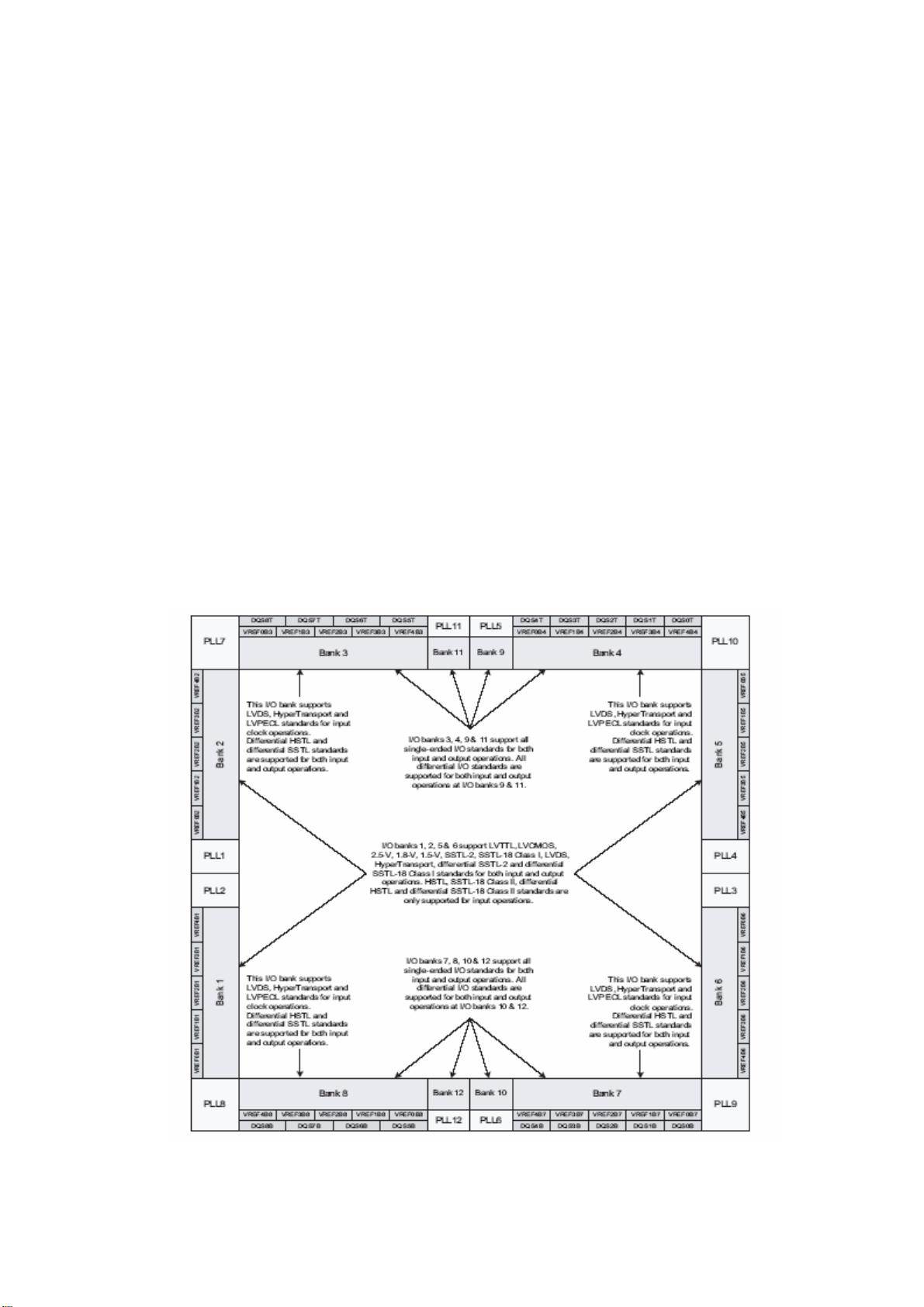

在FPGA(Field-Programmable Gate Array)设计中,管脚分配是一个至关重要的步骤,它直接影响着设计的性能、功耗以及实现的难度。理解并掌握管脚分配的策略和考虑因素对于优化FPGA设计至关重要。以下是关于FPGA管脚分配的一些关键知识点: 1. **I/O标准匹配**:不同的FPGA管脚支持多种I/O标准,如LVCMOS、LVTTL、HSTL等。在分配时,必须确保管脚的I/O标准与外部电路的接口标准相匹配,以确保信号的正确传输。 2. **信号路由长度**:在FPGA内部,信号需要通过布线资源进行传输。分配时,应尽量减小关键路径上信号的延迟差异,以避免时序问题。对于高速信号,更需控制信号的传播延迟,保持时钟树的均衡。 3. **电源和地的分布**:电源和地的布局对信号完整性和电源完整性有很大影响。通常,电源和地管脚应紧密配对,减少电源噪声,并且尽量靠近使用它们的逻辑单元,以降低电源线上的压降。 4. **时钟管脚**:时钟是系统的心脏,其分配极为关键。时钟管脚应尽可能分配到离逻辑单元近且布线资源丰富的区域,同时要注意时钟的扇出数,避免过多的时钟分支导致信号质量下降。 5. **输入/输出缓冲器的使用**:FPGA通常包含可编程的输入/输出缓冲器,用于驱动外部负载或吸收外部信号。根据负载特性,合理配置这些缓冲器可以提高信号质量,降低功耗。 6. **功耗考虑**:管脚分配时要考虑功耗问题,比如,可以将低功耗的I/O放在电路板的边缘,以减少电源线长度,降低功耗。此外,尽量减少高功耗I/O与低功耗I/O之间的连接,以减少功耗的相互影响。 7. **热管理**:高温可能会导致器件性能下降甚至损坏。因此,应尽量将产生热量较多的I/O远离敏感组件,以保持良好的散热条件。 8. **抗干扰设计**:在高速数字系统中,信号间的串扰不容忽视。合理分配管脚,使高噪声信号和低噪声信号分开,可以有效降低串扰影响。 9. **测试性与可维护性**:在设计初期就应考虑测试接口的分配,以便于后期的调试和故障定位。例如,JTAG(Joint Test Action Group)接口的管脚应易于访问。 10. **设计约束**:根据具体的FPGA器件和设计要求,可能还需要考虑其他约束,如管脚的最大驱动电流、最小驱动能力、ESD保护等。 FPGA管脚分配是一个涉及多方面因素的复杂任务,需要综合考虑信号质量、时序、功耗、热管理、测试性等多个方面,以实现高效、可靠的FPGA设计。在实际操作中,可以利用FPGA厂商提供的工具进行自动管脚分配,但理解这些因素有助于更好地优化和调整自动分配的结果。

FPGA管脚分配需要考虑的因素.rar (1个子文件)

FPGA管脚分配需要考虑的因素.rar (1个子文件)  FPGA管脚分配需要考虑的因素.pdf 41KB

FPGA管脚分配需要考虑的因素.pdf 41KB- 1

- 粉丝: 81

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 用于将 Python 计算转换为渲染的乳胶的 Python 库 .zip

- 用于实现推荐系统的 Python 库.zip

- 用于实施无服务器最佳实践并提高开发人员速度的开发人员工具包 .zip

- 用于地理数据的 Python 工具.zip

- 全国大学生FPGA创新设计竞赛作品 泡罩包装药品质量在线检测平台.zip

- 带条码打印的固定资产管理系统源码.zip

- 数据采集与分析课程设计.zip

- 基于django的音乐推荐系统.zip

- 用于在 AWS Lambda 中开发和部署无服务器 Python 代码的工具包 .zip

- 基于Spring Boot + MySQL + Redis + RabbitMQ开发的秒杀系统.zip

信息提交成功

信息提交成功

评论0