1

ispLEVER 使用指南

(Lattice FPGA 部分)

2

1.介绍

1.1 简介

该使用指南适用于初次使用 ispLEVER 软件或者不常使用该软件的工程设计人员,它可以帮助你去了解

不同的处理过程,使用各种工具,以及熟悉 ispLEVER 产生的各种报告。在进行下一步时,可以准备一

个设计,以此去了解设计的仿真,功耗的计算,静态时序分析,以及以时序驱动的布局和布线,检查由

软件输出的报告等。以此设计为例,你可以练习约束设计的输入,输出信号以及这些信号管脚的分配去

满足系统要求。也可以修改约束条件,达到最佳地利用 LatticeEC 的结构和资源,同时实现高性能。该

使用指南覆盖了绝大部分通常的流程和软件选项,那些更大的,时序要求更严的设计则需要更精细的控

制才能满足你对性能和资源利用率要求的目标,在此之前,你必须对这些基本知识有所了解和掌握。

1.2 目标

当你读完该使用指南时,你有能力完成以下的任务:

1. 使用 ispLEVER 软件创建一个新的 Verilog 语言的工程目录,选定你的目标器件,并利用 Project

Navigator 在该工程目录中添加 Verilog HDL 源代码。

2. 生成一个 sysCLOCK 锁相环(PLL)模块,并把它添加到该工程项目,利用 IPexpress 和文本编

译器(Text Editor)将该 PLL 模块添加到源代码中。

3. 在器件的管脚上锁定相应的信号,用 Design Planner 定义信号的频率周期和时钟到输出(Clock-

to-out)的时间。

4. 利用映射(Mapping),布局(Placing),布线(Routing)等工具来完成设计。同时,利用

Project Navigator 检查结果报告。

5. 了解静态时序分析报告,调整设计去满足设计的时序要求。

6. 修改和重新设置约束条件去满足设计的性能要求。

7. 使用 Design Planner 来检查器件的实现情况,以及相应的布线阻塞情况,可编程单元(PFU)的

利用率。

8. 使用 Power Calculator 工具来评估器件的功耗情况。

9. 使用工具对设计进行仿真。

1.3 对所用设计例子的说明

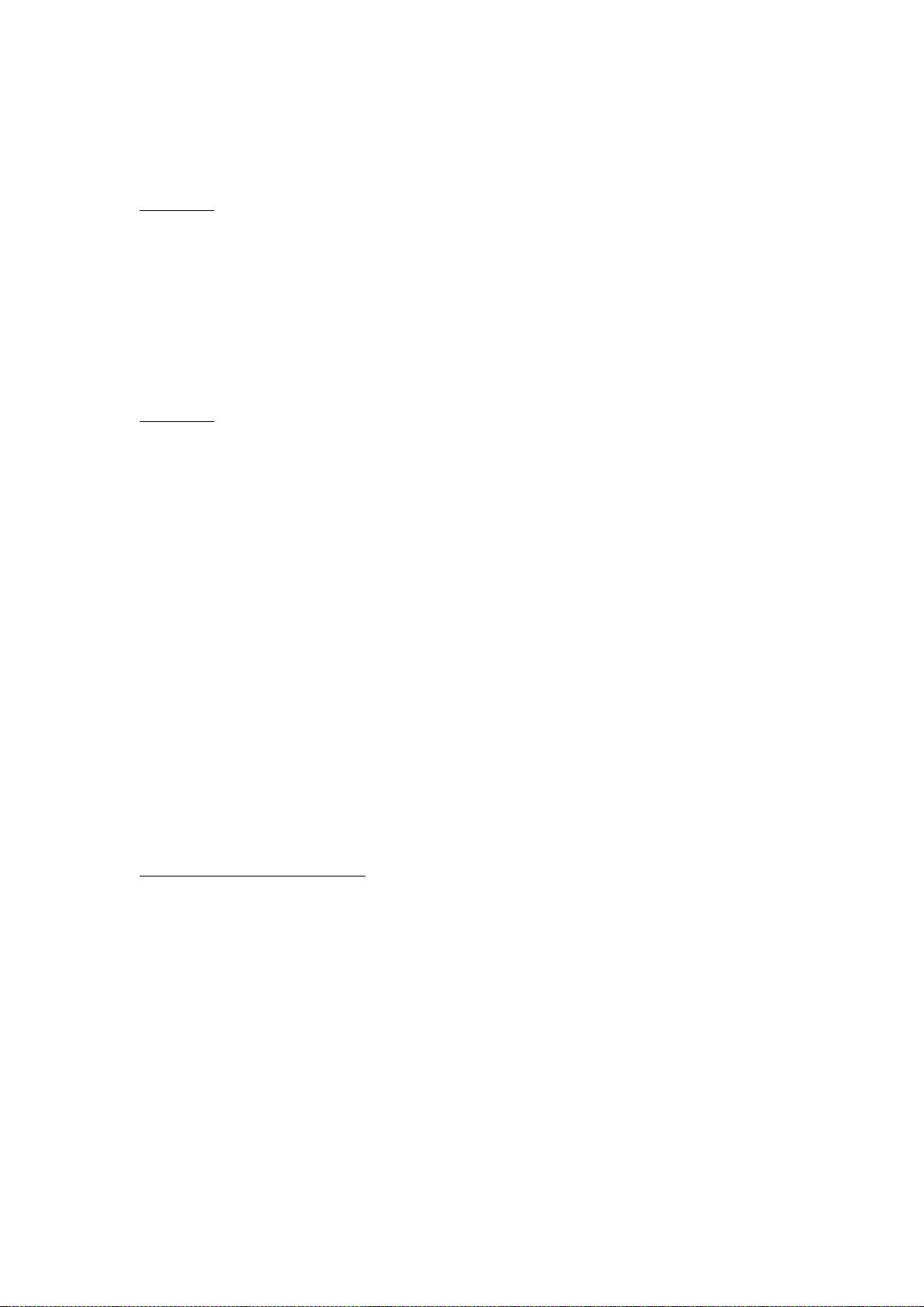

该指南所选用的例子是一个简单的计数器(Counter),用 Verilog 语言来设计。它可以演变成为更复

杂的设计,其中用到寄存器输出,一个 PLL 来协调 FPGA 内部的时序与外部的时序要求。通过修改约束

条件来解决器件的 Fmax 切换特性。sysCLOCK PLL 用来平衡内部反馈补偿,其目的是为了减少时钟

到输出的时延,即Tco的时间。

整个设计由俩部分组成,一个是带有低电平异步清零的 16Bit 计数器和另外一个是 PLL。下面的图说明

了设计A到C的不同实现方法和由此带来的不同时序特性。计数器是由才来完成的,结构化的模块是由

称之为 IPexpress 的工具来实现的,该模块为PLL模块。在设计A和B中,计数器的时钟由外部管脚

提供的,为250MHz。 在设计C中,计数器的时钟由内部PLL提供。sysCLOCK PLL 的引入

有效的去除了由内部时钟网络引起的布线时延,这样可以在PCB设计时更容易进行时序的分析。

3

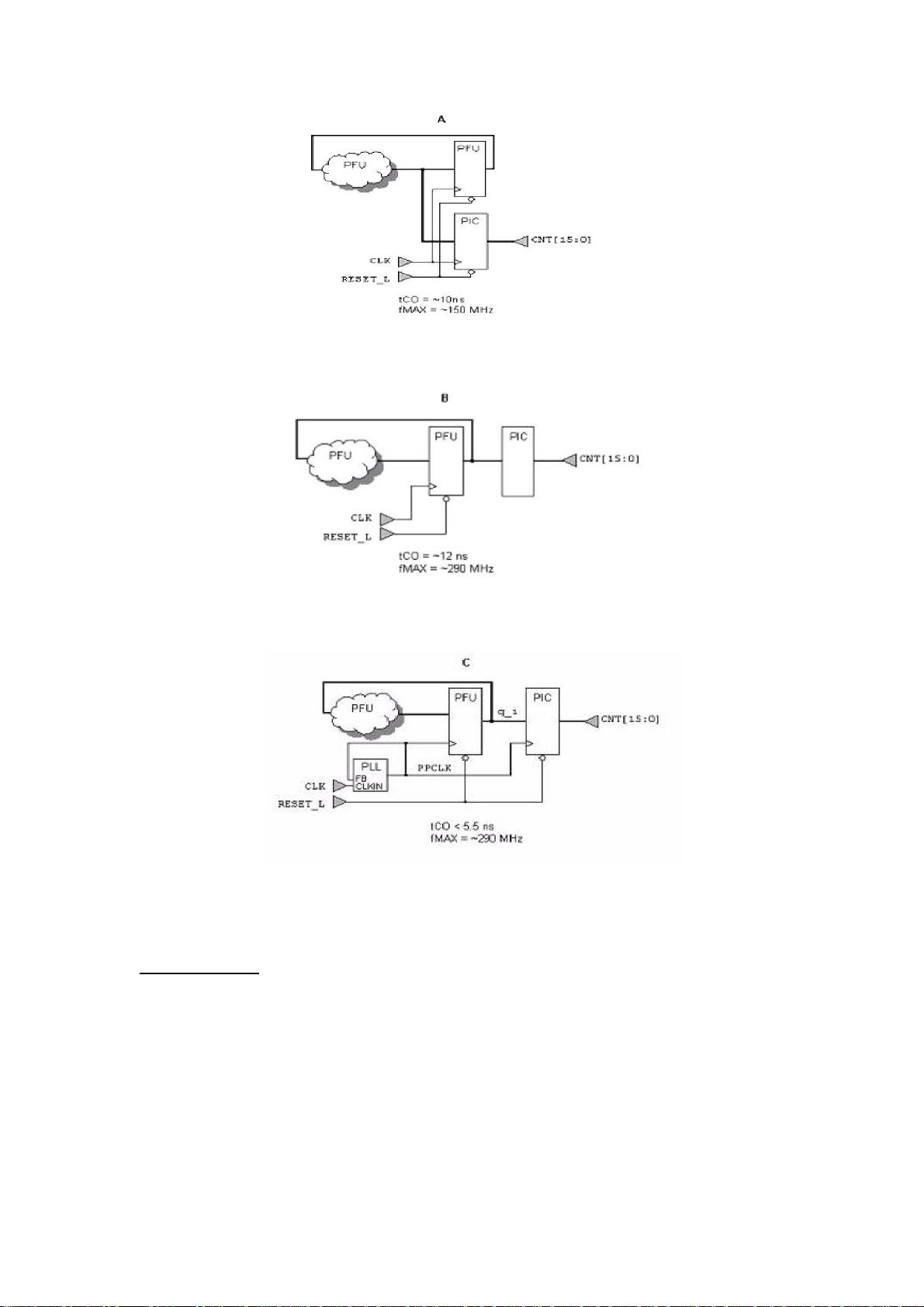

1.4 设计流程

ispLEVER 的 Project Navigator 有几个关键的处理,它们用来把 Verilog 源代码转化成 Lattice 的数

据库,ispLEVER 软件利用这些数据库进行分析和实现设计者的逻辑。以下的流程图阐明这些数据在软

件中的流程。

4

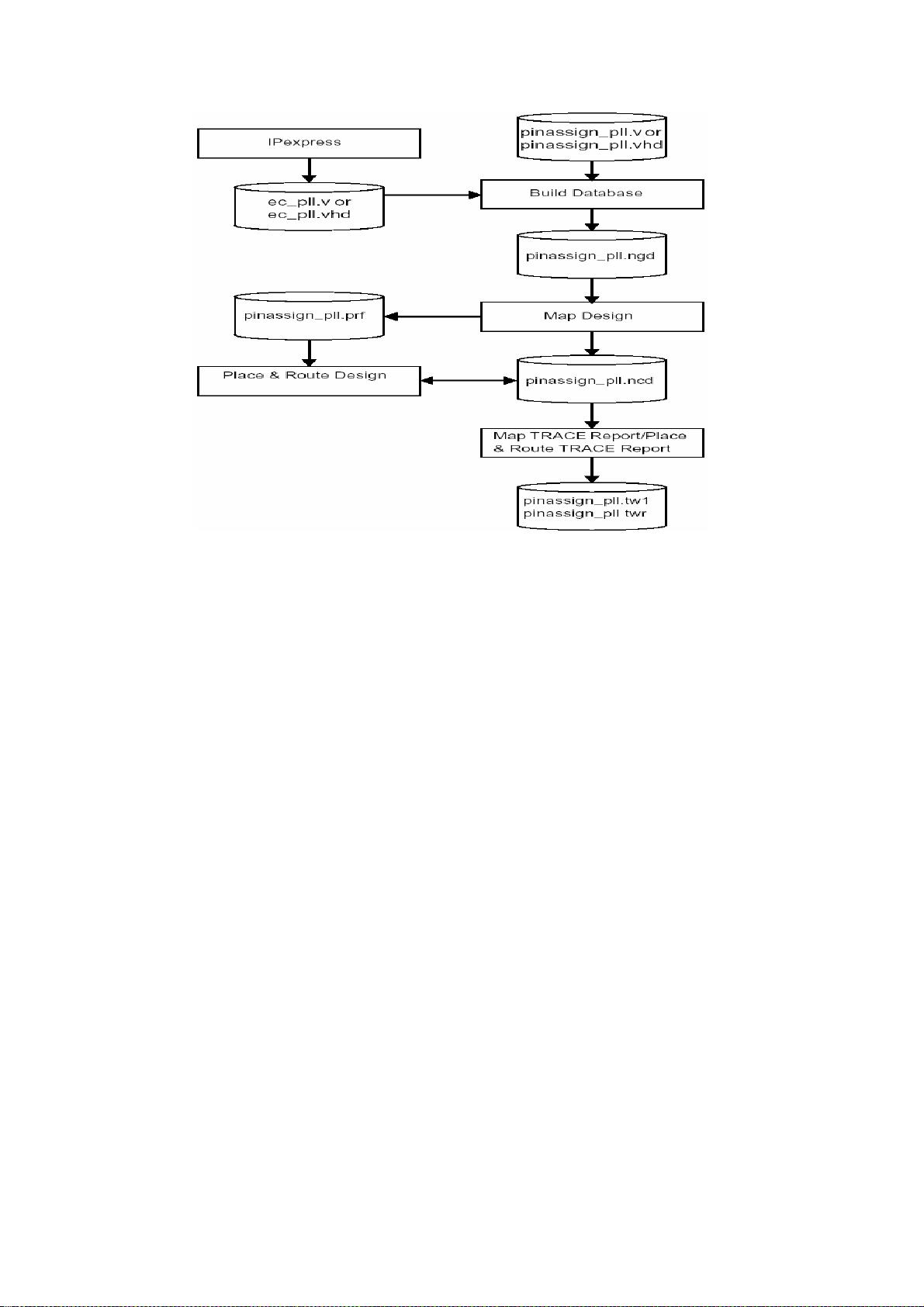

2.练习1:创建新的工程项目

在任务1,你首先要使用 Project Navigator 建立一个新的基于 Verilog 的工程目录,并且给它定义一

个名字。在开始创建一个新的工程时,你应给工程文件(.syn)一个命名,还要申明该工程的类型。

ispLEVER 软件将这些起始的信息存放在你所指定目录的以.syn 为后缀的工程文件之中。一般来说,所

有产生的文件都会存放在该指定的目录当中,但是,你也可以从该指定的目录以外提取源代码。工程的

类型决定了所有代码都必须是相同的类型。比如,该工程类型是 Verilog 的,从其他子目录提取的源代

码也必须是 Verilog 类型的。

建立一个新的工程:

1. 如果没有启动 ispLEVER 软件,开始运行 ispLEVER 软件。

2. 在 Project Navigator 中,选择 File -> New Project 打开工程导向对话框。

3. 在工程导向对话框中,选择或设定以下内容:

在 Project Name 对话框中,键盘输入工程的名字,例如:pinassign_PLL。

在 Location 对话框中,定义你所想要指定目录路径。例如:

<install_path>\examples\tutorial\fpga_design_tutor

在 Design Entry Type 对话框中,选择你想要的源代码类型。例如:Verilog HDL.

在 Synthesis Tool 对话框中,选择你常用的综合工具。例如:Synplify

在 Simulatior 对话框,选择仿真工具

按下一步。

5

4. 在工程导向(Project Wizard)对话框中,选择器件对话框,作以下几步:

在 Family 对话框中,选择你的目标系列。例如:LatticeEC 。

在 Device 对话框中,选择想要使用的器件。例如:LFEC1E 。

在 Speed 速度等级对话框中,选择芯片的速度等级。例如: -3。

在 Package 封装对话框中,选择芯片的封装。例如:TQFP100。

在 Operating Condition 框,选择 Commercial。

按下一步,进入工程导向对话框(Project Wizard),加入源代码对话框。