xilinx_ISE_9.1_cn.rar_ISE_ISE 9.1 _xilinx ISE9.1_xilinx_ISE_9.1_

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

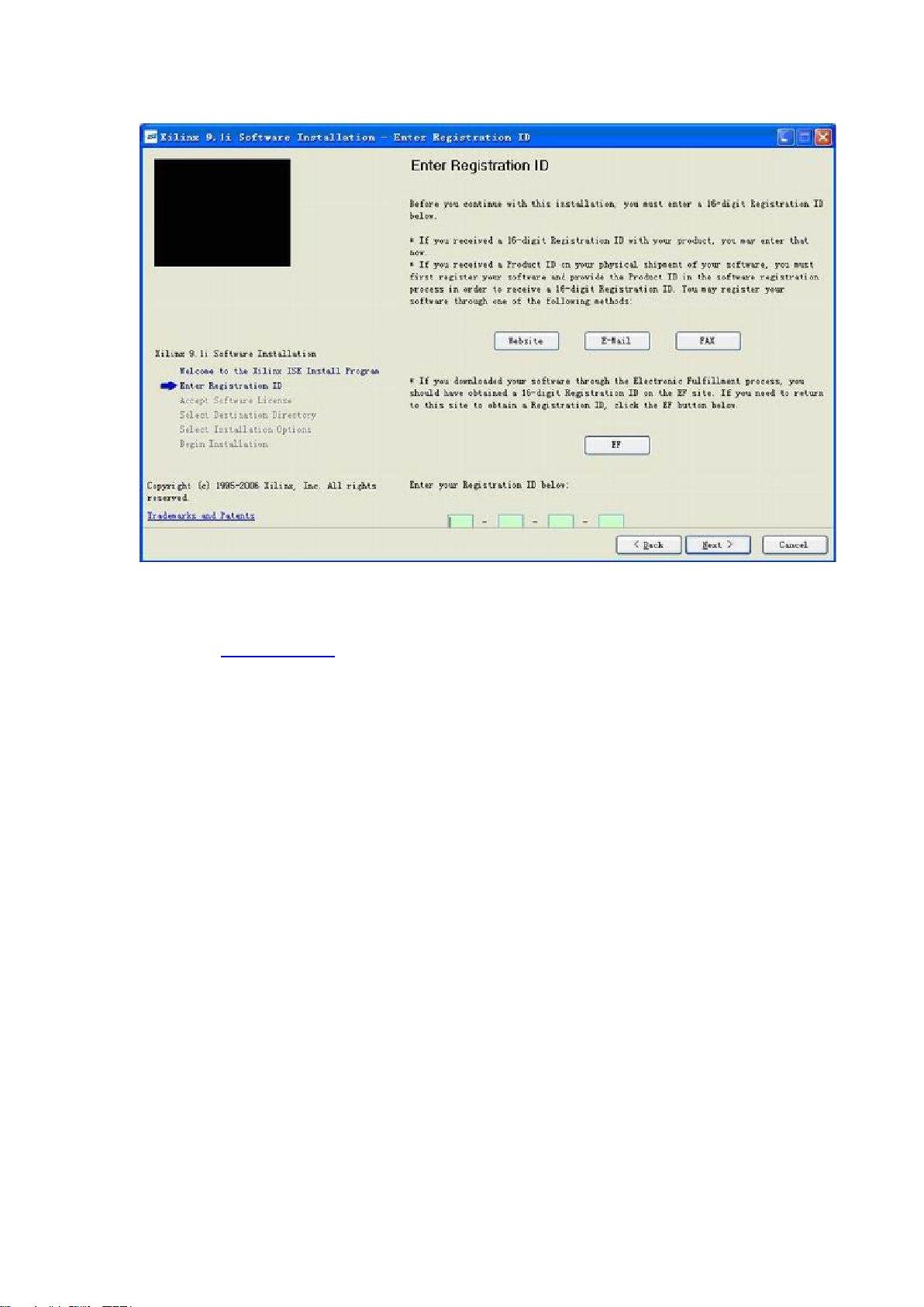

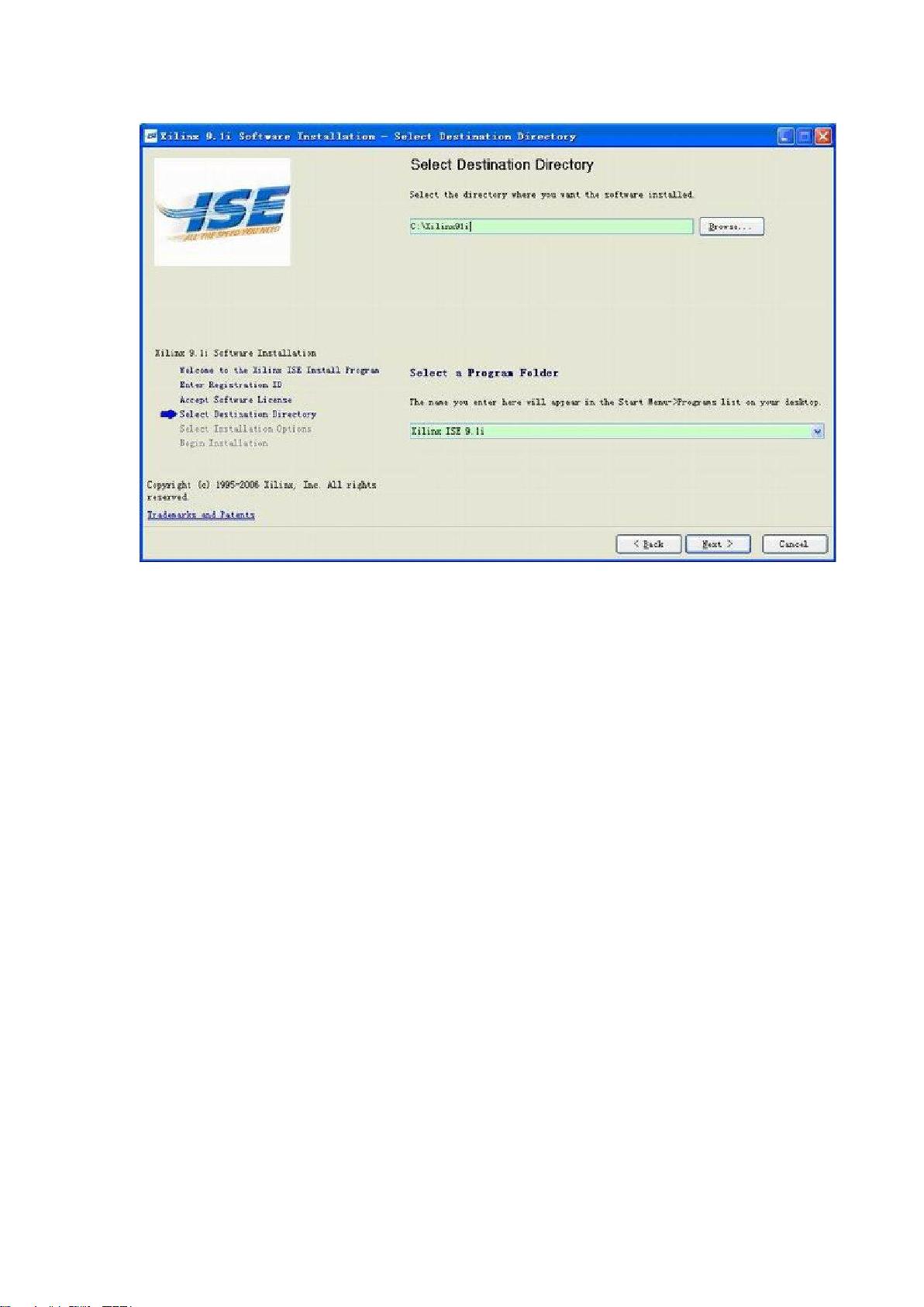

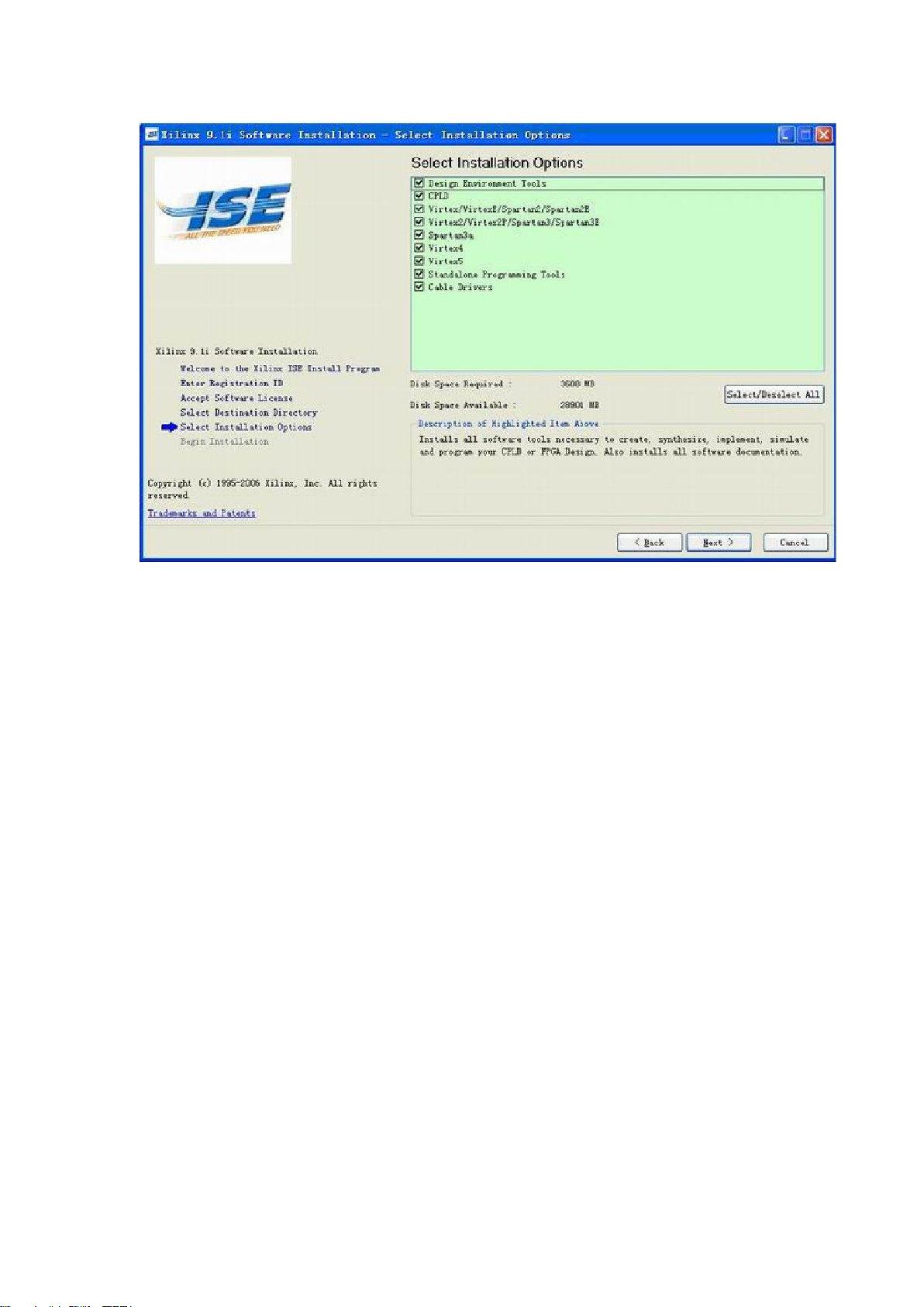

《Xilinx ISE 9.1:仿真工具的深度解析》 Xilinx ISE(Integrated Software Environment)是一款由Xilinx公司推出的综合设计环境,专为FPGA(Field Programmable Gate Array)和CPLD(Complex Programmable Logic Device)的设计、仿真、实现与编程提供了一站式的解决方案。本教程聚焦于ISE 9.1版本,该版本在当时具有广泛的应用,尤其对于初学者和专业工程师来说,是一份极其重要的参考资料。 ISE 9.1包含了众多功能强大的工具,如Synplify Pro用于逻辑综合,XST用于硬件描述语言(HDL)到门级网表的转化,NgDBuild和Map用于布局布线,Par则负责时序优化,而Bitgen则用于生成最终的配置文件。这些工具协同工作,使得设计流程高效且精确。 在仿真工具方面,ISE 9.1提供了ISim,这是一个功能全面的电路仿真器,支持VHDL和Verilog HDL。ISim允许设计师在设计的早期阶段进行行为级和门级仿真,确保设计的功能正确性。用户可以创建测试平台,输入激励,观察输出响应,以验证设计是否满足预期。此外,ISim还支持波形查看器,便于分析仿真结果,定位并解决问题。 在实际应用中,Xilinx ISE 9.1的使用步骤通常包括以下几个关键环节: 1. **设计输入**:使用VHDL或Verilog HDL编写设计代码,或者导入第三方IP核。 2. **综合**:通过Synplify Pro或其他综合工具,将设计代码转化为逻辑网表,这个过程会考虑时序约束,优化逻辑结构。 3. **映射**:XST将网表映射到特定的FPGA架构,分配逻辑资源,包括查找表、触发器和连线。 4. **布局布线**:NgDBuild和Map进行物理布局和布线,以满足速度、面积和功耗的要求。 5. **时序优化**:Par进行时序优化,以达到设计的时序目标。 6. **生成配置文件**:Bitgen根据前面的步骤生成配置文件,用于加载到目标FPGA上。 7. **仿真验证**:在整个设计流程中,ISim扮演着关键角色,它可以在每个阶段进行仿真,确保设计的正确性。 《Xilinx ISE 9.1中文教程.pdf》作为一份详尽的指南,将涵盖这些步骤,并深入讲解每个工具的用法和技巧,帮助用户更好地理解和掌握ISE 9.1。无论你是新手还是有经验的工程师,这份教程都将是你探索FPGA设计世界的一把钥匙,带你领略到数字电路设计的魅力和无限可能。通过深入学习和实践,你将能够自如地运用Xilinx ISE 9.1,创造出自己的独特设计,满足各类应用的需求。

xilinx_ISE_9.1_cn.rar (1个子文件)

xilinx_ISE_9.1_cn.rar (1个子文件)  xilinx_ISE_9.1中文教程.pdf 9MB

xilinx_ISE_9.1中文教程.pdf 9MB- 1

- 粉丝: 78

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论0