D.Module.C6713

• Board Revision 2.0

Technical Data Sheet

Document Revision 1.2 Mar. 2009

D.SignT

Digital Signalprocessing Technology

DSP

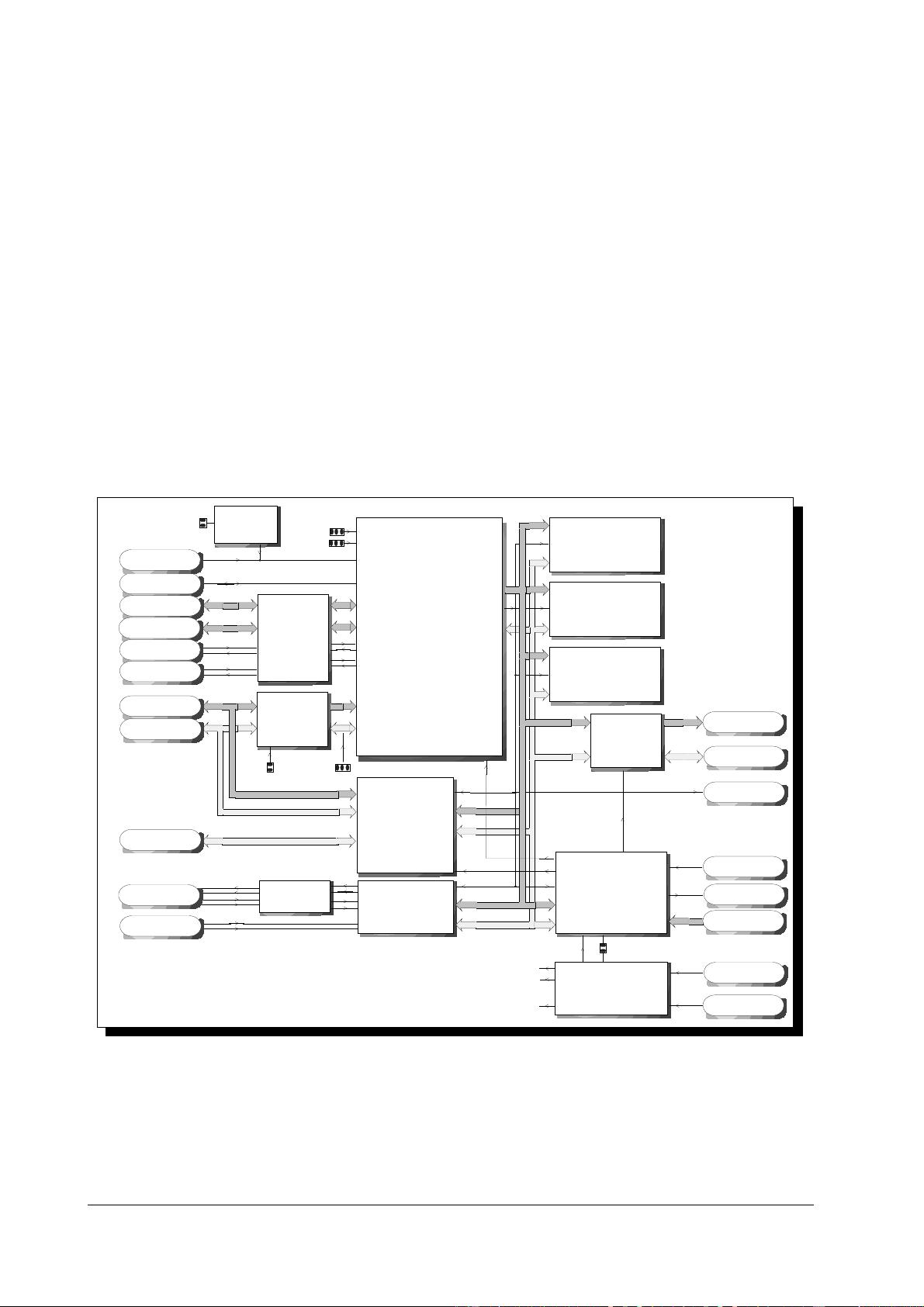

The heart of the D.Module.C6713 is the advanced

VLIW architecture floating point digital signal pro-

cessor TMS320C6713 from Texas Instruments. This

RISC architecture DSP provides 8 instruction units

which operate in parallel, yielding a maximum per-

formance of 2400 MIPS, 1800 MFLOPS. Up to 256

Kbytes internal memory and a two level cache ar-

chitecture (64 Kbytes L2 cache, 4 Kbytes L1 pro-

gram cache and 4 Kbytes L1 data cache) guarantee

the memory bandwidth required to sustain high data

throughput. Furthermore, two multichannel buffered

synchronous serial ports, an I2C bus interface, two

timers, an enhanced DMA controller and a 16 bit

wide Host Interface are built into this processor.

The multichannel buffered serial ports provide a

direct connection to T1/E1, SCSA, MVIP, AC-97,

ST-Bus and SPI interfaces, and industry standard

Codecs, A/D and D/A converters. High Speed data

transfer up to 75 MBits/sec is possible. This also

provides an efficient data path for multiprocessor

communications.

The built-in DMA controller provides enhanced

features for 1D and 2D transfers and auto-initializa-

tion, which allows to maintain circular and ping-

pong buffers without any CPU intervention.

MEMORY

The DSP itself provides up to 256 Kbytes internal

memory, usable as program and/or data memory.

64 Kbytes of this memory area can be configured

as a 4-way second level cache to increase through-

put if large data structures or program code reside

in external memory.

The 512 Kbytes synchronous SRAM operate at

100 MHz clock speed providing single cycle access.

The SBSRAM supports Byte, Halfword and Word

data formats. It can be used as program and data

memory.

Additionally 32 Mbytes on-board SDRAM can be

used for large data buffers as commonly required

by image processing applications. Byte, Halfword

and Word data is supported. SDRAM also operates

at 100 MHz.

Two Mbytes Flash Memory are integrated for non-

volatile data and program storage. The Flash

Memory is divided in multiple sectors of 64 Kbytes.

Each sector can be erased individually and (re-)pro-

grammed on a Byte basis. The DSP has direct ac-

cess to the Flash Memory: Identification, Sector-

Erase and Programming is handled by BIOS func-

tions which effectively encapsulate the program-

ming algorithms.

Further external memory expansion is possible

using the two pre-decoded select signals. The

IOSEL and MEMSEL memory ranges are primarily

intended to connect parallel interface data acquisi-

tion and communication devices, but can be used

for memory expansion too: IOSEL only supports

asynchronous devices, but MEMSEL also supports

external SDRAM expansions.

CLOCKS

An on board oscillator generates the DSP master

clock. Additional clocks for external peripherals can

be generated using the two 32 bit timers. The Serial

Ports feature their own clock generation circuitry

based on the DSP clock or an external master

clock.

POWER SUPPLY

The D.Module.C6713 requires a 3.3V single

voltage power supply only. Secondary voltages for

RS232 and CPU core are generated on board using

PWM regulators and charge pumps. A micro-pro-

cessor supervisor circuit controls the power supply

sequencing and holds the board in reset if the sup-

ply voltage is below it's limit.

EXTERNAL BUS INTERFACE

The external bus interface is fully 5V tolerant to

support a direct connection to 5V environments.

The data bus is 32 bit wide, 20 address lines and

four byte select outputs provide access to a linear

256 Mbytes address range (MEMSEL) and a 1

Mbyte linear address range for I/O expansion

(IOSEL). The bus interface timing is independently

programmable for both memory areas. Peripherals

connected to the external bus interface can request

additional wait states or delay a bus cycle using the

nWAIT input. The minimum I/O cycle time is 20

nsecs.

UART

The UART offers powerful features: 32 word re-

ceive and transmit FIFOs, automatic flow control

(RTS/CTS and Xon/Xoff), and DMA support relieve

the DSP from time-consuming interrupt driven data

transfers. Baud rates up to 460 kBaud are possible.

The line interface is RS232, optionally RS422/485 is

available. The onboard wait state logic generates

the required wait states for UART accesses while

D.SignT 2003 Doc #1.2 2