Q162 HMC830锁相环设计.rar_HMC830_hmc830电路_hmc830锁相环设计图_锁相_锁相环

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

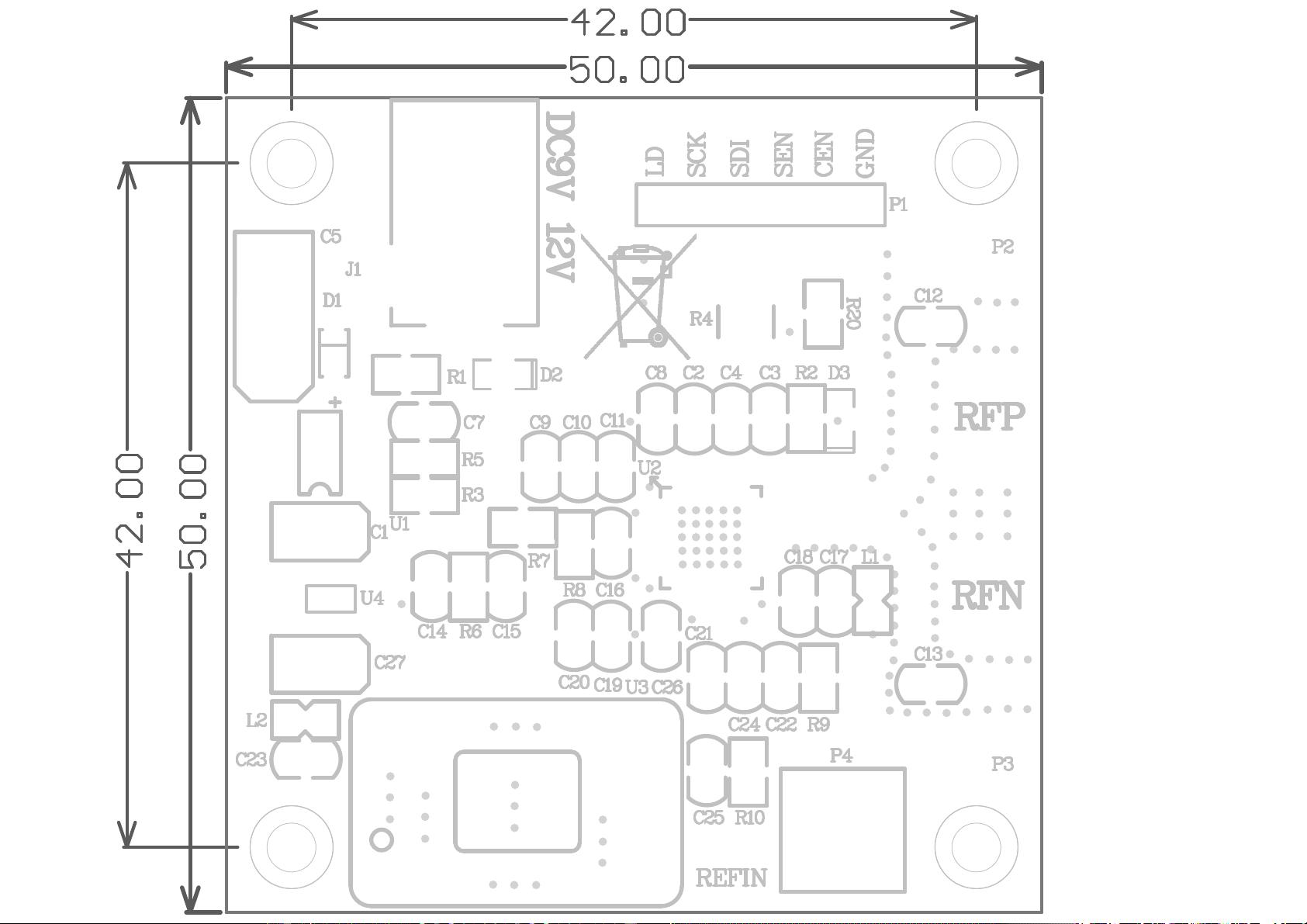

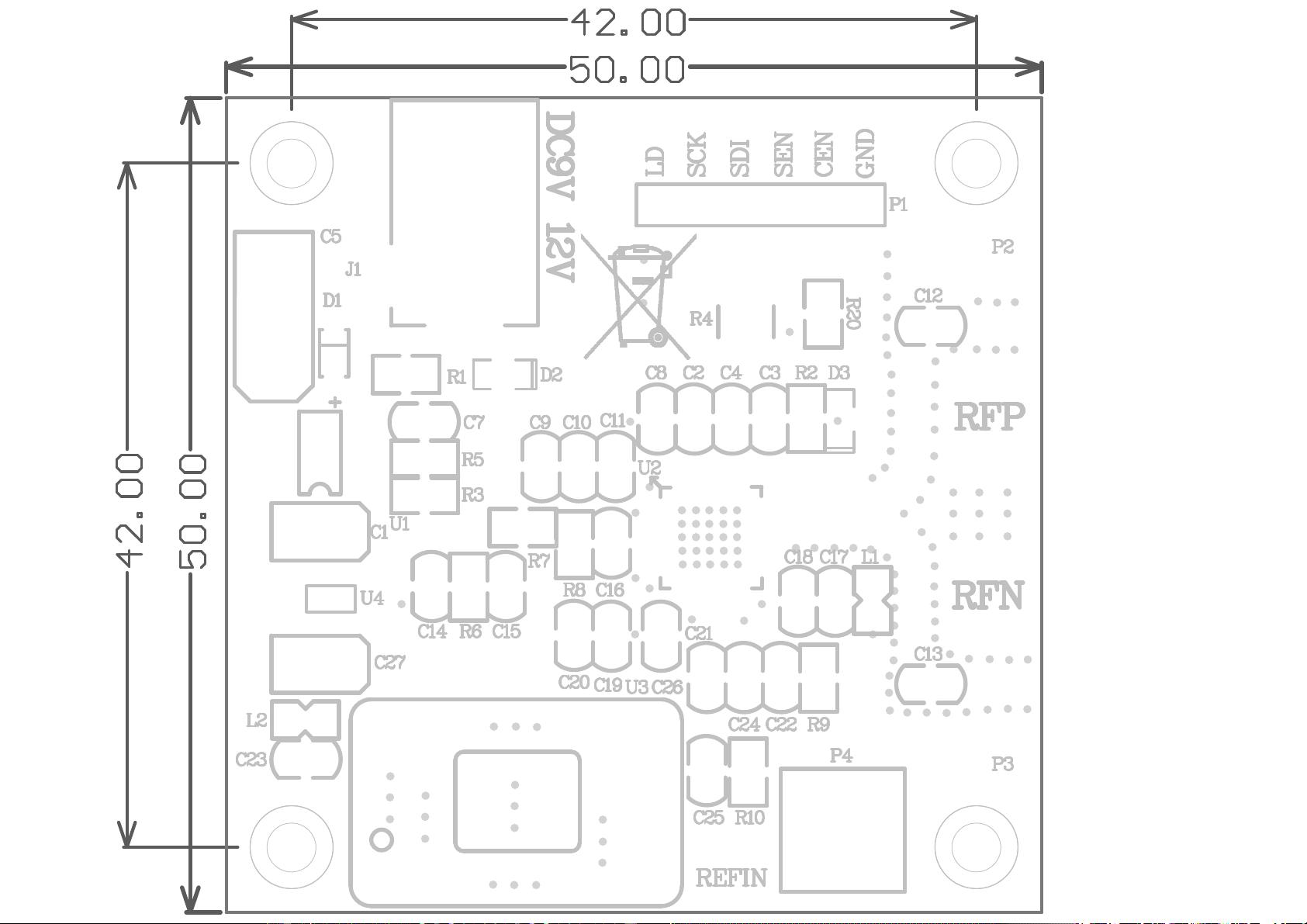

《HMC830锁相环设计详解》 在现代通信系统中,锁相环(PLL,Phase-Locked Loop)是一种关键的频率合成与相位同步技术,它广泛应用于频率控制、信号调制解调、时钟恢复等领域。HMC830是一款高性能的锁相环集成电路,由Analog Devices公司生产,特别适用于射频(RF)和微波系统的应用。本文将深入探讨HMC830锁相环的设计原理,并结合提供的设计图进行详细解析。 一、HMC830概述 HMC830是一款单芯片、宽带、低噪声、高线性度的电压控制振荡器(VCO)锁相环,工作频率范围宽,可覆盖从2.5 GHz到7 GHz。它集成了压控振荡器、分频器、鉴相器和低噪声环路滤波器,具有高稳定性和良好的频率调谐特性,使得设计者能够轻松实现精确的频率合成。 二、锁相环基本原理 锁相环的工作原理是通过比较输入参考信号和VCO输出信号之间的相位差,然后调整VCO的频率,使其与参考信号保持恒定的相位关系。鉴相器将相位差转换为电压信号,经过环路滤波器后,该电压被用于驱动VCO,从而形成一个负反馈闭环控制系统。 三、HMC830锁相环设计关键环节 1. 压控振荡器(VCO):HMC830内置的VCO具有宽调谐范围和低相位噪声,通过改变输入的控制电压,可以实现频率的线性调整。 2. 分频器:根据设计需求,可以选择适当的分频系数,将VCO输出的高频信号降低到鉴相器可以处理的频率范围。 3. 鉴相器:鉴相器负责比较参考信号和VCO输出信号的相位,产生误差电压。 4. 环路滤波器:环路滤波器的作用是平滑鉴相器产生的误差电压,消除高频噪声,确保环路的稳定性。 四、HMC830锁相环设计图分析 在提供的PDF文件中,我们可以看到HMC830锁相环的具体电路配置和参数设置。设计图包括了VCO输入电压控制网络、分频器选择、鉴相器电路以及环路滤波器的详细连接方式。通过分析这些电路,设计者可以了解如何根据具体应用需求调整环路增益、环路带宽以及噪声性能。 五、锁相环应用实例 HMC830常用于射频接收机的本振(Local Oscillator)生成、频率合成器、频率倍增器和时钟恢复系统。例如,在无线通信基站中,锁相环可以用来产生精确的载波频率,确保信号的准确传输。 六、总结 HMC830锁相环凭借其宽频带、高线性度和集成化的特性,为设计者提供了灵活的频率合成解决方案。理解并掌握HMC830锁相环的设计原理和电路配置,对于实现高性能的射频和微波系统至关重要。通过分析设计图,我们可以深入理解每个组件的作用,以及它们如何协同工作以实现锁相环的功能。对于希望深入研究或实际操作的工程师来说,这份资料无疑是一份宝贵的参考资料。

Q162 HMC830锁相环设计.rar (1个子文件)

Q162 HMC830锁相环设计.rar (1个子文件)  Q162 HMC830锁相环设计.pdf 192KB

Q162 HMC830锁相环设计.pdf 192KB- 1

- 粉丝: 79

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Java开发的简洁方便ORM工具BeetlSQL设计源码

- 基于Java语言的Reactor-QL:用SQL简化Reactor API实时数据处理设计源码

- 基于Java的tio-http-server演示学习源码

- 基于Java和C#的C#课程实验与Winform学习及Android实验设计源码

- 基于Java的电厂职工管理系统设计源码

- 基于Python的RSA+AES加密的SecureHTTP设计源码

- 基于Java平台的集成nsg-dao设计源码,涵盖jdbc、hibernate、mybatis框架

- 基于Vue的Java+JavaScript+CSS+HTML搭建的二手交易平台设计源码

- 基于Java和Vue的Spring Boot博客系统设计源码

- 基于MS51单片机的eeprom32与sst39vf040存储器读写设计源码

信息提交成功

信息提交成功

评论2