关于 ALU 处理单元的构建

我们采用自下而上的设计方法:

首先考虑 1 位的 ALU,

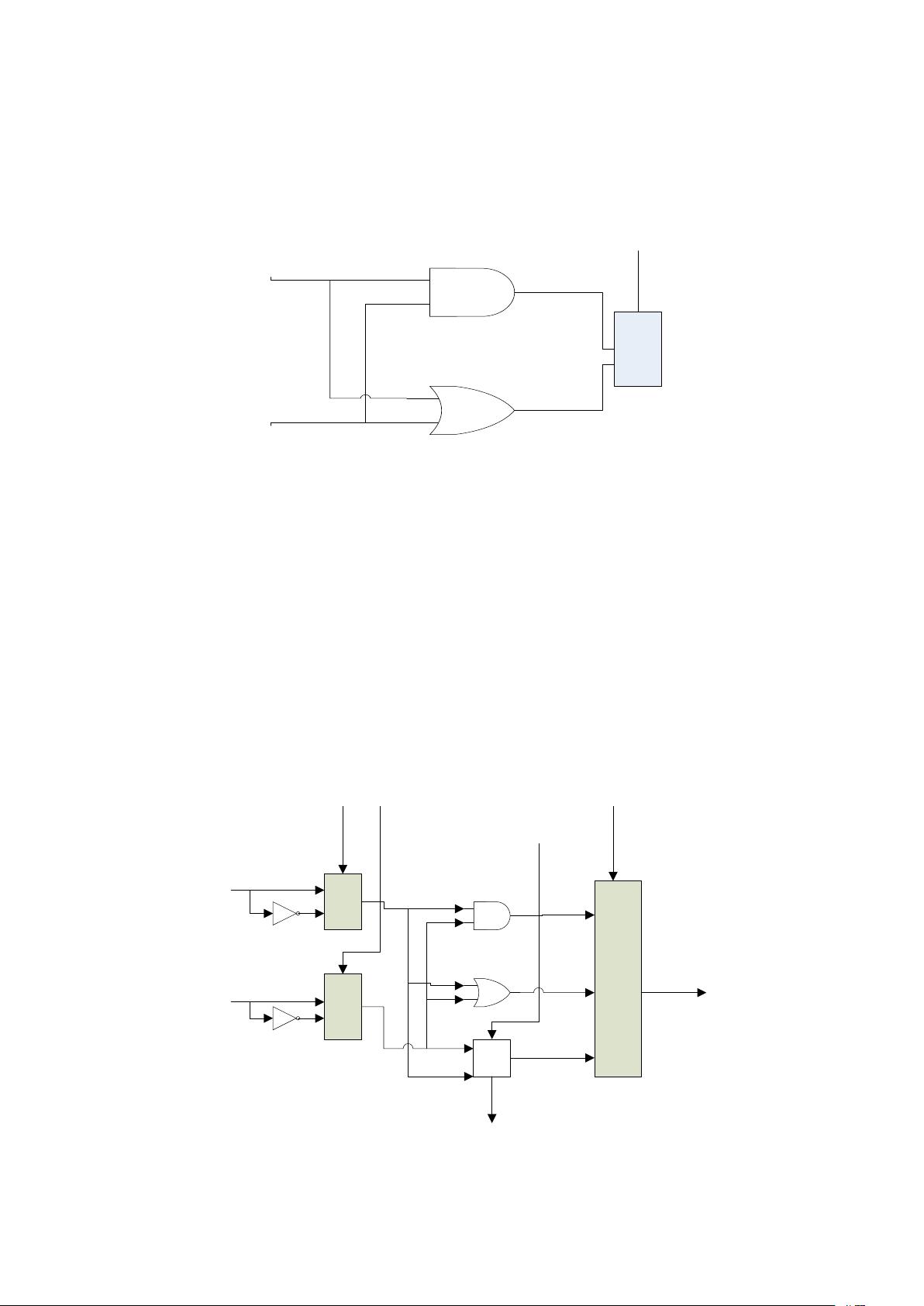

逻辑操作最简单,因为它们可以直接映射到如果所示的硬件组件:

a

b

操作数

0

1

其中右边是一个二选一的选择器(mutex)。

ALU 的下一个功能是加法器。加法器必须有两个操作数输入以及一个和的 1 位输出,这里还

必须有第二个输出用于进位,成为进位输出,相应的还要有进位输入。

根据加法的真值表达式,我们可以得到:

CarryOut

=

a

⋅

b

+

a

∙

CarryIn

+

b

∙

CarryIn

Sum

=

(

a

∙

∼

b

∙

∼

CarryIn

)

+

(

∼

a

∙

b

∙

∼

CarryIn

)

+

(

∼

a

∙

∼

b

∙

CarrIn

)

+

(𝑎

∙

𝑏

∙

𝐶𝑎𝑟𝑟𝑦𝐼𝑛)

于是,加法操作完成,减法相当于加一个操作数的负数,就这样我们就可以用加法器执行减

法。二进制补码取负的方法就是取反加 1,于是 b 输入也需要用一个 mutex,通过选择信号

判断是 b 还是 b 的取反。巧合的是,只要我们将仅为输入 CarryIn 设置为 1,这样就实现了

减法!

为了扩展运算,我们预先也加入关于 a 和 a 的取反的 mutex。于是有了这样的设计图:

+

0

1

2

a

b

CarryOut

CarryIn

Ainvert Binvert

操作数

结果