1

PCI Express

®

Card Electromechanical

Specification

Revision 3.0

July 21, 2013

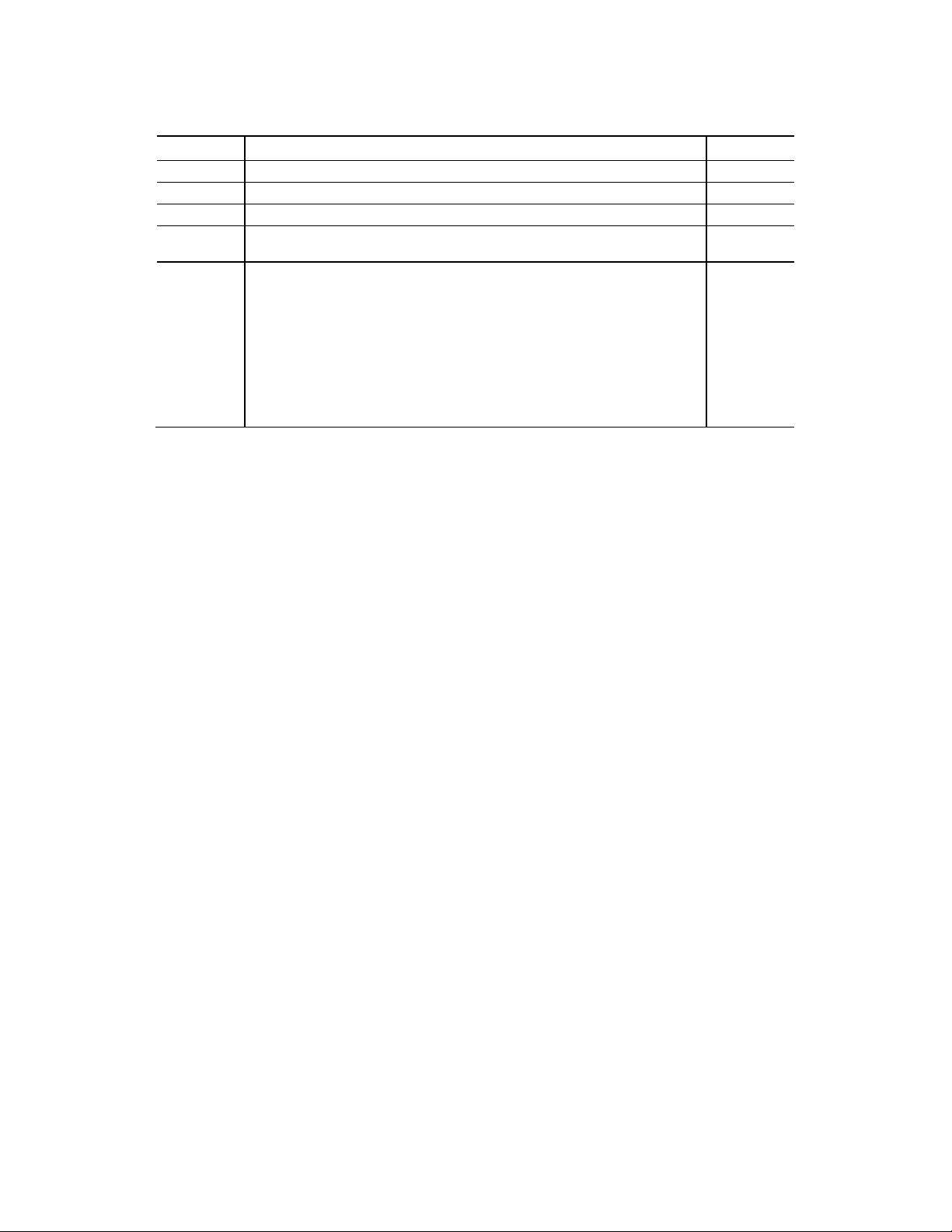

Revision

Revision History

Date

1.0 Initial release. 7/22/2002

1.0a Incorporated WG Errata C1-C7 and E1. 4/15/2003

1.1 Incorporated approved Errata and ECNs. 3/28/2005

2.0 Added support for 5.0 GT/s data rate. 4/11/2007

3.0

• Added support for 8.0 GT/s data rate and incorporated approved Errata and

ECNs. Incorporated the PCI Express x16 Graphics 150W-ATX Specification

and the PCI Express 225 W/300 W High Power Card Electromechanical

Specification.

• Re-imported all figures

• Updated Figure 6-1 and Figure 6-3

• Fixed text notes in Chapter 6 and 9 Figures (took notes out of Illustrator and

made them part of the Word file)

• Changed 306.67 MAX dimension to 326.03 MIN in Figure 9-3

7/21/2013

3

Contents

1. INTRODUCTION..................................................................................................................11

1.1. TERMS AND DEFINITIONS ................................................................................................... 12

1.2. REFERENCE DOCUMENTS ................................................................................................... 13

1.3. SPECIFICATION CONTENTS ................................................................................................. 14

1.4. OBJECTIVES............................................................................................................................. 14

1.5. ELECTRICAL OVERVIEW ..................................................................................................... 15

1.6. MECHANICAL OVERVIEW ................................................................................................... 16

1.7. 150 W OVERVIEW ................................................................................................................... 18

1.8. 225 W AND 300 W ADD-IN CARD OVERVIEW .................................................................. 19

1.9. SYSTEM POWER DELIVERY REQUIREMENTS ................................................................. 20

2. AUXILIARY SIGNALS ........................................................................................................21

2.1. REFERENCE CLOCK ............................................................................................................... 22

2.1.1. Low Voltage Swing, Differential Clocks .................................................................... 22

2.1.2. Spread Spectrum Clocking (SSC) ............................................................................... 23

2.1.3. REFCLK AC Specifications........................................................................................ 24

2.1.4. REFCLK Phase Jitter Specification for 2.5 GT/s Signaling Support ......................... 28

2.1.5. REFCLK Phase Jitter Specification for 5.0 GT/s Signaling Support ......................... 29

2.1.6. REFCLK Phase Jitter Specification for 8.0 GT/s Signaling Support ......................... 29

2.2. PERST# SIGNAL ...................................................................................................................... 29

2.2.1. Initial Power-Up (G3 to S0) ....................................................................................... 30

2.2.2. Power Management States (S0 to S3/S4 to S0) .......................................................... 30

2.2.3. Power Down ............................................................................................................... 32

2.3. WAKE# SIGNAL ...................................................................................................................... 33

2.4. SMBUS (OPTIONAL) ............................................................................................................... 37

2.4.1. Capacitive Load of High-power SMBus Lines ........................................................... 37

2.4.2. Minimum Current Sinking Requirements for SMBus Devices.................................... 37

2.4.3. SMBus “Back Powering” Considerations ................................................................. 37

2.4.4. Power-on Reset .......................................................................................................... 38

2.5. JTAG PINS (OPTIONAL) ......................................................................................................... 38

2.6. AUXILIARY SIGNAL PARAMETRIC SPECIFICATIONS ................................................... 39

2.6.1. DC Specifications ....................................................................................................... 39

2.6.2. AC Specifications ....................................................................................................... 40

3. HOT INSERTION AND REMOVAL ..................................................................................41

3.1. SCOPE 41

3.2. PRESENCE DETECT ................................................................................................................ 41

4. ELECTRICAL REQUIREMENTS .....................................................................................43

4.1. POWER SUPPLY REQUIREMENTS ...................................................................................... 43

4.2. POWER CONSUMPTION ........................................................................................................ 45

4.3. POWER BUDGETING CAPABILITY ..................................................................................... 46

4.4. POWER SUPPLY SEQUENCING ............................................................................................ 46

4.5. POWER SUPPLY DECOUPLING ............................................................................................ 47

4.6. ELECTRICAL TOPOLOGIES AND LINK DEFINITIONS .................................................... 47

4.6.1. Topologies .................................................................................................................. 47

4.6.2. Link Definition ............................................................................................................ 49

PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 3.0

4

4.7. ELECTRICAL BUDGETS ........................................................................................................ 50

4.7.1. AC Coupling Capacitors ............................................................................................ 51

4.7.2. Insertion Loss Values (Voltage Transfer Function) ................................................... 51

4.7.3. Jitter Values ................................................................................................................ 51

4.7.4. Crosstalk ..................................................................................................................... 53

4.7.5. Lane-to-Lane Skew ..................................................................................................... 54

4.7.6. Transmitter Equalization ............................................................................................ 54

4.7.7. Skew within the Differential Pair ............................................................................... 55

4.7.8. Differential Data Trace Impedance............................................................................ 55

4.7.9. Differential Data Trace Propagation Delay .............................................................. 56

4.8. EYE DIAGRAMS AT THE ADD-IN CARD INTERFACE ..................................................... 56

4.8.1. Add-in Card Transmitter Path Compliance Eye Diagram at 2.5 GT/s ...................... 56

4.8.2. Add-in Card Transmitter Path Compliance Eye Diagrams at 5.0 GT/s .................... 57

4.8.3. Add-in Card Transmitter Path Compliance Eye Diagrams at 8.0 GT/s .................... 59

4.8.4. Add-in Card Minimum Receiver Path Sensitivity Requirements at 2.5 GT/s ............. 60

4.8.5. Add-in Card Minimum Receiver Path Sensitivity Requirements at 5.0 GT/s ............. 61

4.8.6. Add-in Card Minimum Receiver Path Sensitivity Requirements at 8.0 GT/s ............. 62

4.8.7. System Board Transmitter Path Compliance Eye Diagram at 2.5 GT/s .................... 65

4.8.8. System Board Transmitter Path Compliance Eye Diagram at 5.0 GT/s .................... 66

4.8.9. System Board Transmitter Path Compliance Eye Diagram at 8.0 GT/s .................... 69

4.8.10. System Board Minimum Receiver Path Sensitivity Requirements at 2.5 GT/s ........... 72

4.8.11. System Board Minimum Receiver Path Sensitivity Requirements at 5.0 GT/s ........... 73

4.8.12. System Board Minimum Receiver Path Sensitivity Requirements at 8.0 GT/s ........... 75

5. 150 W, 225 W, AND 300 W ADD-IN CARD POWER .......................................................77

5.1. 150 W ADD-IN CARD POWER-UP SEQUENCING .............................................................. 79

5.2. 225 W AND 300 W ADD-IN CARD POWER-UP SEQUENCING ......................................... 81

6. CARD CONNECTOR SPECIFICATION ..........................................................................86

6.1. CONNECTOR PINOUT ............................................................................................................ 86

6.2. CONNECTOR INTERFACE DEFINITIONS ........................................................................... 89

6.3. SIGNAL INTEGRITY REQUIREMENTS AND TEST PROCEDURES ................................ 94

6.3.1. Signal Integrity Requirements .................................................................................... 94

6.3.2. Signal Integrity Requirements and Test Procedures for 2.5 GT/s Support ................ 94

6.3.3. Signal Integrity Requirements and Test Procedures for 5.0 GT/s Support ................ 97

6.3.3.1 Test Fixture Requirements ...................................................................... 99

6.3.4. Signal Integrity Requirements and Test Procedures for 8.0 GT/s Support .............. 100

6.3.4.1 Test Fixture Requirements .................................................................... 101

6.4. CONNECTOR ENVIRONMENTAL AND OTHER REQUIREMENTS .............................. 101

6.4.1. Environmental Requirements ................................................................................... 101

6.4.2. Mechanical Requirements ........................................................................................ 103

6.4.3. Current Rating Requirement .................................................................................... 104

6.4.4. Additional Considerations ........................................................................................ 104

7. PCI EXPRESS 2 X 3 AUXILIARY POWER CONNECTOR DEFINITION ...............106

7.1. 6-POSITION POWER CONNECTOR SYSTEM PERFORMANCE REQUIREMENTS ..... 106

7.2. 6-POSITION PCB HEADER ................................................................................................... 106

7.2.1. 6-Position R/A Thru-Hole PCB Header Assembly ................................................... 106

7.2.2. 6-Position R/A Thru-Hole Header Recommended PCB Footprint .......................... 108

7.2.3. 6-Position R/A SMT PCB Header Assembly ............................................................ 109

7.2.4. R/A SMT Header Recommended PCB Footprint ..................................................... 110

PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 3.0

5

7.3. 6-POSITION CABLE ASSEMBLY ........................................................................................ 111

7.4. CONNECTOR MATING-UNMATING KEEP-OUT AREA (LATCH LOCK RELEASE) .. 112

7.5. 6-POSITION POWER CONNECTOR SYSTEM PIN ASSIGNMENT ................................. 113

7.6. ADDITIONAL CONSIDERATIONS ...................................................................................... 114

8. PCI EXPRESS 2 X 4 AUXILIARY POWER CONNECTOR DEFINITION ...............115

8.1. 2 X 4 AUXILIARY POWER CONNECTOR PERFORMANCE REQUIREMENTS ........... 118

8.2. 2 X 4 RECEPTACLE ............................................................................................................... 118

8.2.1. Connector Drawing .................................................................................................. 118

8.2.2. PCB Footprint .......................................................................................................... 120

8.3. CABLE ASSEMBLY ............................................................................................................... 121

8.4. CONNECTOR MATING-UNMATING KEEP-OUT AREA (LATCH LOCK RELEASE) .. 123

8.5. 2 X 4 AUXILIARY POWER CONNECTOR SYSTEM PIN ASSIGNMENT ....................... 124

8.6. ADDITIONAL CONSIDERATIONS ...................................................................................... 126

9. ADD-IN CARD FORM FACTORS AND IMPLEMENTATION ..................................127

9.1. ADD-IN CARD FORM FACTORS......................................................................................... 127

9.2. CONNECTOR AND ADD-IN CARD LOCATIONS ............................................................. 146

9.3. CARD INTEROPERABILITY ................................................................................................ 155

9.4. 150W-ATX THERMAL MANAGEMENT ............................................................................. 156

10. PCI EXPRESS 225 W/300 W ADD-IN CARD THERMAL AND ACOUSTIC

MANAGEMENT .................................................................................................................157

10.1. INLET TEMPERATURE ........................................................................................................ 157

10.2. CARD THERMAL CHARACTERIZATION PROCEDURE ................................................. 158

10.3. ACOUSTIC MANAGEMENT ................................................................................................ 162

10.3.1. Background and Scope ............................................................................................. 162

10.3.2. Card Acoustic Characterization Procedure ............................................................. 162

10.3.3. Acoustic Recommendations and Guidelines ............................................................. 163

A. INSERTION LOSS VALUES (VOLTAGE TRANSFER FUNCTION)

(INFORMATIONAL ONLY) .............................................................................................164

B. 8.0 GT/S TEST CHANNELS ..............................................................................................167

11. ACKNOWLEDGEMENTS ................................................................................................168

评论0