摘要

本文为数字时钟的设计介绍,具体说明如何使用 QuartusⅡ软件设计一个基

于 EP1C6Q240C8 芯片的数字钟。该数字钟具备以下功能:1.正常计时 2.校

正时间 3.闹铃设置 4.整点报时。

目录

方案分析与对比

本次设计的数字钟功能比较复杂,应分成若干模块分别设计,然后再

整合在一起。现就各模块的功能与总体设计方案进行讨论。

分频部分:由于数字钟计时每秒跳变一次,数码管动态扫描的频率必

须大于 100Hz,闹铃需要 500Hz 和 1000Hz 的频率输入,而限于实验板的

布局,输入的时钟只能有一个。因此,必然要对仅有的一个输入时钟进行

分频。常用的分频方式主要是对输入时钟的边沿进行计数,当计数器达到

一定数值时,再控制所需时钟信号跳变。以 1000Hz 时钟分频得到 1Hz 时

钟为例,可以用 Q 作为计数信号,Q 初始值为 0,当 1000Hz 时钟上升沿

到来时,Q 自动加 1,直到 Q 加至 999 时,再回到 0。当 Q 的值小于 500

时,令所需时钟信号为低电平,Q 大于 500 时为高电平,即可得到 1Hz 时

钟。当然,这样得到的是占空比 50%的时钟信号,实际中,占空比的大小

对设计没有影响,只要确保时钟频率为 1Hz 即可。

计数部分:时钟是一种计数器,它兼有 60 进制和 24 进制两种计数模

式。因此,计数部分是数字钟的核心部分。24 进制和 60 进制的实现并不

困难。与前述的计数信号 Q 没有本质区别,只是计数状态减少而已。本次

设计中,以 1Hz 时钟信号驱动“秒”位的计数,当“秒”位达到 59 时,

若检测到时钟上升沿到来,则将“秒”位置零,同时产生一个时钟信号,

驱动“分”位加一,到此“秒”位的计数过程即结束。“分”位和“时”位

的计数过程与此类似,此处不再赘述。

输入部分:为了校正时间和设置闹钟,必然要设计一个输入部分。该

部分必须包含两个单元,即数字输入单元和位选择单元。数字输入功能的

实现有多种方法,可以直接通过开关高低电平的变换输入 BCD 码,也可

以设置一个使能端子,使该端子被激活时要输入的数字每秒自动加一。考

虑到 BCD 输入繁琐、占用的开关较多,因此采用第二种方案。位选择单

元用来控制要输入的是“时”位,还是“分”位。可以用一个开关的高低

电平来控制,也可以用两个开关分别控制。为了简化设计,本次设计采用

两个开关控制的方案。

输入转换部分:得到输入的数据之后,必须对数据进行处理,先将输

入的 BCD 码转换为二进制码,然后根据不同的需要把这些数据存入不同

的单元。进行转换时,首先读入用户输入的 BCD 码,根据设计好的查表

程序将其转换为相应的二进制码,再判断此时被激活的是“校正”端子,

还是“闹铃设置”端子,从而将数据存入相应单元。

闹钟比较部分:当时钟时间达到闹钟设定时间时,必须发出提示音。

该部分的主要内容是进行比较,当时钟时间与设定时间一置的时候,即调

用发声部分,从而发出声响。

整点报时部分:该部分的功能与闹钟闹响的部分比较接近,区别在于

闹响的时间不是由用户设定,而是事先确定并且不能改变的。

发声部分:该部分的主要功能是实现整点报时和闹铃闹响时发出声音

的过程。当时钟时间到达闹钟设定时间或整点报时时间的时候,该部分被

激活。

输出部分:该部分的主要功能是向数码管提供显示信号。本设计采用

的是动态扫描方案,即利用人眼的视觉惰性,轮流为数码管的每一位提供

显示信号。该部分需要输出 10 个信号,其中的 7 个用于驱动数码管(数码

管的小数点控制位空出),另外三个用于数码管选择。

主体部分:

整体设计论述

数字时钟由输入的 1000Hz 时钟信号进行分频,得到 500Hz 和 1Hz 的

时钟信号。1Hz 时钟信号的上升沿到来时,触发计数模块的“秒”位加一

操作,经过数据处理,将生成与数码管各位所要显示的数字相对应的二进

制码,再经过显示模块的转换,生成数码管的位选择信号和七段码,从而

实现时钟的正常显示。

为实现时间的校正功能,设计中加入了一个使能端“a”,一个“时”

位选择信号“hour”,一个“分”位选择信号“min”,和一个加一使能端子

“tune”。“a”端子为低电平时,校正功能被封锁,只有“a”端为高电平

时,校正功能才有效。“tune”端子由 1Hz 时钟驱动,该端子被激活时,当

前显示数字每秒加一,“hour”、“min”端子控制“tune”的加一操作针对

的是“时”位还是“分”位。

在闹钟功能的实现中,主要有两个问题,一是如何设定闹钟时间,二

是如何判断时钟时间到达闹钟设定的时刻并给出闹铃发出提示音的信号。

为解决第一个问题,设计中加入了“rhou1”、“rhou0”、“min1”、“min0”

四个单元,分别存储用户输入的闹铃时间,在实现该功能时,用户的输入

过程与前述校正时间的过程相同。而为了解决第二个问题,设计中用“if”

语句建立了一个判断模块,和一个闹响信号“d2”。到达设定时间时,“d2”

即输出高电平,否则为低电平。当然,这里还设计了一个闹铃设置使能端

“f”,用来控制时钟是否工作在闹铃设置状态。

对于整点报时功能的实现与闹钟设置的过程相类似,区别在于该功能

的实现中,时间的设定是事先在 VHDL 代码里规定好的,用户无法更改。

整点时刻,d1 端子就会按要求在适当时间给出高电平。但为了避免打扰用

户,设计中加入了使能端“c”,用户可以通过改变该端子的状态来控制是

否发出提示音。

响铃功能主要通过蜂鸣器实现,该单元比较简单,“d1”或“d2”信号

为高电平时,选通蜂鸣器即可。若要给定蜂鸣器的响声频率,可以使“d1”

或“d2”与相应频率的时钟信号进行“与”操作。

单元模块设计与仿真

分频模块:

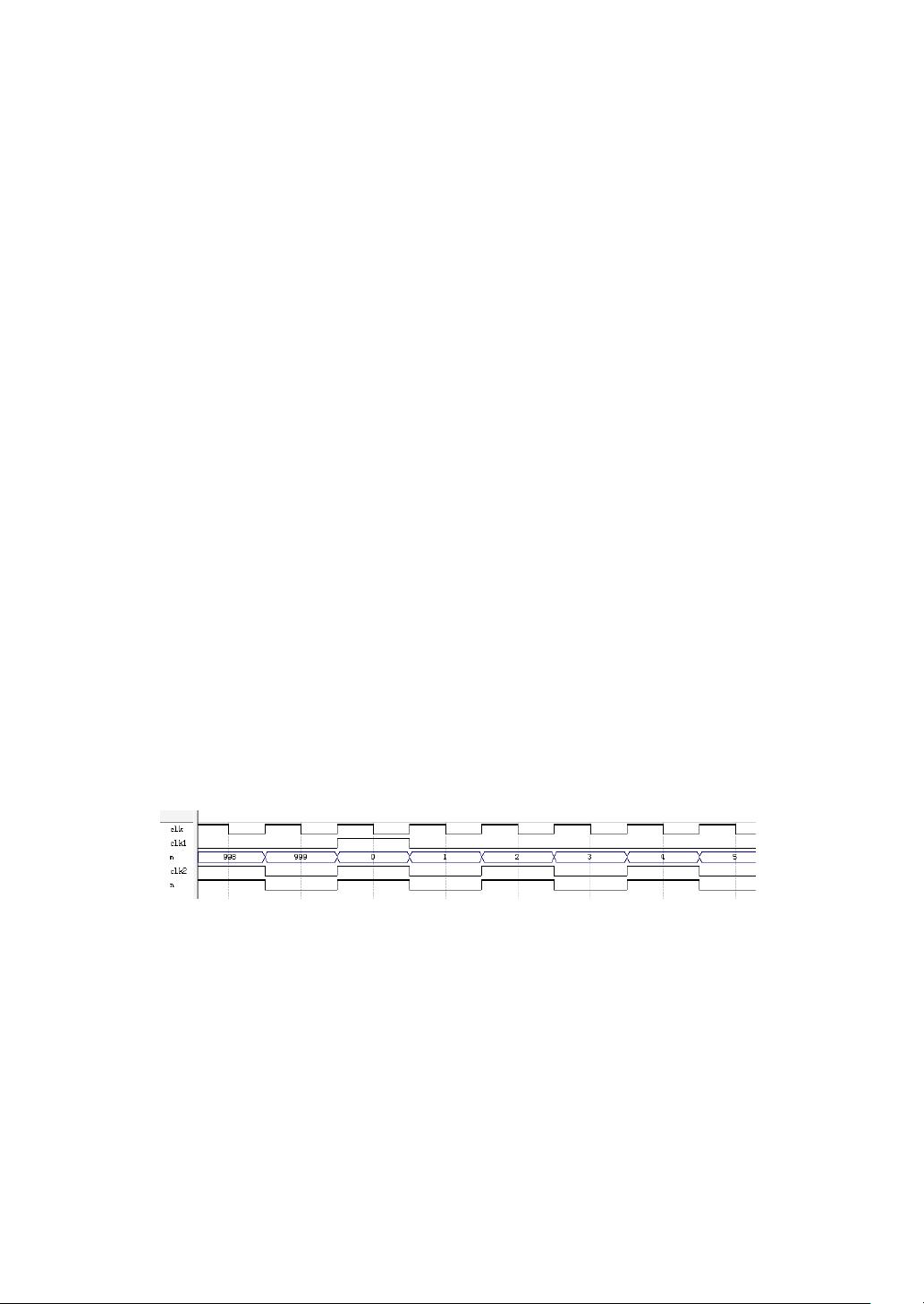

图中,clk 为 1000Hz 输入时钟信号,clk1、clk2 分别为分频后得到的 1Hz、

500Hz 时钟信号,n、m 分别为 1Hz、500Hz 时钟的计数器。

当 clk 信号的上升沿到来时,n、m 进行计数,n 从 999 跳变到 0 时,clk1

变为高电平,其余时刻均为低电平。而 m 始终在“0”、“1”之间跳变,clk2

与其保持一致。

计数模块:

评论1