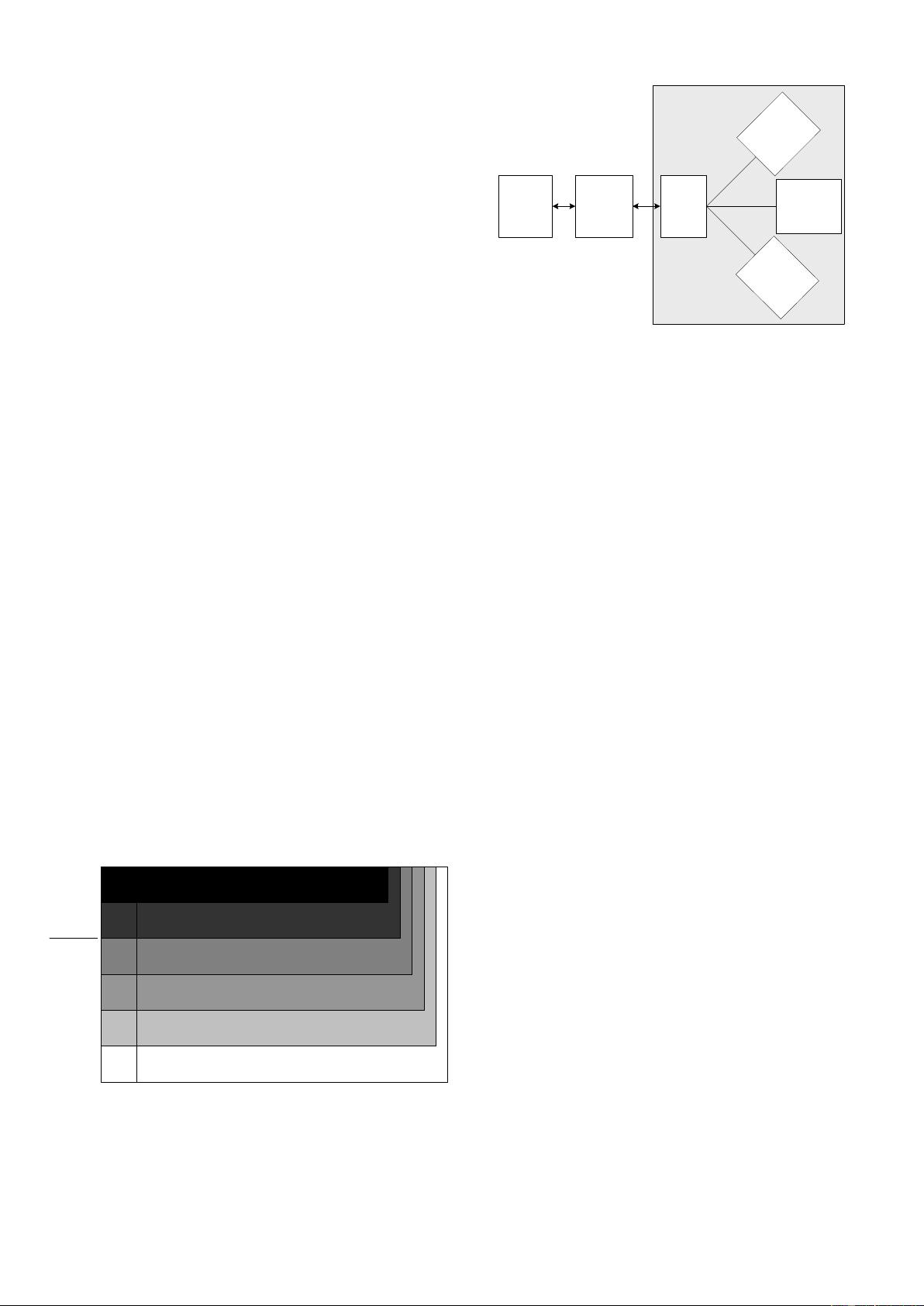

**SWD Debug Interfaces详解** 在嵌入式系统开发中,调试接口是不可或缺的一部分,它使得开发者能够对微控制器(MCU)或系统级芯片(SoC)进行程序加载、调试和故障排查。JTAG(Joint Test Action Group)和SWD(Serial Wire Debug)是两种常用的调试协议,尤其在ARM架构的设备中广泛使用。本篇将深入探讨这两种协议以及它们在SWD Debug Interfaces中的应用。 **JTAG协议** JTAG最初是为了电路板测试而设计的,但后来被广泛应用于嵌入式系统的调试。JTAG协议通过四个引脚——TCK(Test Clock)、TDI(Test Data In)、TDO(Test Data Out)和TMS(Test Mode Select)来实现数据传输和控制。开发者可以通过这个接口执行各种操作,如读取和修改寄存器、运行CPU、检测硬件错误等。 **SWD协议** 随着技术的发展,SWD应运而生,其主要目的是为了减少物理引脚的数量,以适应更小封装的芯片。SWD协议只需要两根线:SWDIO(Serial Wire Data I/O)和SWCLK(Serial Wire Clock),同时实现了数据传输和时钟信号。尽管引脚数量减少,但SWD仍然可以提供与JTAG相当的功能,甚至在某些情况下,如低功耗应用,SWD更具优势。 **SWD与JTAG的对比** 1. 引脚数量:JTAG需要4个引脚,而SWD只需2个,这在资源有限的嵌入式系统中尤其重要。 2. 速度:虽然JTAG的原始设计允许更高的数据速率,但在实际应用中,SWD的速度可以与JTAG相媲美,甚至更快。 3. 功耗:SWD的低引脚数量意味着更低的功耗,更适合电池供电的设备。 4. 灵活性:SWD接口可以在不改变硬件的情况下升级到更高版本的协议,而JTAG则需要额外的硬件支持。 **Low_Pin-Count_Debug_Interfaces_for_Multi-device_Systems.pdf** 这份文档可能详细阐述了在多设备系统中如何利用低引脚数的调试接口(如SWD)进行有效调试。它可能涵盖了如何配置和管理多个设备的SWD接口,如何处理冲突,以及如何在复杂的系统中高效地利用这些接口进行调试和测试。 JTAG和SWD都是嵌入式系统调试的重要工具,选择哪一种取决于具体的应用需求,如资源限制、功耗要求、调试速度和灵活性。了解并熟练掌握这两种协议,对于提升开发效率和优化产品性能具有重要意义。在实际项目中,根据设备特性、成本和设计约束灵活选择合适的调试接口,将有助于实现更高效、可靠的系统设计。

SWD Debug Interfaces.zip (1个子文件)

SWD Debug Interfaces.zip (1个子文件)  Low_Pin-Count_Debug_Interfaces_for_Multi-device_Systems.pdf 156KB

Low_Pin-Count_Debug_Interfaces_for_Multi-device_Systems.pdf 156KB- 1

- 粉丝: 99

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- springboot060师生共评的作业管理系统设计与实现.zip

- springboot257基于SpringBoot的中山社区医疗综合服务平台.zip

- MATLAB程序:多微网优化,多能源系统优化,多Energyhub 协同优化 摘要:基于多能量集成的优点,本文建立了一个基于交互控制的双级两阶段框架,以实现互联多能量系统(MESs)之间的最佳能量供应

- springboot062购物推荐网站的设计与实现.zip

- springboot258流浪动物救助网站.zip

- springboot257基于SpringBoot的中山社区医疗综合服务平台_0303174040.zip

- 6自由度机械臂MATLAB仿真KUKA KR6机器人仿真 simulink simscape 逆向运动学,正向运动学 非线性控制

- springboot063知识管理系统.zip

- springboot259交通管理在线服务系统的开发.zip

- springboot259交通管理在线服务系统的开发_0303174040.zip

- springboot064高校学科竞赛平台.zip

- springboot260火锅店管理系统.zip

- springboot260火锅店管理系统_0303174040.zip

- GlobalUrban-ISA-GS.rar 全球城市边界、不透水表面及绿地数据集下载

- Labview工业以太网Ethernetip TCP通讯培训支持所有Ethernetip协议的设备和模块常用罗克韦尔 ABPLC,欧姆龙NXNJPLC数据标签通讯让你从原理上学会从此定值自己的通讯协议

- springboot261高校专业实习管理系统的设计和开发.zip

信息提交成功

信息提交成功

评论0