PCI Express

®

Base Specification

Revision 2

3.0

Version 0.5

December 20

September 12, 2006 2008

2

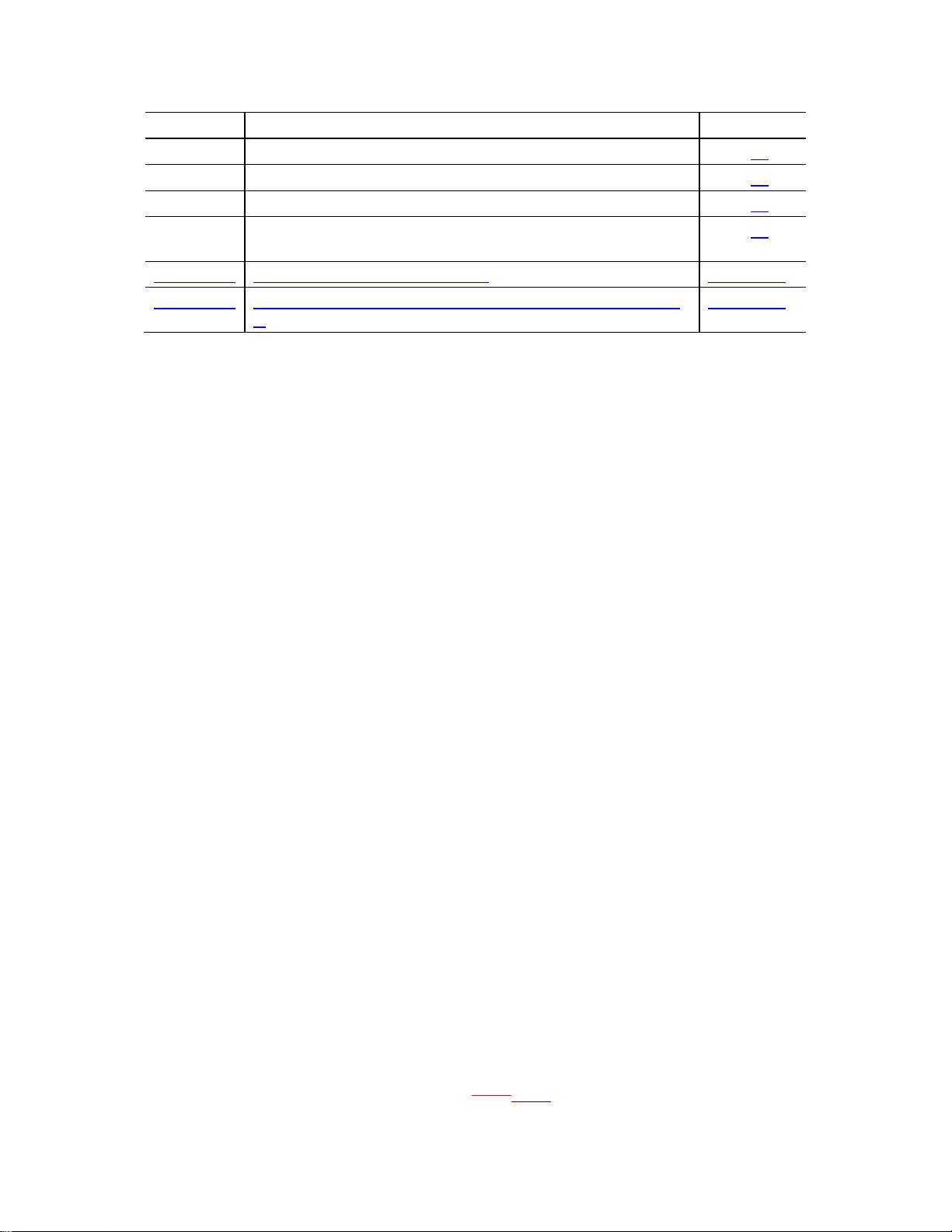

Revision Revision History DATE

1.0 Initial release. 07/22/2002

1.0a Incorporated Errata C1-C66 and E1-E4.17. 04/15/2003

1.1 Incorporated approved Errata and ECNs. 03/28/2005

2.0 Added 5.0 GT/s data rate and incorporated approved Errata

and ECNs.

12/20/2006

3.0, ver. 0.3 First PCI-SIG membership review. 05/22/2008

3.0, ver. 0.5 Incorporated approved errata and ECNs and updated Chapter

4,

09/12/2008

PCI-SIG

®

disclaims all warranties and liability for the use of this document and the information

contained herein and assumes no responsibility for any errors that may appear in this document, nor

does PCI-SIG make a commitment to update the information contained herein.

Contact the PCI-SIG office to obtain the latest revision of this specification.

Questions regarding the PCI Express Base Specification or membership in PCI-SIG may be

forwarded to:

Membership Services

www.pcisig.com

E-mail: administration@pcisig.com

Phone: 503-619-0569

Fax: 503-644-6708

Technical Support

techsupp@pcisig.com

DISCLAIMER

This PCI Express Base Specification is provided “as is” with no warranties whatsoever, including

any warranty of merchantability, noninfringement, fitness for any particular purpose, or any

warranty otherwise arising out of any proposal, specification, or sample. PCI-SIG disclaims all

liability for infringement of proprietary rights, relating to use of information in this specification.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is

granted herein.

PCI, PCI Express, PCIe, and PCI-SIG are trademarks or registered trademarks of PCI-SIG.

All other product names are trademarks, registered trademarks, or servicemarks of their respective

owners.

Copyright © 2002-2006 2008 PCI-SIG

PCI EXPRESS BASE SPECIFICATION, REV. 23.0, VER. 0.5

3

Contents

OBJECTIVE OF THE SPECIFICATION............................................................................... 23

DOCUMENT ORGANIZATION.............................................................................................. 23

DOCUMENTATION CONVENTIONS................................................................................... 24

TERMS AND ACRONYMS...................................................................................................... 25

REFERENCE DOCUMENTS................................................................................................... 32

1. INTRODUCTION............................................................................................................... 33

1.1. A THIRD GENERATION I/O INTERCONNECT ................................................................... 33

1.2. PCI EXPRESS LINK......................................................................................................... 35

1.3. PCI EXPRESS FABRIC TOPOLOGY .................................................................................. 37

1.3.1. Root Complex........................................................................................................ 37

1.3.2. Endpoints .............................................................................................................. 38

1.3.3. Switch.................................................................................................................... 41

1.3.4. Root Complex Event Collector.............................................................................. 42

1.3.5. PCI Express to PCI/PCI-X Bridge........................................................................ 42

1.4. PCI EXPRESS FABRIC TOPOLOGY CONFIGURATION....................................................... 42

1.5. PCI EXPRESS LAYERING OVERVIEW.............................................................................. 43

1.5.1. Transaction Layer................................................................................................. 44

1.5.2. Data Link Layer.................................................................................................... 44

1.5.3. Physical Layer ...................................................................................................... 45

1.5.4. Layer Functions and Services............................................................................... 45

2. TRANSACTION LAYER SPECIFICATION ................................................................. 49

2.1. T

RANSACTION LAYER OVERVIEW.................................................................................. 49

2.1.1. Address Spaces, Transaction Types, and Usage................................................... 50

2.1.2. Packet Format Overview ...................................................................................... 52

2.2. TRANSACTION LAYER PROTOCOL - PACKET DEFINITION............................................... 53

2.2.1. Common Packet Header Fields ............................................................................ 53

2.2.2. TLPs with Data Payloads - Rules......................................................................... 56

2.2.3. TLP Digest Rules .................................................................................................. 60

2.2.4. Routing and Addressing Rules.............................................................................. 60

2.2.5. First/Last DW Byte Enables Rules........................................................................ 64

2.2.6. Transaction Descriptor......................................................................................... 67

2.2.7. Memory, I/O, and Configuration Request Rules................................................... 72

2.2.8. Message Request Rules......................................................................................... 77

2.2.9. Completion Rules.................................................................................................. 91

2.3. H

ANDLING OF RECEIVED TLPS...................................................................................... 94

2.3.1. Request Handling Rules........................................................................................ 97

PCI EXPRESS BASE SPECIFICATION, REV. 23.0, VER. 0.5

4

2.3.2. Completion Handling Rules................................................................................ 110

2.4. TRANSACTION ORDERING............................................................................................ 112

2.4.1. Transaction Ordering Rules ............................................................................... 112

2.4.2. Update Ordering and Granularity Observed by a Read Transaction................ 118

2.4.3. Update Ordering and Granularity Provided by a Write Transaction................ 119

2.5. VIRTUAL CHANNEL (VC) MECHANISM........................................................................ 119

2.5.1. Virtual Channel Identification (VC ID).............................................................. 121

2.5.2. TC to VC Mapping.............................................................................................. 122

2.5.3. VC and TC Rules................................................................................................. 123

2.6. ORDERING AND RECEIVE BUFFER FLOW CONTROL ..................................................... 124

2.6.1. Flow Control Rules............................................................................................. 125

2.7. DATA INTEGRITY ......................................................................................................... 135

2.7.1. ECRC Rules ........................................................................................................ 136

2.7.2. Error Forwarding............................................................................................... 140

2.8. COMPLETION TIMEOUT MECHANISM ........................................................................... 142

2.9. LINK STATUS DEPENDENCIES ...................................................................................... 143

2.9.1. Transaction Layer Behavior in DL_Down Status............................................... 143

2.9.2. Transaction Layer Behavior in DL_Up Status ................................................... 144

3. DATA LINK LAYER SPECIFICATION ...................................................................... 145

3.1. DATA LINK LAYER OVERVIEW .................................................................................... 145

3.2. DATA LINK CONTROL AND MANAGEMENT STATE MACHINE ...................................... 147

3.2.1. Data Link Control and Management State Machine Rules ................................ 148

3.3. FLOW CONTROL INITIALIZATION PROTOCOL ............................................................... 150

3.3.1. Flow Control Initialization State Machine Rules ............................................... 150

3.4. DATA LINK LAYER PACKETS (DLLPS)........................................................................ 154

3.4.1. Data Link Layer Packet Rules ............................................................................ 154

3.5. DATA INTEGRITY ......................................................................................................... 159

3.5.1. Introduction......................................................................................................... 159

3.5.2. LCRC, Sequence Number, and Retry Management (TLP Transmitter).............. 159

3.5.3. LCRC and Sequence Number (TLP Receiver).................................................... 171

4. PHYSICAL LAYER SPECIFICATION........................................................................ 179

4.1. INTRODUCTION ............................................................................................................ 179

4.2. L

OGICAL SUB-BLOCK................................................................................................... 179

4.2.1. Encoding for 2.5 GT/s and 5 GT/s Data Rates................................................... 180

4.2.2. Encoding for 8GT/s and Higher Data Rates....................................................... 188

4.2.3. <Placeholder>.................................................................................................... 204

4.2.4. Link Initialization and Training.......................................................................... 204

4.2.5. Link Training and Status State Machine (LTSSM) Descriptions........................ 219

4.2.6. Link Training and Status State Rules.................................................................. 222

4.2.7. Clock Tolerance Compensation.......................................................................... 269

4.2.8. Compliance Pattern ............................................................................................ 272

4.2.9. Modified Compliance Pattern............................................................................. 273

4.3. E

LECTRICAL SUB-BLOCK ............................................................................................. 275

4.3.1. Maintaining Backwards Compatibility............................................................... 275

4.3.2. Jitter Budgeting and Measurement..................................................................... 277

PCI EXPRESS BASE SPECIFICATION, REV. 23.0, VER. 0.5

5

4.3.3. Transmitter Specification.................................................................................... 278

4.3.4. Receiver Specification......................................................................................... 293

4.3.5. Transmitter and Receiver DC Specifications...................................................... 307

4.3.6. Channel Specifications........................................................................................ 312

4.3.7. Reference Clock Specifications........................................................................... 319

4.4. 8.0G ELECTRICAL SPECIFICATION ............................................................................... 327

4.4.1. 8.0G Transmitter Specifications ......................................................................... 327

4.4.2. 8.0G Receiver Specifications .............................................................................. 335

4.4.3. Channel Compliance Testing.............................................................................. 345

4.4.4. Refclk Parameters for 8.0G ................................................................................ 352

5. POWER MANAGEMENT .............................................................................................. 357

5.1. OVERVIEW ................................................................................................................... 357

5.1.1. Statement of Requirements.................................................................................. 358

5.2. L

INK STATE POWER MANAGEMENT............................................................................. 358

5.3. PCI-PM

SOFTWARE COMPATIBLE MECHANISMS......................................................... 363

5.3.1. Device Power Management States (D-States) of a Function.............................. 363

5.3.2. PM Software Control of the Link Power Management State.............................. 367

5.3.3. Power Management Event Mechanisms............................................................. 373

5.4. NATIVE PCI EXPRESS POWER MANAGEMENT MECHANISMS....................................... 380

5.4.1. Active State Power Management (ASPM) .......................................................... 380

5.5. AUXILIARY POWER SUPPORT....................................................................................... 396

5.5.1. Auxiliary Power Enabling................................................................................... 396

5.6. POWER MANAGEMENT SYSTEM MESSAGES AND DLLPS............................................. 397

6. SYSTEM ARCHITECTURE .......................................................................................... 399

6.1. INTERRUPT AND PME SUPPORT ................................................................................... 399

6.1.1. Rationale for PCI Express Interrupt Model........................................................ 399

6.1.2. PCI Compatible INTx Emulation........................................................................ 400

6.1.3. INTx Emulation Software Model ........................................................................ 400

6.1.4. Message Signaled Interrupt (MSI/MSI-X) Support............................................. 400

6.1.5. PME Support....................................................................................................... 402

6.1.6. Native PME Software Model .............................................................................. 402

6.1.7. Legacy PME Software Model ............................................................................. 403

6.1.8. Operating System Power Management Notification........................................... 403

6.1.9. PME Routing Between PCI Express and PCI Hierarchies ................................ 403

6.2. E

RROR SIGNALING AND LOGGING................................................................................ 404

6.2.1. Scope................................................................................................................... 404

6.2.2. Error Classification............................................................................................ 404

6.2.3. Error Signaling................................................................................................... 406

6.2.4. Error Logging..................................................................................................... 413

6.2.5. Sequence of Device Error Signaling and Logging Operations .......................... 417

6.2.6. Error Message Controls ..................................................................................... 420

6.2.7. Error Listing and Rules ...................................................................................... 421

6.2.8. Virtual PCI Bridge Error Handling.................................................................... 426

6.2.9. Internal Errors.................................................................................................... 427

6.3. V

IRTUAL CHANNEL SUPPORT ...................................................................................... 428