1

Instruction Set Nomenclature

Status Register (SREG)

SREG: Status Register

C: Carry Flag

Z: Zero Flag

N: Negative Flag

V: Two’s complement overflow indicator

S: N ⊕ V, For signed tests

H: Half Carry Flag

T: Transfer bit used by BLD and BST instructions

I: Global Interrupt Enable/Disable Flag

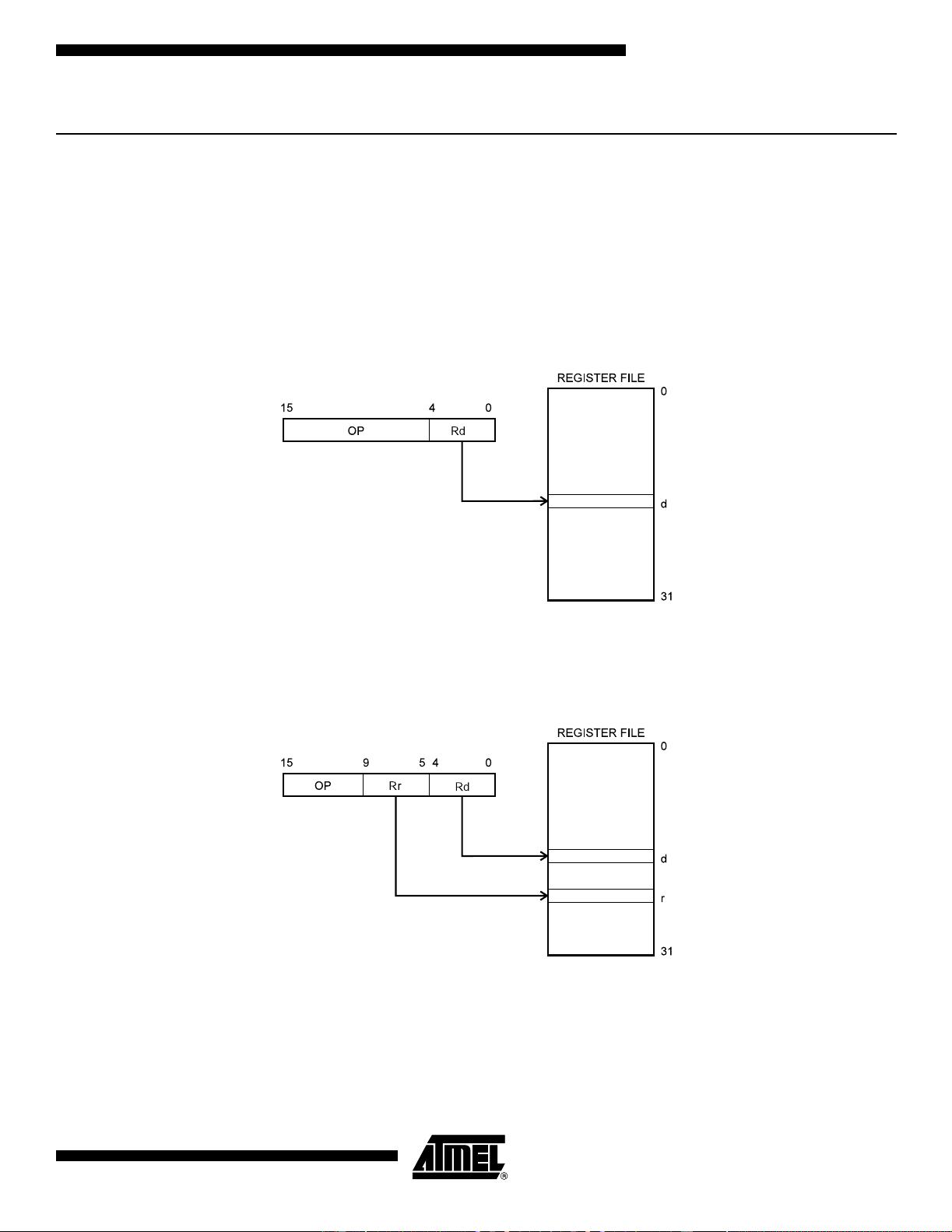

Registers and Operands

Rd: Destination (and source) register in the Register File

Rr: Source register in the Register File

R: Result after instruction is executed

K: Constant data

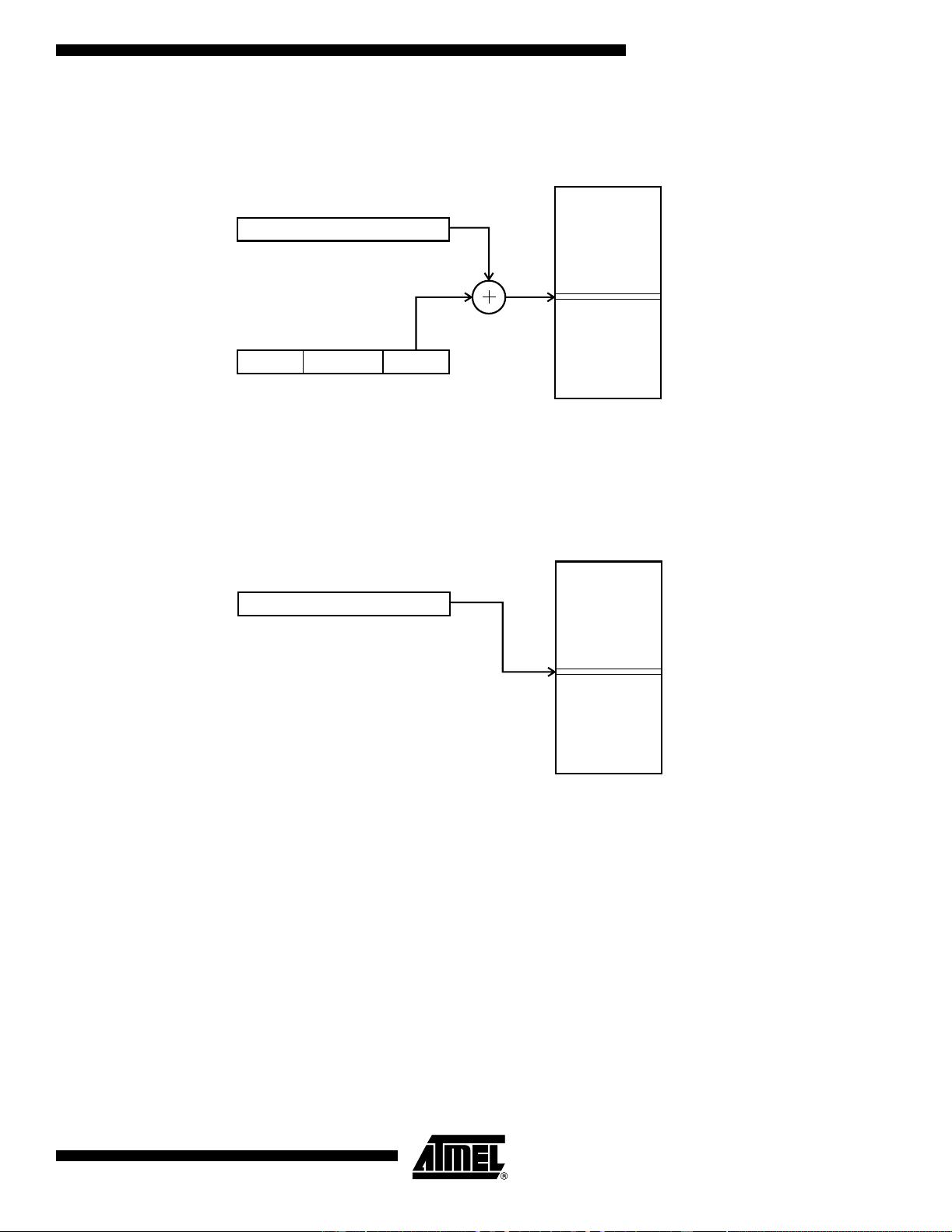

k: Constant address

b: Bit in the Register File or I/O Register (3-bit)

s: Bit in the Status Register (3-bit)

X,Y,Z: Indirect Address Register

(X=R27:R26, Y=R29:R28 and Z=R31:R30)

A: I/O location address

q: Displacement for direct addressing (6-bit)

8-bit

Instruction Set

Rev. 0856D–AVR–08/02