XAPP199 (v1.0) June 11, 2001 www.xilinx.com 1

1-800-255-7778

© 2000 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Summary This application note is written for logic designers who are new to HDL verification flows, and

who do not have extensive testbench-writing experience.

Testbenches are the primary means of verifying HDL designs. This application note provides

guidelines for laying out and constructing efficient testbenches. It also provides an algorithm to

develop a self-checking testbench for any design.

All design files for this application note are available on the FTP site at:

PC: ftp://ftp.xilinx.com/pub/applications/xapp/xapp199.zip

UNIX: ftp://ftp.xilinx.com/pub/applications/xapp/xapp199.tar.gz

Introduction Due to increases in design size and complexity, digital design verification has become an

increasingly difficult and laborious task. To meet this challenge, verification engineers rely on

several verification tools and methods. For large, multi-million gate designs, engineers typically

use a suite of formal verification tools. However, for smaller designs, design engineers usually

find that HDL simulators with testbenches work best.

Testbenches have become the standard method to verify HLL (High-Level Language) designs.

Typically, testbenches perform the following tasks:

• Instantiate the design under test (DUT)

• Stimulate the DUT by applying test vectors to the model

• Output results to a terminal or waveform window for visual inspection

• Optionally compare actual results to expected results

Typically, testbenches are written in the industry-standard VHDL or Verilog hardware

description languages. Testbenches invoke the functional design, then stimulate it. Complex

testbenches perform additional functions—for example, they contain logic to determine the

proper design stimulus for the design or to compare actual to expected results.

The remaining sections of this note describe the structure of a well-composed testbench, and

provide an example of a self-checking testbench—one that automates the comparison of actual

to expected testbench results.

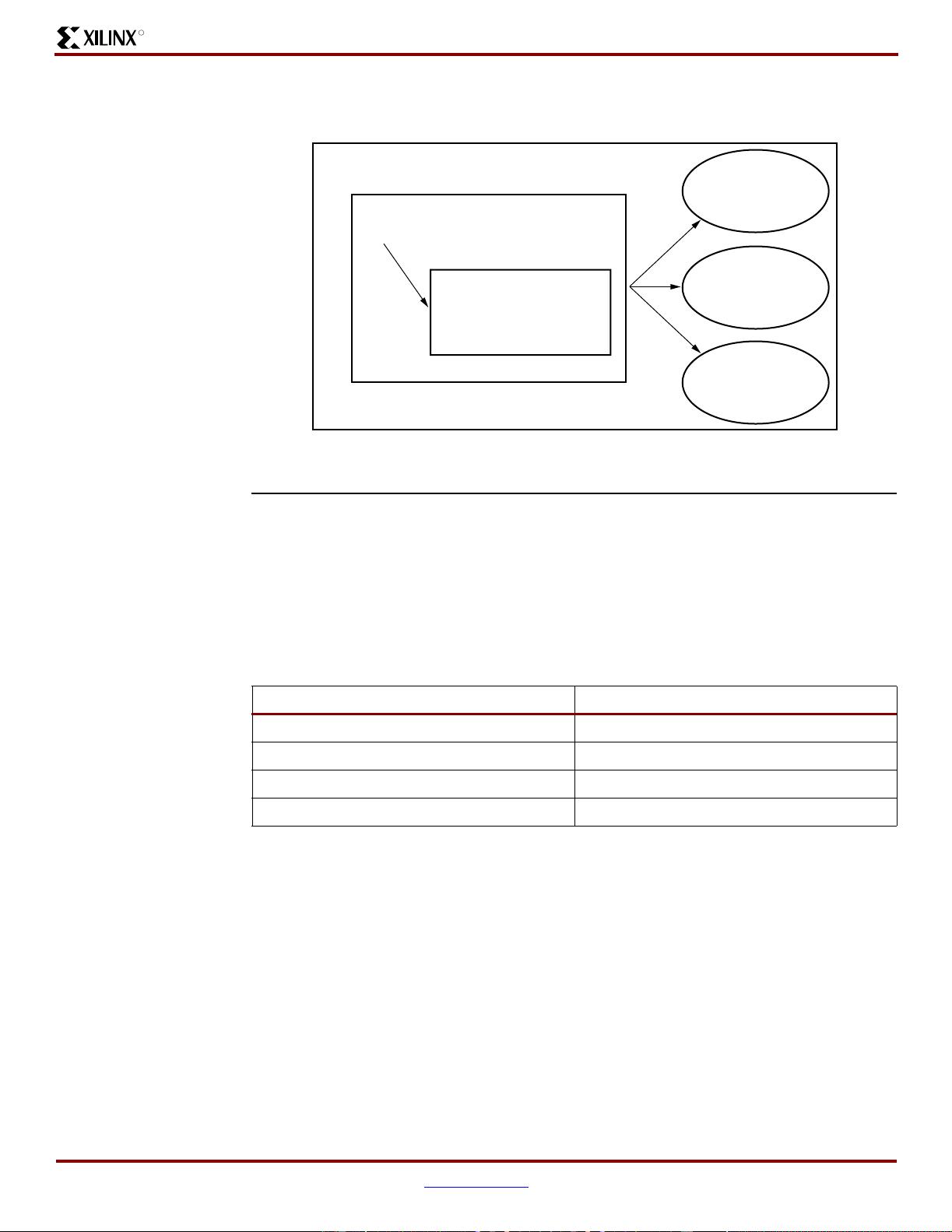

Figure 1 shows a standard HDL verification flow which follows the steps outlined above.

Since testbenches are written in VHDL or Verilog, testbench verification flows can be ported

across platforms and vendor tools. Also, since VHDL and Verilog are standard non-proprietary

Application Note: Test Benches

XAPP199 (v1.0) June 11, 2001

Writing Efficient Testbenches

Author: Mujtaba Hamid

R