GCD logic Circuit

1

Greatest Common Divisor Logic Circuit

Abstract

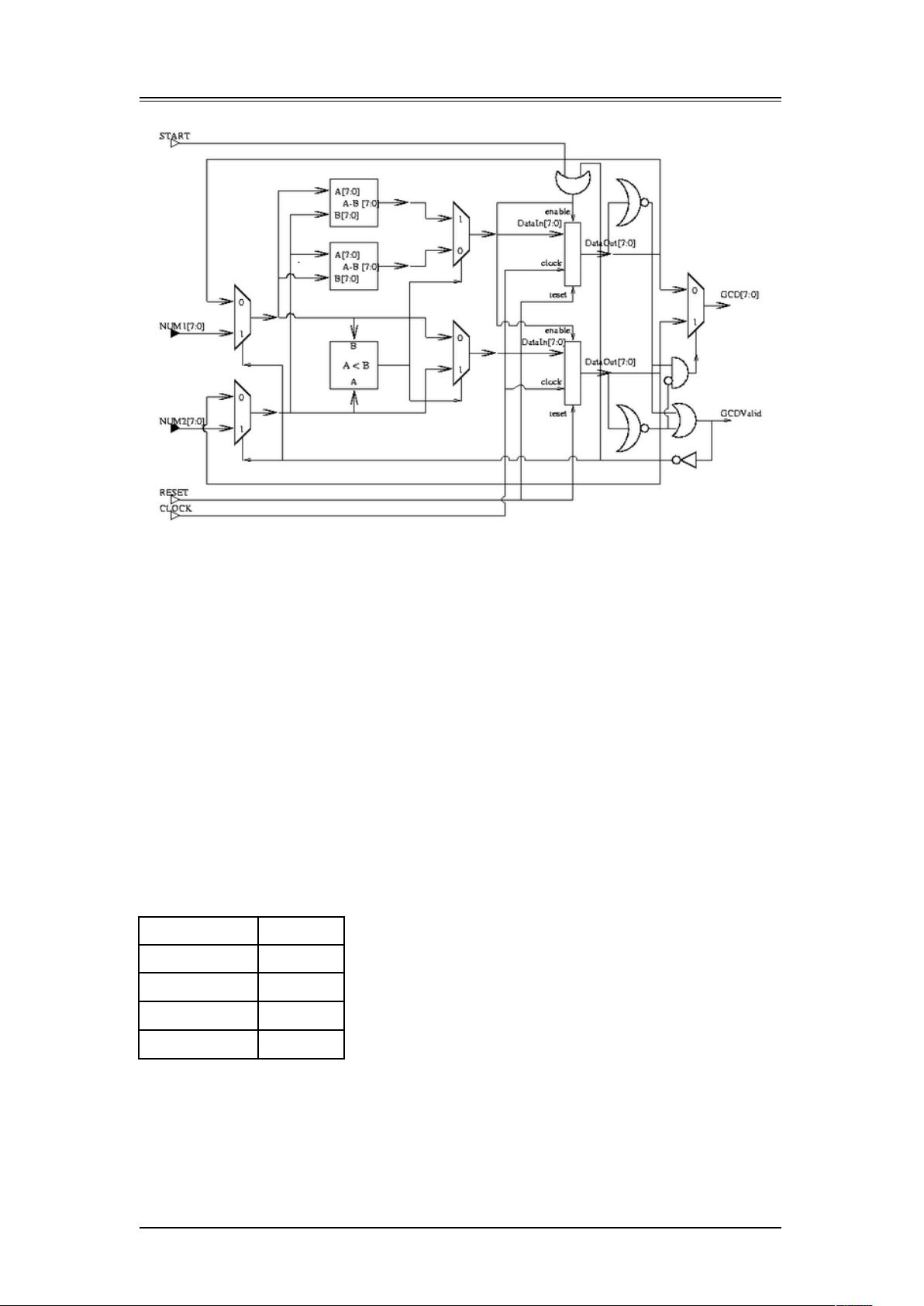

This report describes the implementation of a digital circuit that computes

the Greatest Common Divisor (GCD) of two unsigned eight-bit integers.

Introduction

This report is organized as follows. First we describe the black-box

behavior of the entity. In section 2, we present an architecture of the GCD

circuit. The GCD circuit is designed using a top-down aproach, and in

section 3 we describe the sub-circuits used. The different sub-circuits

result in different designs of the GCD logic. In Section 4, we compares

the Area/Performance Tradeoffs for both the implementations. In Section

5, we present out validation methodology and describe the architecture of

the test benches. In Section 6 we present some simulation results.

Entity

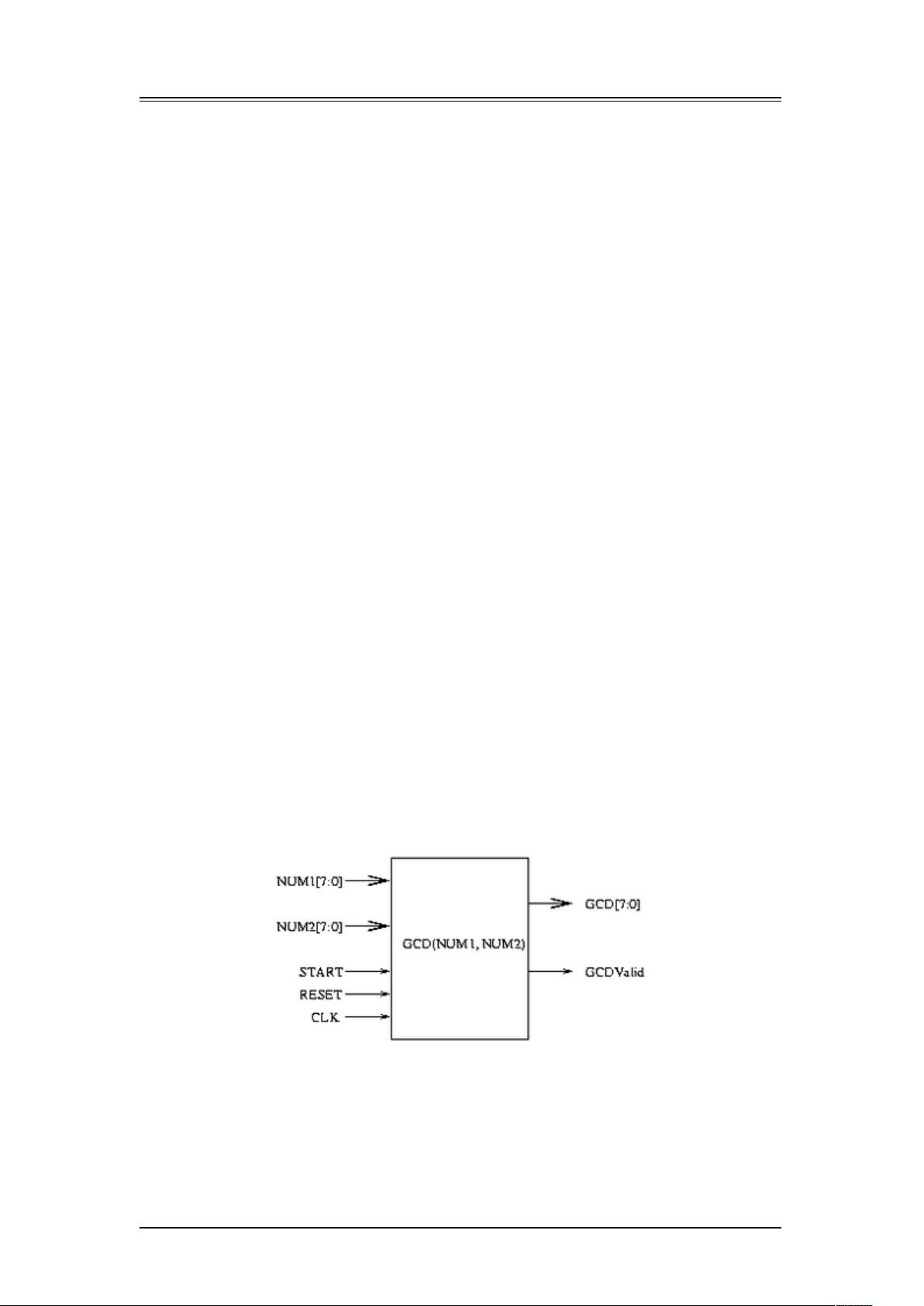

Figure 1 shows the GCD entity.

Figure 1: Greatest Common Divisor Component