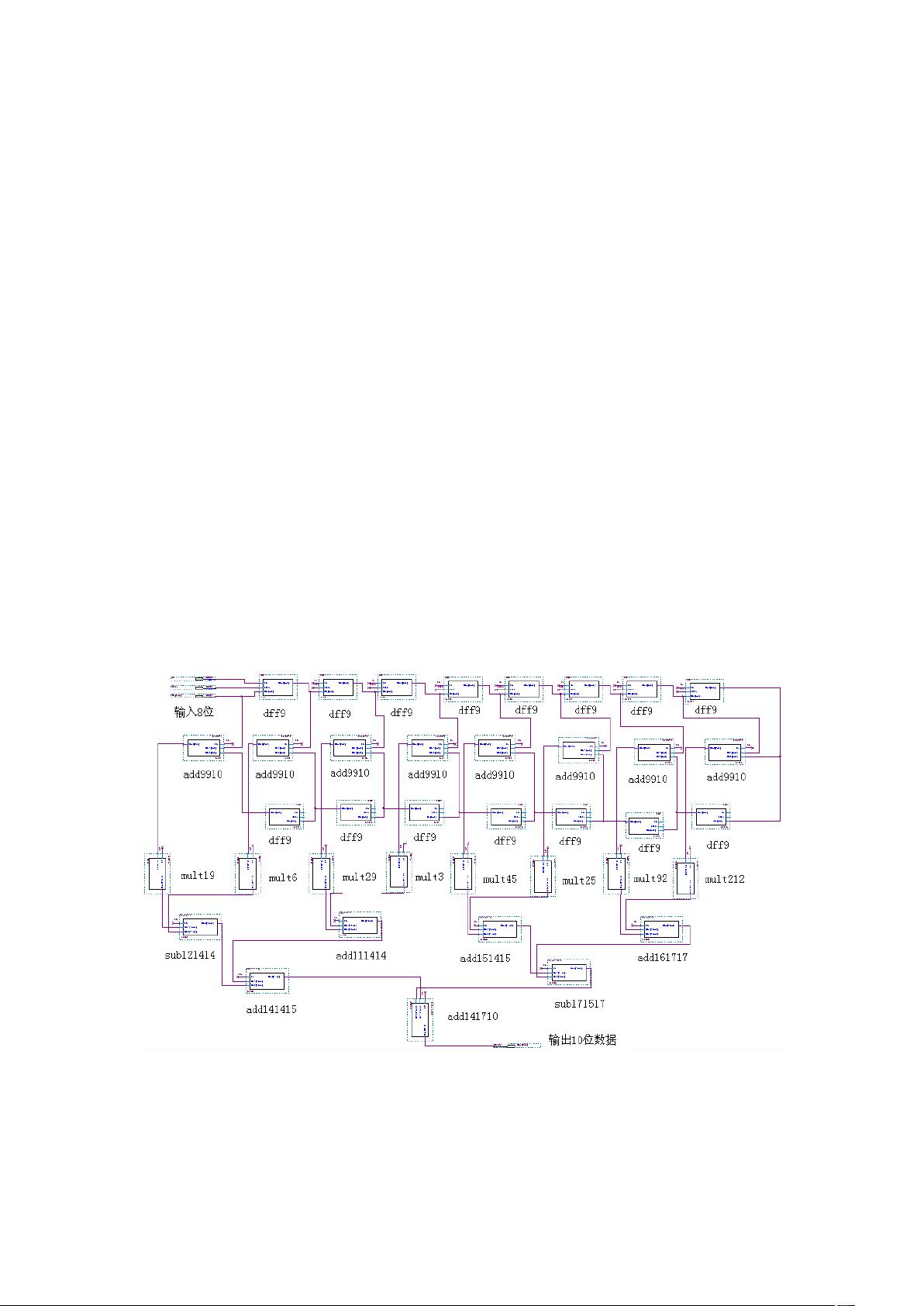

我的原理说明是根据上面原理图的设计顺序逐步进行的。

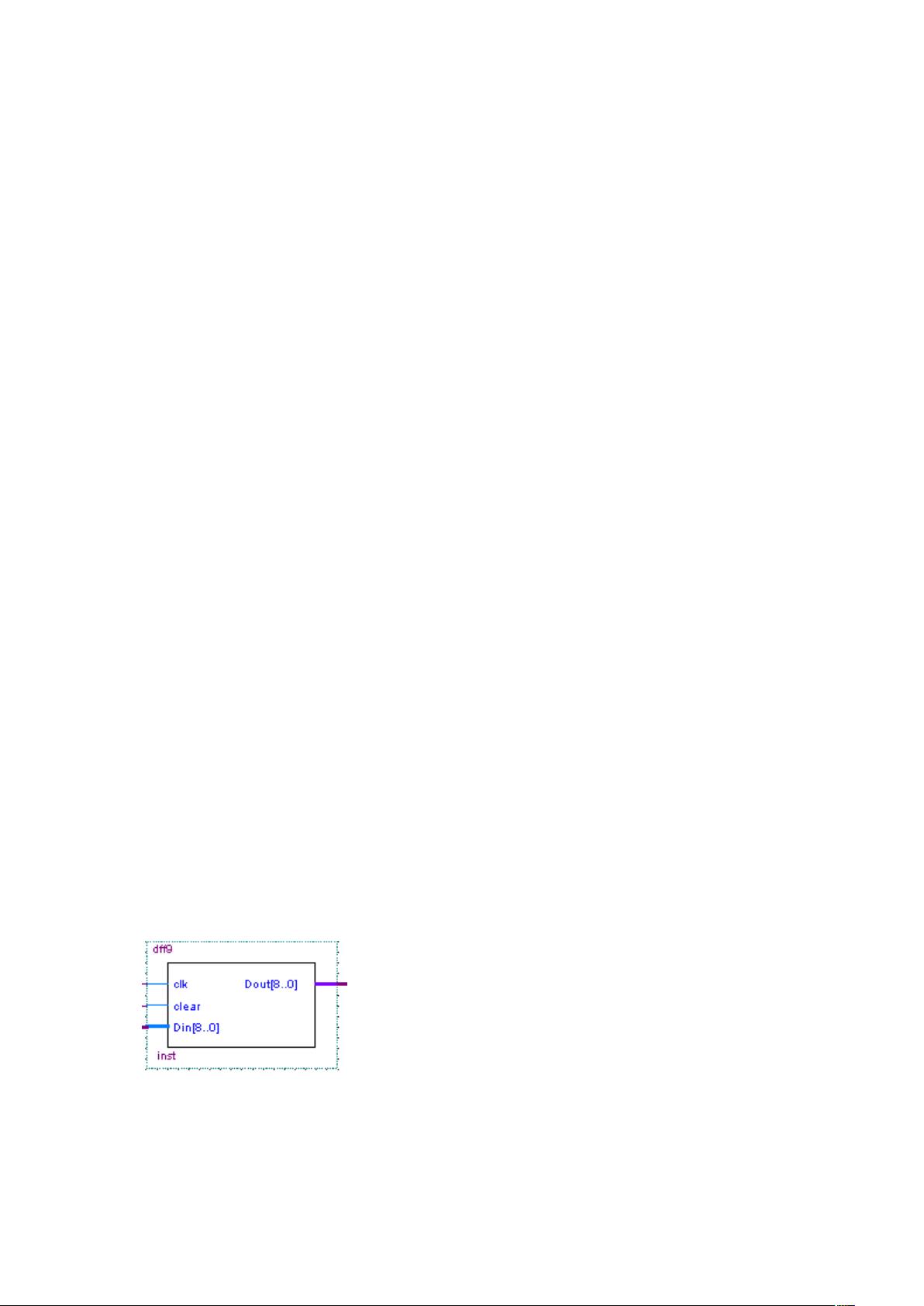

1 寄存器(延时器)。

原理图上标有 dff9 的器件。输入 9 位数据,通过 dff9 的 D 触发寄存器,达到延时的作

用。

2 第一级加法器

数据通过 add9910,就是 9 位数字输入,10 位数字输出加法器,完成第一级相加运算,

因为本题是 16 阶 FIR 数字滤波器,它的滤波系数有对称的关系,所以采用上面的第一级加

法器,达到简化运算的效果。

3 乘法器

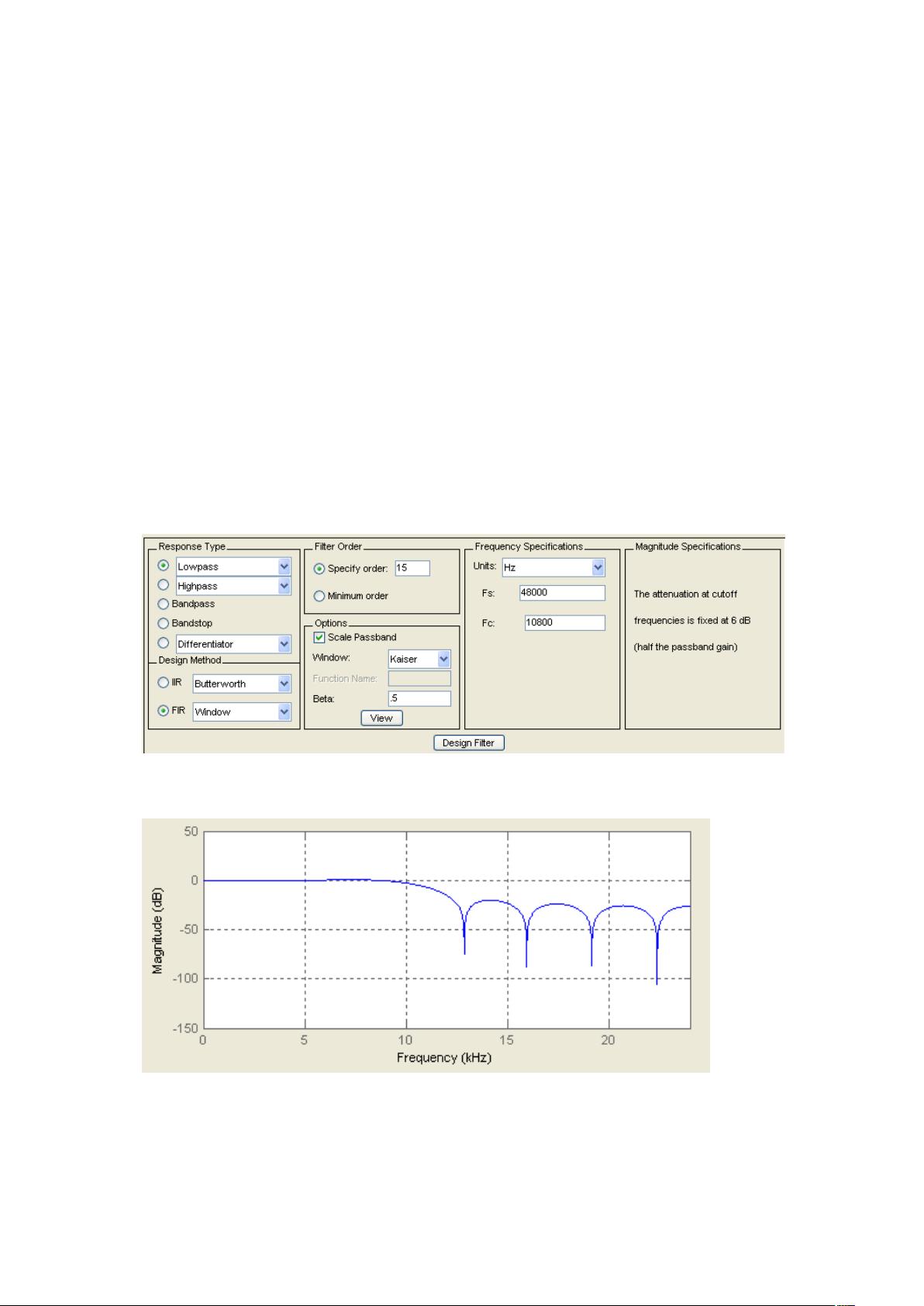

乘 法 器 用 来 将 数 据 乘 以 由 matlab 计 算 得 到 的 滤 波 系 数 , 本 题 的 系 数 分 别 为 :

-19,6,29,3,-45,-25,92,212。

在乘法器设计时暂时没有考虑符号,符号问题由下面的减法器实现。即:若系数符号为

负,那么在下一级用减法器减去乘法器所得的数据。所有的乘法器为:mult19, mult mult 6,

mult 29, mult 3, mult 45, mult 25, mult 92, mult 212。

4 第二级加,减法器

第二级加法器主要有 add111414,add151415,add161717。add111414 就是说 11 位数据加 14

位数据输出 14 位数据,说有的都是相同的命名规则。减法器的作用是反映乘法器的负号的,

对于负的滤波系数,在此相当于经过减法器相减。

5 第三级加,减法器

与上一级大体相同的原理。

6 输出

输出通过 add141710,将上一级得到的 14 位和 17 位数据相加,再拿出相加结果的高十

位作为输出。

到此,整个 FIR 数字滤波器设计完毕,下面详细说明各个部分的具体实现。

二 详细说明

我的说明是根据上面的概要逐一展开的。

我的设计是先编写各个功能的 vhdl 源文件,再生成功能模块,最后在顶层用原理图的

设计方法连线,组成整个系统。

1 寄存器(延时器)

设计中用 D 触发器组成寄存器,实现寄存功能。这里用来寄存一组 9 位的二进制数据。

实现功能:

在 CP 正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁。

源文件: