TM

Confidential and Proprietary

2

KFA Series - Introduction

Key Hardware Features

• High performance ARM Cortex architecture

• Low power 30% better than today’s benchmark

• Scalability from 16KB to 2MB embedded flash

• FlexCAN with CAN FD option

• FlexIO for configurable number of LIN, SPI, I2C

• Targeting ASIL-B applications

• Security

Key Software Features

• KDS (Kinetis Design Studio)

• Autosar MCAL and OS

• Non-autosar Low-Level Drivers

• Model-based design support

• Extensive 3

rd

party offering

TM

Confidential and Proprietary

3

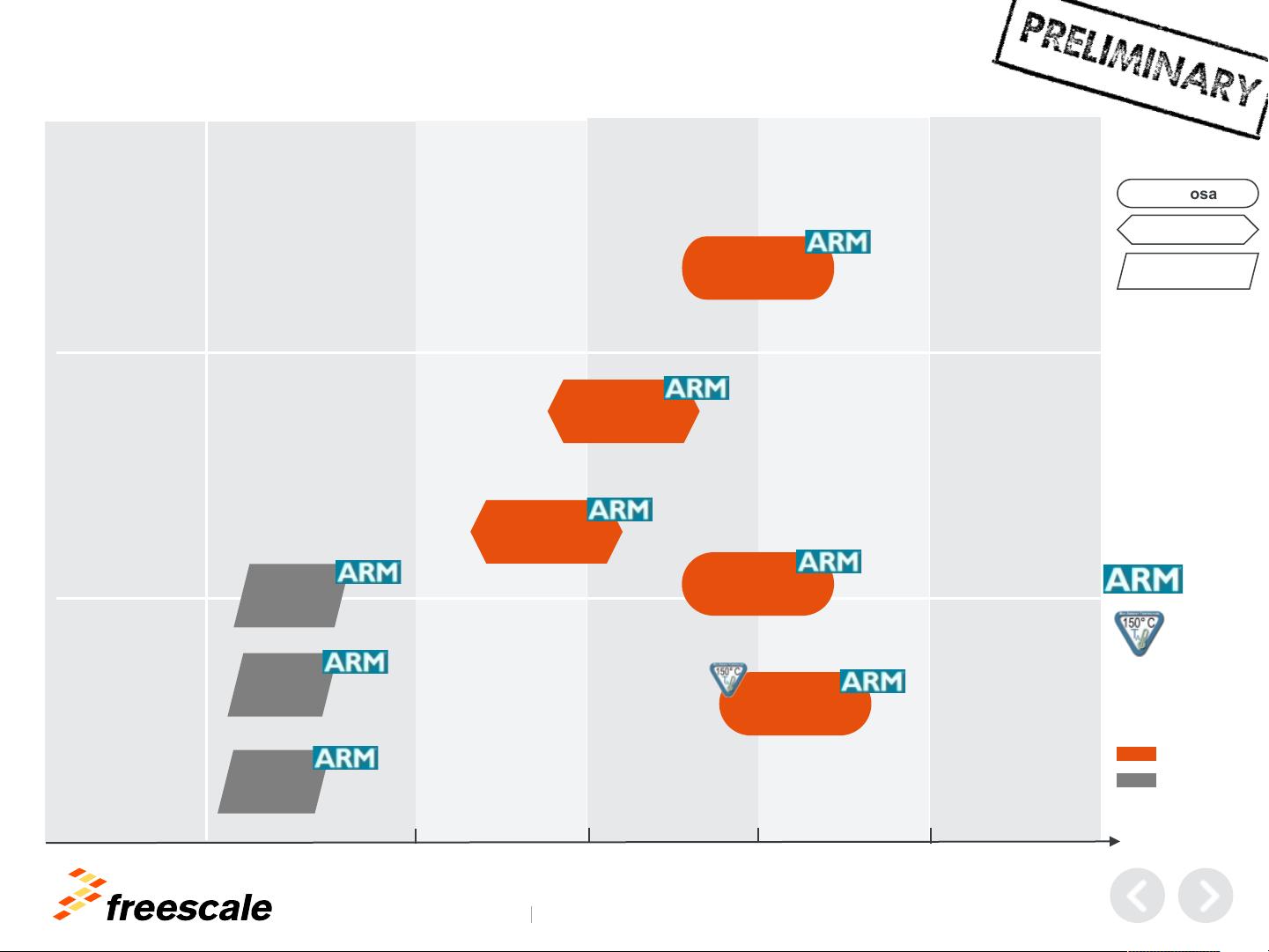

General Purpose MCU Roadmap

2014

2015

2016

2017

Entry

90nm

First

Sample Date

(left edge)

Product

Qualification

(right edge)

Proposal

Planning

Production or

Execution

180nm

Last Updated 10SEP14

2018

KFA 512

M4 up to

120MHz

KEA64

M0+

40MHz

KEA8

M0+

48MHz

Mainstream

High

performance

KEA128

M0+

48MHz

64-128kB, LIN, CAN, 64-80pin

16-64kB, LIN, 32-64pin

8kB, LIN, 16-24pin

256-512kB, FlexIO, CAN-FD, 48-144pin

64-128kB, LIN, CAN, 32-64pin

KFA 1M

M4 up to

150MHz

768kB-1M, FlexIO, CAN-FD, 100-176pin

KFA 2M

M4/M0+ up to

180MHz

1.5M-2M, FlexIO, CAN-FD, Ethernet, Security

100-176pin

KGA 128

M0+

64MHz

16-32kB, LIN, 20-48pin

KGA 32

M0+

48MHz

High temp

(AEC Grade 0)

Cortex

M4/M0+

TM

Confidential and Proprietary

4

KFA512 Block Diagram

Preliminary and subject to change

Communications I/O System

Peripheral Bus

SWD

JTAG

Debugger

Debug

RAM

Up to

64KB

System

Peripheral

Bridge

Flash

Up To

512K

NVIC

Cortex M4

80/120MHz

FPU, DSP, MPU

EEPROM

4KB

2x16ch,

12bit

Dual ADC

2

ACMP

Flex IO peripheral

16ch / 64ch

eDMA

WDT

EWM

PMC

2.7 - 5.5V

POR

FLL Clk Mult

LVD

Ext Osc

(4 - 40MHz)

Int R/C OSC

(~48MHz 1%)

Int LP Osc

(128KHz)

SCG

High performance

• ARM Cortex M4 up to 120MHz w FPU

• eDMA from Qorivva family

Software Friendly Architecture

• High RAM to Flash ratio

• Independent CPU and periph clocking

• 48MHz IRC – no PLL init required in LP

• registers maintained in all modes

• Programmable triggers for ADC no

sw delay counters or extra interrupts

Functional safety

• ISO26262 support for ASIL B or higher

• MPU

• ECC on Flash/Dataflash and RAM

• Independent internal OSC for Watchdog

• Diversity between ADC and ACMP

• Diversity between SPI/SCI and FlexIO

• Core self test libraries

• Scalable LVD protection

Low power

• Low leakage technology

• Multiple VLP modes and IRC combos

• Wake-up on analog thresholds

4x8ch

16-Bit

FlexTimer

2

I2C

3

SPI

4

SCI

(LIN)

2

PDB

3

FlexCAN

w FD

1

PIT

Open-

Drain IO,

KBI,

GPIO

Digital

Components

5V Analogue

Components

MCU Core

and Memories

1

API

RTC

Operating Characteristics I/Os

• Voltage range: 2.7 to 5.5 V 64/100pin compatible within Family

• Temperature (ambient): -40 to 125°C Open-drain for 3.3V and hi-drive pins to save BOM

Powered ESD protection

评论1