GRAPHCORE 第二代 IPU.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

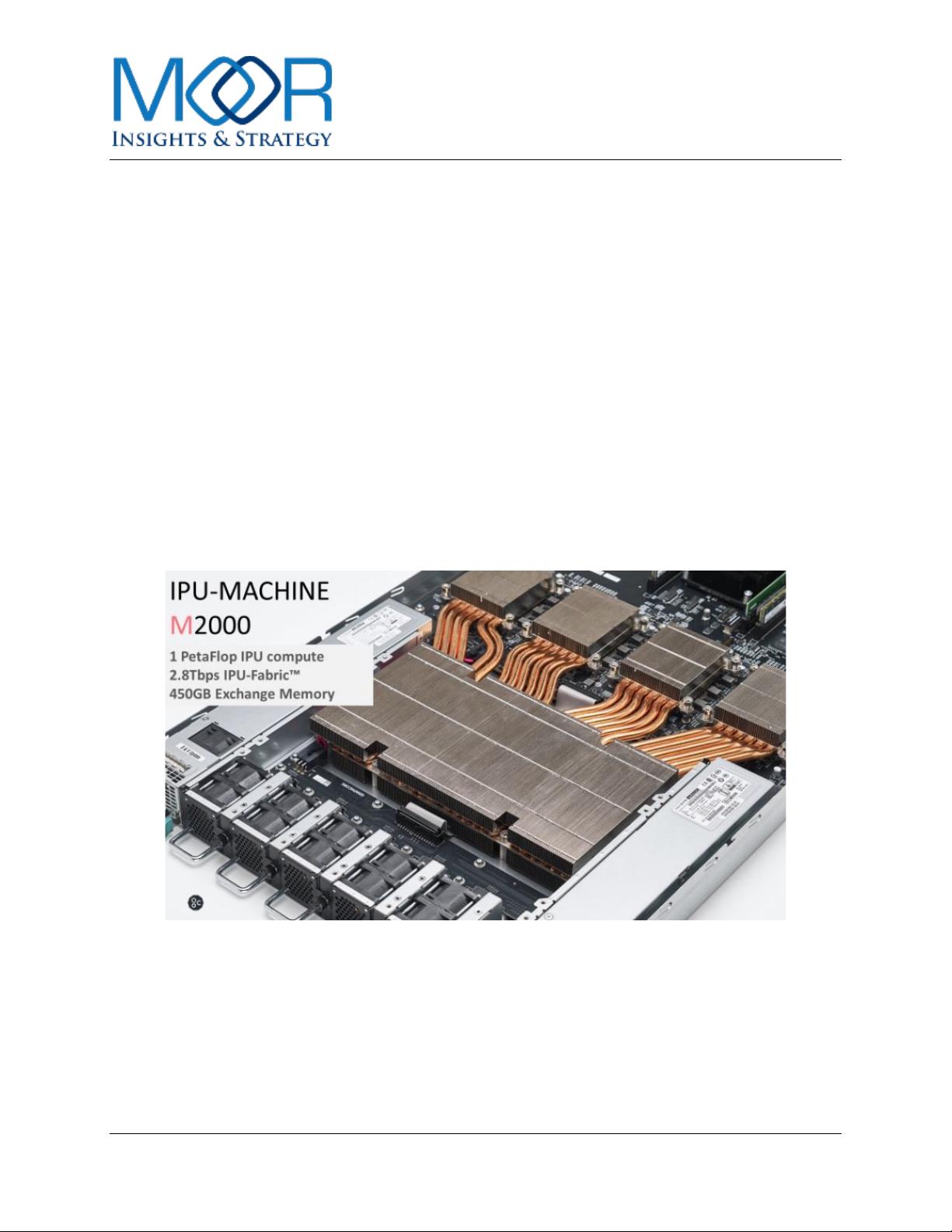

### GRAPHCORE 第二代 IPU 知识点解析 #### 一、概述 Graphcore是一家总部位于英国的初创公司,专注于开发专为人工智能(AI)加速设计的智能处理器(Intelligence Processing Unit, IPU)。自2018年推出首款IPU以来,Graphcore在2020年7月发布了其第二代IPU——MK2,以及基于此的IPU-Machine平台。 #### 二、第二代IPU-Machine特性 - **IPU-Machine M2000**: 该平台由四个IPU组成,每个IPU都拥有强大的处理能力、大量的内存以及内置的可扩展性。 - **硬件规格**: - 每个1U设备能够提供高达1 PFLOP的AI性能和450GB的存储空间。 - 通过集成的100GbE横向扩展结构和PCIe接口,可以实现快速的数据传输。 - 支持高达448GB的“流存储”DRAM,以补充片上IPU内存。 - **Colossus MK2 IPU (GC200)**: - 这是一款大规模并行的594亿晶体管处理器,采用7纳米制程工艺,由台积电制造。 - 提供约250万亿次每秒运算(TOPS),通过2.8Tb/秒的低延迟结构互连900MB的处理器内存储。 - 与第一代相比,核心数量增加了20%,片上SRAM增加了333%。 - **AI-Float技术**: - 这是一项创新的浮点实现技术,旨在提高AI计算的能量效率和性能。 - 使用标准IEEE FP16格式,通过随机舍入特性使得FP16能够匹配FP32的性能。 - 支持250 TFlop/秒的半精度FP16运算速度,以及62.5 TFlop/秒的单精度FP32运算速度。 #### 三、系统软件与可扩展性 - **Poplar软件栈**: - 作为Graphcore的核心软件组件之一,Poplar提供了高级编程接口,简化了开发者的工作流程。 - 支持多种深度学习框架,并且能够自动优化模型以适应IPU的硬件特性。 - **可扩展性**: - MK2 IPU-Machine可以在1024个机架上扩展到最多64,000个IPU。 - 完全配置的AI超级计算机可以提供大约16 EFLOPS的AI性能(16位FP)。 - 新的系统软件增强了可扩展性、部署和管理功能。 #### 四、稀疏性优化 - **针对稀疏性的优化**: - 许多AI模型会产生具有高度稀疏性的模型参数,这意味着很多参数值为零。 - MK2 IPU-Machine支持多种稀疏性优化,包括块稀疏性、标量稀疏性、静态稀疏性和动态稀疏性。 - 通过编译器技术提前识别出这些零元素,从而避免不必要的乘法操作,显著提高了性能。 #### 五、市场定位与竞争分析 - **市场定位**: - Graphcore将重点放在了数据中心和高性能计算领域,在这些场景中,AI应用程序对性能的需求远高于成本敏感度。 - 边缘AI推理处理则更加注重成本和功耗,这是MK2 IPU的一个次要关注点。 - **潜在竞争对手**: - NVIDIA: 在GPU市场上占据主导地位,同时也推出了专门针对AI加速的Tensor Core技术。 - Google: 通过其TPU(Tensor Processing Unit)产品线,在云端AI加速领域有着广泛的影响力。 - Intel: 通过收购Nervana Systems,进入了AI加速器领域,提供了一系列针对AI训练和推理的解决方案。 #### 六、总结 Graphcore推出的第二代IPU-Machine M2000是一个具有强大性能和高可扩展性的平台,旨在解决大规模并行处理工作负载的需求。通过技术创新如Colossus MK2 IPU和AI-Float技术,以及针对稀疏性的优化,Graphcore能够在性能方面取得显著的进步。虽然面临来自NVIDIA、Google和Intel等公司的激烈竞争,但凭借其独特的技术优势和不断扩大的生态系统,Graphcore有望在AI加速领域占据一席之地。

剩余10页未读,继续阅读

- 粉丝: 0

- 资源: 2万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功