没有合适的资源?快使用搜索试试~ 我知道了~

引言 只要在现在的市场上走一圈就会发现,大部分的中小规模 LED 显示系统,采用的是传统的单片机作为主控芯片。但是内部资源较少、运行速度较慢的单片机,很难满足LED大屏幕的显示屏,因为系统要求数据传输量大,扫描速度要快。以FPGA作为控制器,一方面,FPGA采用软件编程实现硬件功能,可以有效提高运行速度;另一方面,它的引脚资源丰富,可扩展性强。因此,用单片FPGA和简单的外围电路就可以实现大屏幕LED显示屏的控制,具有集成度高、稳定性好、设计灵活和效率高等优点。 1 系统总体结构 LED大屏幕显示系统由上位机(PC机)、单片机系统、FPGA控制器、LED显示屏的行列驱动电路

资源推荐

资源详情

资源评论

一种基于一种基于MCU+FPGA的的LED大屏幕控制系统的设计大屏幕控制系统的设计

引言 只要在现在的市场上走一圈就会发现,大部分的中小规模 LED 显示系统,采用的是传统的单片机作为

主控芯片。但是内部资源较少、运行速度较慢的单片机,很难满足LED大屏幕的显示屏,因为系统要求数据传

输量大,扫描速度要快。以FPGA作为控制器,一方面,FPGA采用软件编程实现硬件功能,可以有效提高运行

速度;另一方面,它的引脚资源丰富,可扩展性强。因此,用单片FPGA和简单的外围电路就可以实现大屏幕

LED显示屏的控制,具有集成度高、稳定性好、设计灵活和效率高等优点。 1 系统总体结构 LED大屏

幕显示系统由上位机(PC机)、单片机系统、FPGA控制器、LED显示屏的行列驱动电路

引言引言

只要在现在的市场上走一圈就会发现,大部分的中小规模 LED 显示系统,采用的是传统的单片机作为主控芯片。但是内

部资源较少、运行速度较慢的单片机,很难满足LED大屏幕的显示屏,因为系统要求数据传输量大,扫描速度要快。以FPGA

作为控制器,一方面,FPGA采用软件编程实现硬件功能,可以有效提高运行速度;另一方面,它的引脚资源丰富,可扩展性

强。因此,用单片FPGA和简单的外围电路就可以实现大屏幕LED显示屏的控制,具有集成度高、稳定性好、设计灵活和效率

高等优点。

1 系统总体结构系统总体结构

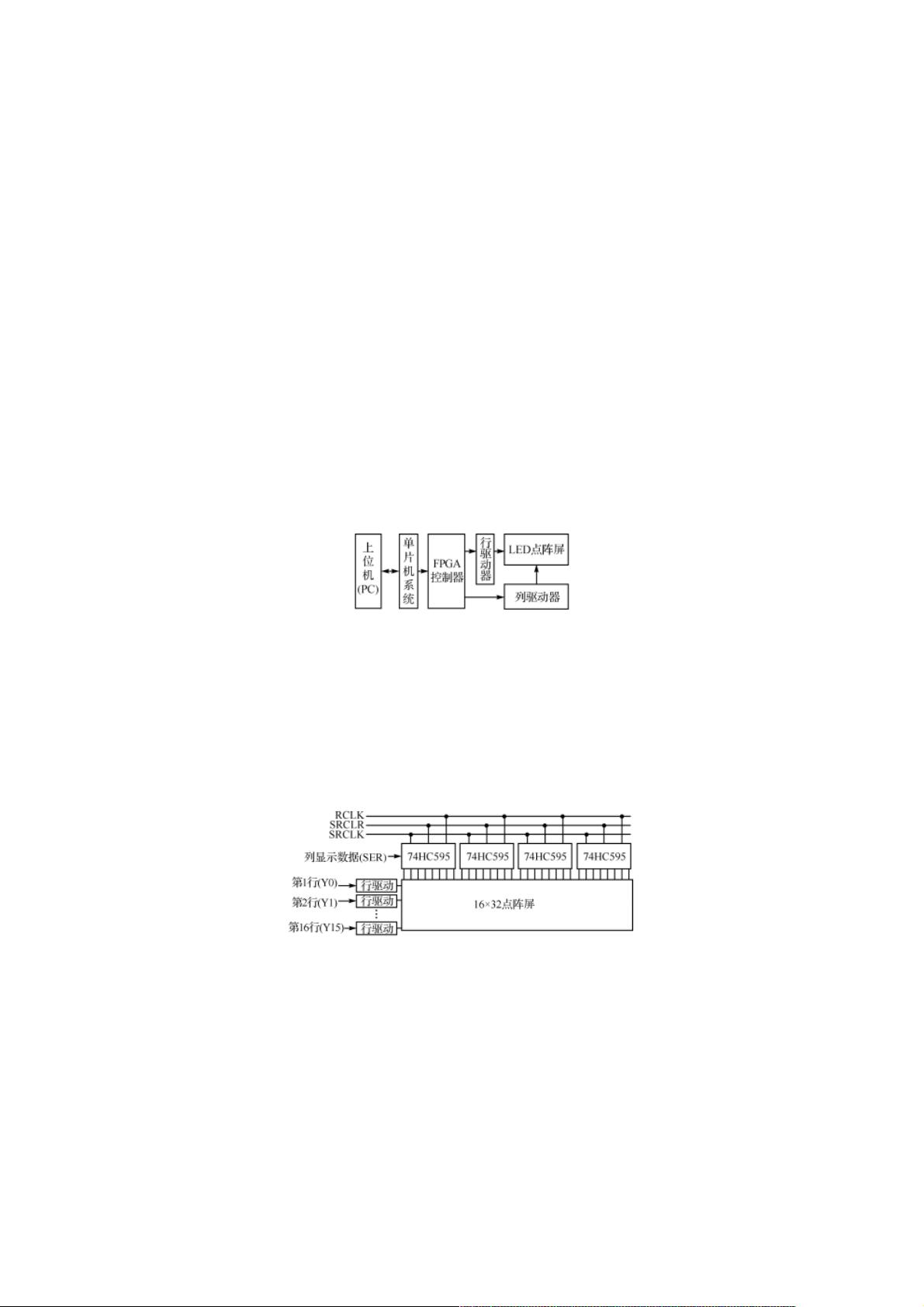

LED大屏幕显示系统由上位机(PC机)、单片机系统、FPGA控制器、LED显示屏的行列驱动电路等模块组成,如图1所

示。上位机负责汉字、字符等数据的采集与发送。单片机系统与上位机之间以异步串行通信工作方式,通过串行端口从上位机

获得已完成格式转换的待显示的图形点阵数据,并将其存入EEPROM存储器。之后通过FPGA控制器,将存储器的显示数据

还原到LED显示屏。扫描控制电路采用可编程逻辑芯片Cyclone EP1C6,利用VHDL语言编程实现,采用1/16扫描方式,刷新

频率在60 Hz以上。本文着重介绍256×1024的单色图文显示屏的FPGA控制模块。

图1 系统总体结构框图

2 LED显示屏基本工作原理显示屏基本工作原理

对大屏幕LED显示屏来说,列显示数据通常采用的是串行传输方式,行采用1/16的扫描方式。图2为16×32点阵屏单元模

块的基本结构,列驱动电路采用4个74HC595级联而成。在移位脉冲SRCLK的作用下,串行数据从74HC595的数据端口SER

一位一位地输入,当一行的所有32列数据传送完后,输出锁存信号RCLK并选通行信号Y0,则第1行的各列数据就可按要求显

示。按同样的方法显示其余各行,当16行数据扫描一遍(即完成一个周期)后,再从第1行开始下一个周期的扫描。只要扫描

的周期小于20 ms,显示屏就不闪烁。

图2 16×32点阵屏基本结构

256×1024大屏幕显示屏由16×32个的16×32点阵屏级联而成。为了缩短控制系统到屏体的信号传输时间,将显示数据分

为16个区,每个区由16×1024点阵组成,每行数据为1024/8=128字节,显示屏的像素信号由LED显示屏的右侧向左侧传输移

位,把16个分区的数据存在同一块存储器。一屏的显示数据为32 KB,要准确读出16个分区的数据,其存储器的读地址由16

位组成,由于数据只有32 KB,因此可置为0。其余15位地址从高到低依次为:行地址(4位)、列地址(7位)、分区地址

(4位)。4位分区地址的译码信号(Y0~Y15)作为锁存器的锁存脉冲,在16个读地址发生周期内,依次将第1~16分区的第

1字节数据锁存到相应的锁存器,然后在移位锁存信号上升沿将该16字节数据同时锁存入16个8位并转串移位寄存器组中。在

下一个16个读地址发生时钟周期,一方面,并转串移位寄存器将8位数据移位串行输出,移位时钟为读地址发生时钟的二分

频;另一方面,依次将16个分区的第2字节数据读出并锁入相应的锁存器,按照这种规律将所有分区的行数据依次全部读出

后,在数据有效脉冲信号的上升沿将所有串行移位数据输出,驱动LED显示。接下来,移位输出第2行的数据,在此期间第1

行保持显示;第2行全部移入后,驱动第2行显示,同时移入第3行……按照这种各分区分行扫描的方式完成整个LED大屏幕的

扫描显示。

3 基于基于FPGA显示屏控制器的设计显示屏控制器的设计

3.1 FPGA控制模块总体方案控制模块总体方案

资源评论

weixin_38747216

- 粉丝: 5

- 资源: 882

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功