资深工程师电源设计策略:如何避免传导 EMI问题.docx

需积分: 0 60 浏览量

更新于2019-09-13

收藏 622KB DOCX 举报

在电源设计中,传导电磁干扰(EMI)是一个常见的问题,尤其对于资深工程师而言,理解和解决这个问题至关重要。本文主要探讨如何避免由共模噪声引起的传导 EMI 问题,这种噪声通常源于电源中的寄生电容。

我们要理解共模噪声的来源。共模噪声是由在电源线两端同时存在的相同方向的电流引起的,这些电流会在电源线中产生磁场,进而形成EMI。寄生电容,即非设计意图的电容,是导致共模噪声的关键因素。哪怕只有几飞法拉(fF)的寄生电容,也可能导致EMI测试不达标。这是因为开关电源在工作过程中,某些节点会产生高dV/dt(电压变化率),这样的节点与寄生电容结合,会生成噪声电流,直接注入电源线。

为了解决这个问题,我们需要关注电源设计中的关键环节:

1. 寻找并评估寄生电容:检查电路中所有节点,特别是那些dV/dt高的位置,如开关MOSFET的漏极和缓冲电路。理解这些节点的表面积和它们与电源输入线的距离,这两者都会影响寄生电容的大小。

2. 减小表面面积:采用表面贴装器件可以有效减小寄生电容。例如,TO-220封装的FET通常具有较大的漏极选项卡,增加表面积,而DPAK或D2PAK封装的FET则能提供更好的屏蔽效果。如果必须使用带散热片的TO-220 FET,尝试将其连接到初级接地,而不是大地接地,这样可以降低杂散电容并提高屏蔽效果。

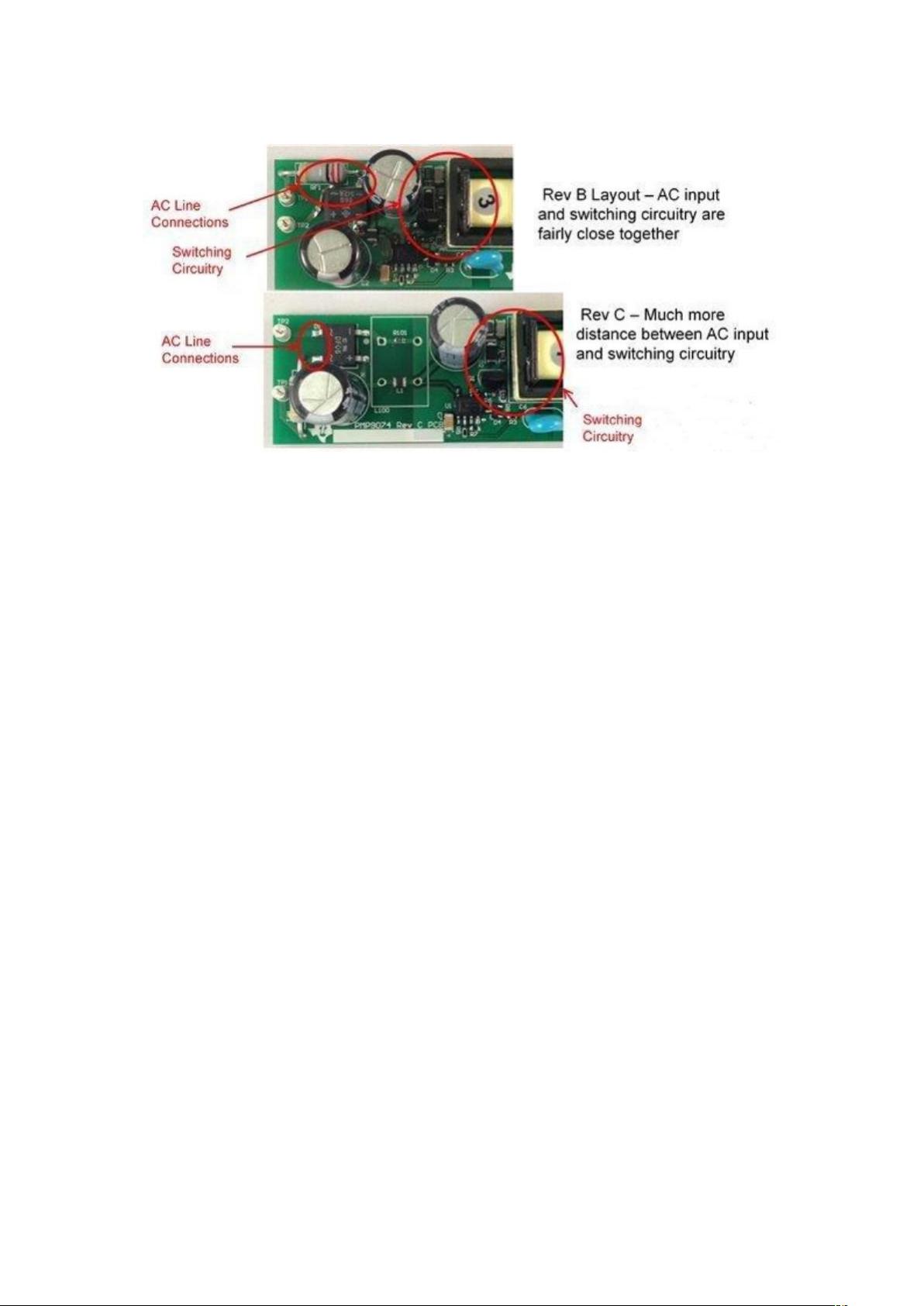

3. 布局优化:确保开关节点与输入连接保持足够的距离,避免高dV/dt的节点与输入线过近,如图1所示。适当调整电路板布局,如图2和图3的对比,可以显著降低EMI水平。

4. 检查输入滤波器的效果:有时,即使加强了输入滤波器,EMI改善效果仍不明显,这可能是因为寄生电容直接耦合到输入线,绕过了共模扼流圈(CMC)。在这种情况下,可以通过临时短路CMC的绕组,用二级CMC串联于输入线来检测问题。如果改善明显,那么需要重新设计电路板,特别是在输入连接的布局和布线上。

避免传导EMI的关键在于理解和控制电源设计中的寄生电容。通过细致的电路分析、器件选择、布局优化以及滤波器设计,资深工程师能够有效地抑制共模噪声,提高电源系统的电磁兼容性。在实际操作中,每一步都需要谨慎处理,以确保电源设计的稳定性与可靠性。

weixin_38743481

- 粉丝: 698

- 资源: 4万+

最新资源

- 电子商务_网上商城管理系统_用户身份验证_便捷购物_1740825436.zip

- 商城管理_System_SCUM_1740825333.zip

- 智能公交系统电子站牌设计_STM32_微信小程序_毕业设_1740825532.zip

- 全国地图 省GeoJson 市GeoJson

- MATLAB实现领航追随法与人工势场法融合的车辆编队避障控制策略,MATLAB领航追随法融合人工势场法的车辆编队避障控制策略实现研究,MATLAB基于领航追随法的车辆编队控制,领航追随者与人工势场法的

- 迪恩在线教育素材培训课程网站源码 discuz内核完整资料带数据

- 基于手性光学效应的连续介质束缚态研究:从三维图谱到Q因子图的所见即所得超表面复现分析,基于Comsol模拟:三次谐波效应下的本征手性BIC超表面研究-远场偏振图、手性透射曲线与光学响应的可见性分析

- 和材料性能分析** COMSOL 培训视频,深入解析多物理场仿真技术与应用 **深入解析COMSOL多物理场仿真技术与应用:从结构力学到化学反应的全面分析**,界面仿真和流控模拟 COMSO

- 找高手:应该如何训练工程造价的大模型?

- NOIP2009年提高组NOI Linux和Cena测评环境与数据

- 手把手项目实践:用Labview制作一个电子秤的485上位程序

- golang画图库演示程序源码

- IntelCacheAccelerationSoftware,傲腾加速软件

- 昆仑通态MCGS与欧姆龙E5CC温控器通讯:PID控制及输出启停功能实现,欧姆龙E5CC温控器与昆仑通态MCGS的PID通讯方式及输出启停(KUNL-1),昆仑通态MCGS与欧姆龙E5CC温控器通讯+

- 补码计算与进制转码学习

- 《从0到1:手把手教你OpenCV下载安装秘籍》