嵌入式系统/ARM技术中的嵌入式系统中可配置式GPIO模拟SPI总线方法

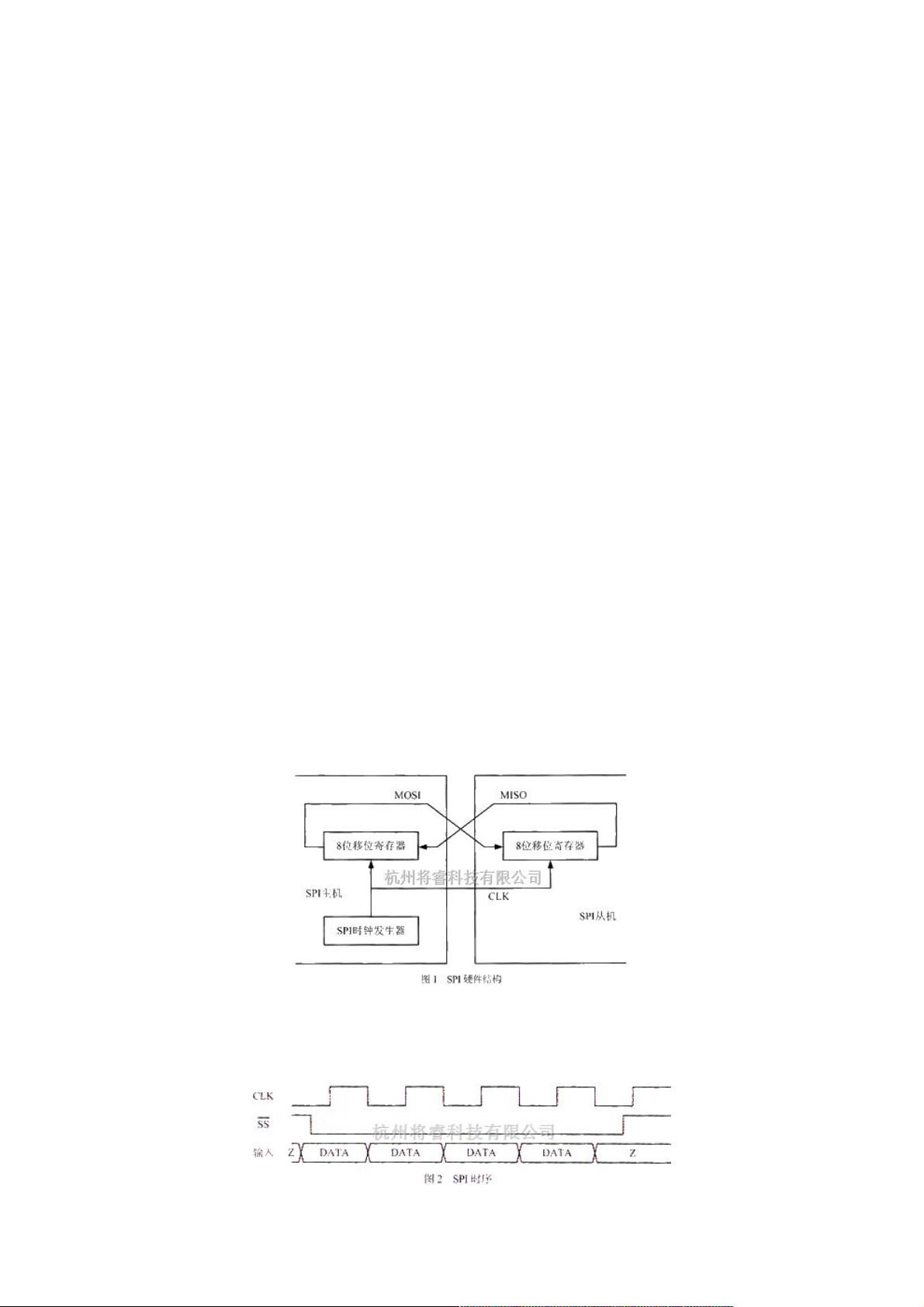

在嵌入式系统处理器中有相当一部分处理器不带SPI接口,但基丁SPI接口的设备非常丰富,此外,SPI设备的不同以及处理器对GPIO口位寻址是否支持各处理器各有不同,因而不同处理器中软件模拟GPIO也各不相同。若能提供一种通用可配置可移植的GPIO模拟SPI总线的驱动则能很方便快捷的访问SPI设备,从而提高整个嵌入式系统的开发效率。本文针对GPIO口位寻址与否给出方面,给出了一种可配置GPIO模拟SPI总线的方法并详细介绍了其设计与实现过程,且具有代码小可移植性强使用方便等特点。 1 GPIO规范 SPI是一个全双工的串行接口。它设计成可以在一个给定总线上处理多个互联的主机和从机。在一定数据 嵌入式系统中,GPIO(General Purpose Input/Output)接口是一种通用输入输出接口,常用于控制硬件设备的状态。在某些嵌入式处理器中,可能并未集成SPI(Serial Peripheral Interface)接口,但SPI接口因其简单高效,被广泛应用于各种外设如传感器、存储器等。为了在不带SPI接口的处理器上也能使用SPI设备,就需要通过软件模拟SPI总线,即通过GPIO口模拟SPI的通信协议。 SPI是一个全双工的串行通信接口,允许一个主机和多个从机在同一总线上进行通信。在一次通信中,主机向从机发送数据,从机也会回传数据。SPI接口通常包括四个信号线:时钟(SCLK)、主输出从机输入(MOSI)、主输入从机输出(MISO)和从机选择(SS)。在特定的时钟边沿(上升沿或下降沿),数据会被读取或写入。 在GPIO模拟SPI的过程中,由于不同的处理器对GPIO口位寻址的支持程度不同,模拟方法也会有所差异。因此,设计一个可配置、可移植的GPIO模拟SPI驱动显得尤为重要。这样的驱动能够灵活适应不同的处理器环境,简化代码的移植工作,提高开发效率。 为了实现GPIO模拟SPI,首先要理解SPI的硬件结构和时序。SPI硬件通常包含两个移位寄存器,数据在主设备产生的时钟脉冲下逐位传输。SPI的时序要求数据在SCLK的下降沿变化,并将数据送入移位寄存器。在写入过程中,可以采用掩码方式实现对GPIO位的控制。 在实现过程中,需要对GPIO进行配置,根据处理器特性定义GPIO接口对应于SPI的方式。这部分工作通常在头文件如`SPIHARD.H`中进行。代码实现应确保与GPIO口寻址方式无关,以增强其可移植性。例如,对于支持位寻址和不支持位寻址的GPIO端口,可以通过宏定义或者条件编译来适应不同的处理器。 在实际应用中,这种GPIO模拟SPI的方法已经在Epson S1C33L11、AT89C52、SPCE061A和Philips ARM LPC2106等多种处理器平台上得到了验证,证明了其代码量小、可移植性强和使用方便的特点。 通过GPIO模拟SPI总线,可以克服处理器无内置SPI接口的限制,充分利用丰富的SPI设备资源。这种方法降低了对硬件的依赖,提高了软件的灵活性,使得开发者能够在各种嵌入式系统中更便捷地接入和控制SPI设备,从而优化系统设计,提升整体性能。

- 粉丝: 7

- 资源: 925

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论0