没有合适的资源?快使用搜索试试~ 我知道了~

EDA/PLD中的基于FPGA的FIFO设计和应用

0 下载量 182 浏览量

2020-11-09

18:11:01

上传

评论

收藏 203KB PDF 举报

温馨提示

引 言 在利用DSP实现视频实时跟踪时,需要进行大量高速的图像采集。而DSP本身自带的FIFO并不足以支持系统中大量数据的暂时存储,这就要求大的中间缓存,而专用的高速FIFO芯片价格昂贵且容量受限,大大增加了商业成本,因此在实际应用中寻找FIFO代替器件是很有必要的。 1 器件选择 这里在视频信号处理系统中,将利用FPGA作为桥梁,实现对SDRAM的控制,以达到大量高速存取数据的功能。之所以选取SDRAM,主要是因为在各种随机存取器件中,SDRAM的容量较大,价格较低,且数据突发传输模式大大提高了存取速度,能够满足应用的要求。 FIFO的速度受到两个因素的限制:

资源推荐

资源详情

资源评论

EDA/PLD中的基于中的基于FPGA的的FIFO设计和应用设计和应用

引 言 在利用DSP实现视频实时跟踪时,需要进行大量高速的图像采集。而DSP本身自带的FIFO并不足以

支持系统中大量数据的暂时存储,这就要求大的中间缓存,而专用的高速FIFO芯片价格昂贵且容量受限,大大

增加了商业成本,因此在实际应用中寻找FIFO代替器件是很有必要的。 1 器件选择 这里在视频信号处

理系统中,将利用FPGA作为桥梁,实现对SDRAM的控制,以达到大量高速存取数据的功能。之所以选取

SDRAM,主要是因为在各种随机存取器件中,SDRAM的容量较大,价格较低,且数据突发传输模式大大提高

了存取速度,能够满足应用的要求。 FIFO的速度受到两个因素的限制:

引 言

在利用DSP实现视频实时跟踪时,需要进行大量高速的图像采集。而DSP本身自带的FIFO并不足以支持系统中大量数据

的暂时存储,这就要求大的中间缓存,而专用的高速FIFO芯片价格昂贵且容量受限,大大增加了商业成本,因此在实际应用

中寻找FIFO代替器件是很有必要的。

1 器件选择

这里在视频信号处理系统中,将利用FPGA作为桥梁,实现对SDRAM的控制,以达到大量高速存取数据的功能。之所以

选取SDRAM,主要是因为在各种随机存取器件中,SDRAM的容量较大,价格较低,且数据突发传输模式大大提高了存取速

度,能够满足应用的要求。

FIFO的速度受到两个因素的限制:

(1)SDRAM的最高工作频率。SDRAM的工作频率越高,数据的传输速率就越高;

(2)SDRAM的突发长度。SDRAM的突发长度越长,对数据流的吞吐量就越大,可以从某种程度上提高数据的传输速率。

FIFO的大小由所选SDRAM芯片的容量来决定。该设计以采用MICRON公司的MT48LC4M3282(4 BANK×4M×32 b)为

例,存储容量为128 Mb,数据带宽为32位,内部由4个BANK组成,每个BANK有4 096行和256列。

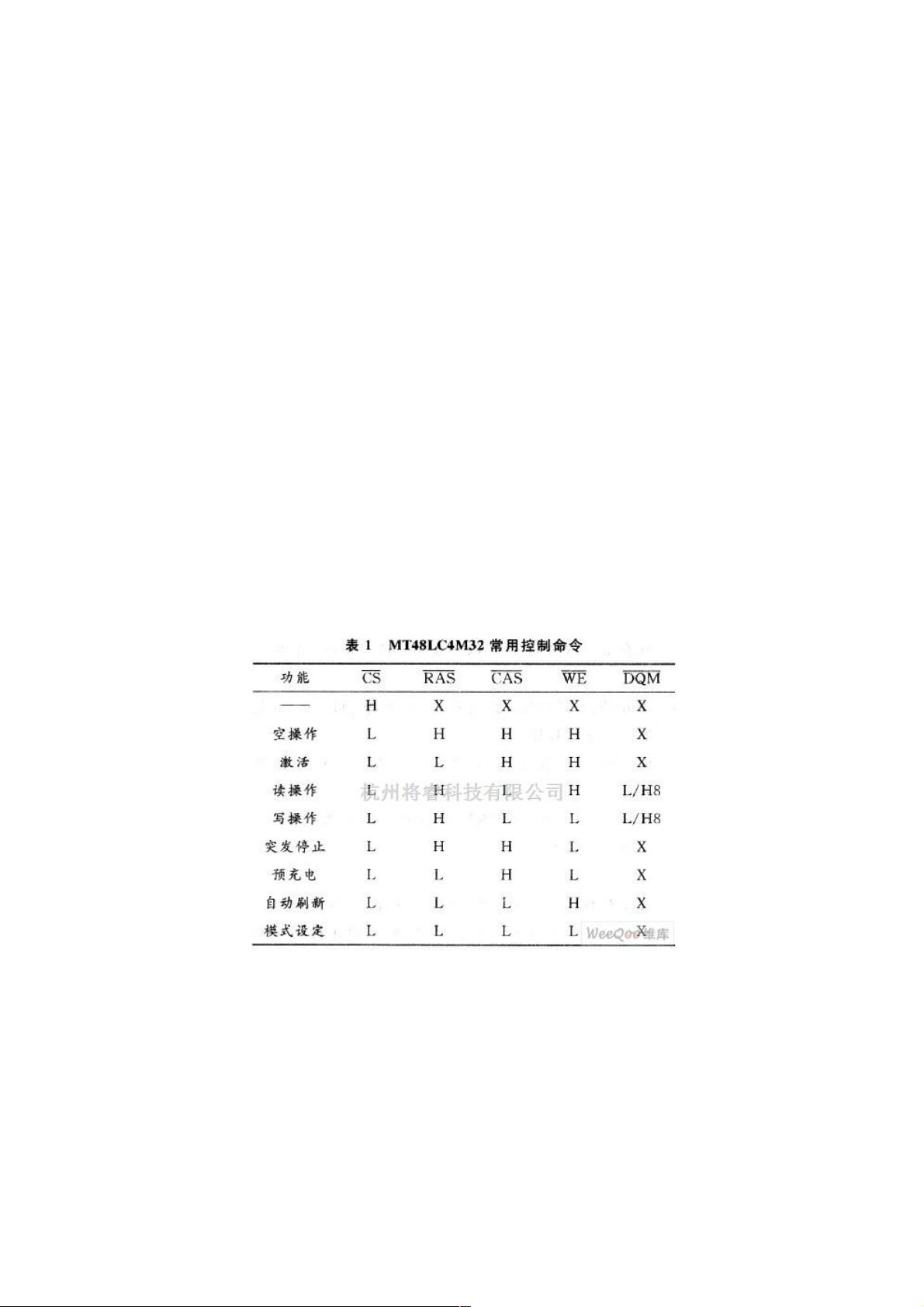

MT48LC4M3282的控制信号有CLK(时钟信号)、CKE(时钟使能)、CS(片选信号)、WE(写使能)、CAS(列有效)、RAS(行

有效)、DQM0~DQM3(输入输出使能)。控制信号组成的常用控制命令如表1所示。

2 FIFO系统设计

FIFO系统由FGPA和SDRAM两部分组成。其中,FGPA内部包含FIFO.、缓冲器、SDRAM控制器三个模块。FIFO.的作

用是将FIFO的状态转变成状态机的读、写信号。若操作为向SDRAM写数据,则在FIFO已满时,FIFO.送出一个信号,以阻止

写操作继续向FIFO中写数据而造成溢出;若操作为向SDRAM读数据,则在缓冲器已空时,FIFO.送出一个信号,以阻止读操

作继续从FIFO中读数据而造成无效数据的读出。FIFO的模块结构如图1所示。

资源评论

weixin_38729399

- 粉丝: 7

- 资源: 902

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Java语言实现养老院信息管理系统(SQL Server数据库)

- 社区居民诊疗健康-JAVA-基于SpringBoot的社区居民诊疗健康管理系统设计与实现(毕业论文)

- ChromeSetup.zip

- 大黄蜂V14旋翼机3D

- 体育购物商城-JAVA-基于springboot的体育购物商城设计与实现(毕业论文)

- 三保一评关系与区别分析

- 星形发动机3D 星形发动机

- 机考样例(学生).zip

- Day-05 Vue22222222222

- 经过数据增强后番茄叶片病害识别,约45000张数据,已标注

- 商用密码技术及产品介绍

- CC2530无线zigbee裸机代码实现WIFI ESP8266上传数据到服务器.zip

- 文物管理系统-JAVA-基于springboot的文物管理系统的设计与实现(毕业论文)

- 店铺数据采集系统项目全套技术资料.zip

- 数据安全基础介绍;数据安全概念

- 目标检测数据集: 果树上的tomato西红柿图像检测数据【VOC标注格式、包含数据和标签】

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功