没有合适的资源?快使用搜索试试~ 我知道了~

嵌入式系统/ARM技术中的基于嵌入式系统内存规划方法的研究

0 下载量 56 浏览量

2020-11-10

21:38:04

上传

评论

收藏 171KB PDF 举报

温馨提示

摘 要: 内存访问延迟是嵌入式系统性能提高的瓶颈。本文以数据在内存的存储方式为出发点来解决内存访问延迟的问题,并用遗传算法实现了优化算法。 针对有内存管理单元(MMU)的处理器设计的一些桌面操作系统(如Windows、Linux)都使用了虚拟存储器的概念,虚拟内存地址被送到MMU。在这里,虚拟地址被映射为物理地址,实际存储器被分割为相同大小的页面,采用分页的方式载入进程。一个程序在运行之前,没有必要全部装入内存,而是仅将那些当前要运行的部分页面装入内存运行。大多数嵌入式系统是针对没有MMU的处理器设计的,因此不能使用处理器的虚拟内存管理技术,而采用实存储管理策略,从而对内存的访问是直接

资源推荐

资源详情

资源评论

嵌入式系统嵌入式系统/ARM技术中的基于嵌入式系统内存规划方法的研技术中的基于嵌入式系统内存规划方法的研

究究

摘 要: 内存访问延迟是嵌入式系统性能提高的瓶颈。本文以数据在内存的存储方式为出发点来解决内存访问延

迟的问题,并用遗传算法实现了优化算法。 针对有内存管理单元(MMU)的处理器设计的一些桌面操作系

统(如Windows、Linux)都使用了虚拟存储器的概念,虚拟内存地址被送到MMU。在这里,虚拟地址被映射为物

理地址,实际存储器被分割为相同大小的页面,采用分页的方式载入进程。一个程序在运行之前,没有必要全

部装入内存,而是仅将那些当前要运行的部分页面装入内存运行。大多数嵌入式系统是针对没有MMU的处理器

设计的,因此不能使用处理器的虚拟内存管理技术,而采用实存储管理策略,从而对内存的访问是直接

摘 要: 内存访问延迟是嵌入式系统性能提高的瓶颈。本文以数据在内存的存储方式为出发点来解决内存访问延迟的问

题,并用遗传算法实现了优化算法。

针对有内存管理单元(MMU)的处理器设计的一些桌面操作系统(如Windows、Linux)都使用了虚拟存储器的概念,虚拟

内存地址被送到MMU。在这里,虚拟地址被映射为物理地址,实际存储器被分割为相同大小的页面,采用分页的方式载入进

程。一个程序在运行之前,没有必要全部装入内存,而是仅将那些当前要运行的部分页面装入内存运行。大多数嵌入式系统是

针对没有MMU的处理器设计的,因此不能使用处理器的虚拟内存管理技术,而采用实存储管理策略,从而对内存的访问是直

接的。它对地址的访问不需要经过MMU,而是直接送到地址线上输出,所有程序中访问的地址都是实际的物理地址。而且,

大多数嵌入式操作系统对内存没有保护,各个进程实际上共享一个运行空间。一个进程在执行前,系统必须为它分配足够的连

续地址空间,然后全部载入主存储的连续空间。从编译内核开始,开发人员必须告诉系统,这块开发板到底拥有多少内存;在

开发程序时,必须考虑内存的分配情况并关注应用程序需要运行空间的大小。另外,由于采用实存储器管理策略,用户程序同

内核以及其他用户程序在一个地址空间,程序开发时要保证不侵犯其他应用程序的地址空间,不破坏系统的正常工作,使程序

正常运行。因而对内存操作要格外小心。由此可见,开发者不得不参与系统的内存管理,否则系统的效率和性能都不能令人满

意。开发者可以用一个内存管理器来帮助管理内存,可以借鉴流行操作系统对内存池(pool)中块(block)进行管理的思

想。访问时先寻找对应的块,然后对物理地址进行页的解码,进而是行解码,最后是列解码和根据图像处理系统处理大量数据

的特点,对数据在内存中的布局进行规划。即同一块中使连续访问的数据在同一页;在同一页的数据,尽量安排在同一行,减

小内存访问延迟,以便对性能进行改善。同时,内存块间相对位置也用同样的方法进行规划,使得块间的转换也尽快完成。本

文采用遗传算法,同时对内存数据存储进行页、行、列的规划,对块间相对位置也进行了规划。

1 内存规划

流行的操作系统对内存访问的基本方式是支持快速缓存,执行的过程是把要访问的地址整行拷贝到缓存区,先进行页解码

和行解码,然后进行列解码并根据读写信号进行选择。目前嵌入式系统中使用的DRAMs都支持高效内存访问模式,还特别支

持流行的页(page)访问模式和区间(burst)访问模式(相当于以列为主的访问)。这种访问模式消耗的能量低于随机访问方式,

例如,IBM′s Cu-11 Embedded DRAM macro支持的随机访问时间是10ns,而块中页访问的时间是5ns,电流分别是

60mA/MB和13mA/MB。所以,充分利用内存访问模式的特点可以改变嵌入式系统的性能。

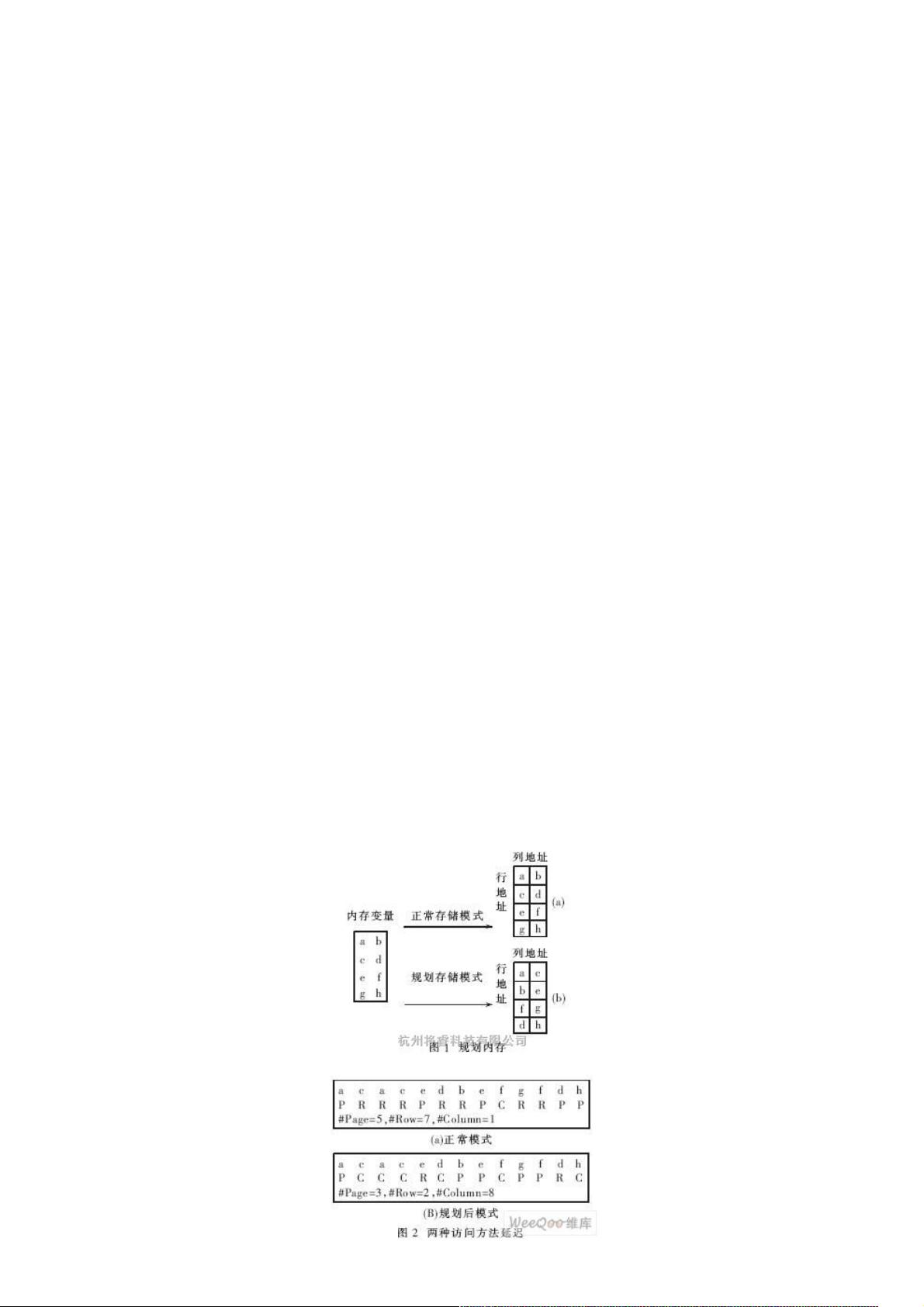

为了说明本文的规划思想,假设内存中有如图1所示的变量a,b,c,d,e,f,g,h。若要访问内存中变量的次序为

acacebdbefgfdah,则根据图1中内存存放的次序,可以计算出访问延迟的时间。如果页间访问延迟时间是5个时钟周期,记为

Delay(P)=5cycles,则在同页中行间访问延迟Delay(R)=3cycles,同行中列间访问延迟Delay(C)=1cycles。根据图1(a)和图

1(b)中两种存储模式,可以分别计算出如图2所示的两种内存存储方式下内存访问延迟时间:

Latency(a)=47cycles,Latency(b)=29cycles。

资源评论

weixin_38689736

- 粉丝: 5

- 资源: 931

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功