3310 IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 24, NO. 11, NOVEMBER 2016

Alleviating Through-Silicon-Via Electromigration

for 3-D Integrated Circuits Taking Advantage

of Self-Healing Effect

Yuanqing Cheng, Member, IEEE, Aida Todri-Sanial, Member, IEEE, Jianlei Yang, Member, IEEE,

and Weisheng Zhao, Senior Member, IEEE

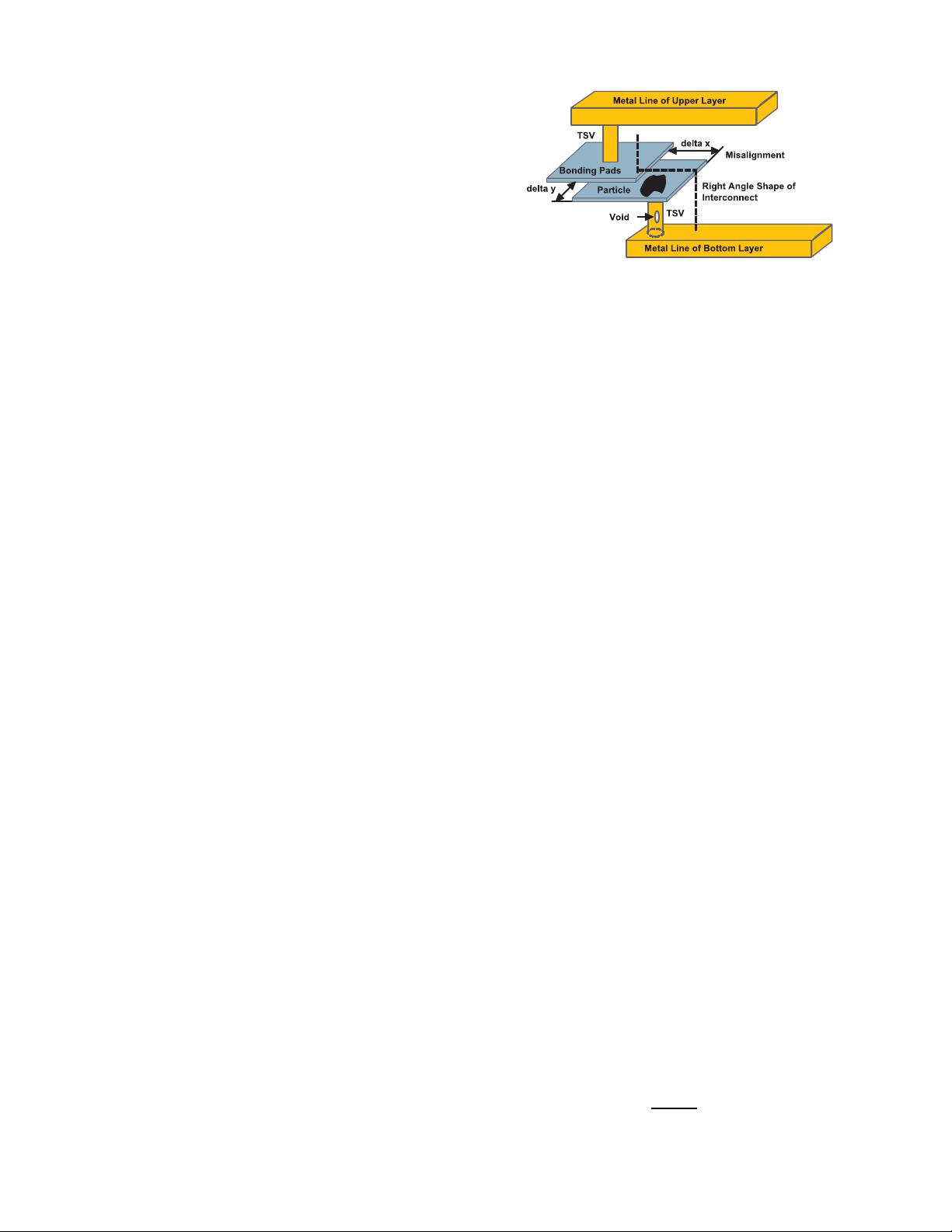

Abstract—Three-dimensional integration is considered to be

a promising technology to tackle the global interconnect scaling

problem for terascale integrated circuits (ICs). Three-dimensional

ICs typically employ through-silicon-vias (TSVs) to vertically

connect planar circuits. Due to its immature fabrication process,

several defects, such as void, misalignment, and dust contamina-

tion, may be introduced. These defects can significantly increase

current densities within TSVs and cause severe electromigra-

tion (EM) effects, which can degrade the reliability of 3-D ICs

considerably. In this paper, we propose an effective framework

to mitigate EM effect of the defective TSV. At first, we analyze

various possible TSV defects and their impacts on EM reliability.

Based on the observation that EM can be significantly alleviated

by self-healing effect, we design an EM mitigation module to

protect defective TSVs from EM. To guarantee EM mitigation

efficiency, we propose two defective TSV protection schemes,

i.e., neighbor sharing and global sharing. Experimental results

show that the global-sharing scheme performs the best and

can improve the EM mean time to failure by more than 70×

on average with only 0.7% area overhead and less than 0.5%

performance degradation compared with naked design without

any EM protection.

Index Terms—3-D integrated circuits (ICs), electro

migration (EM), reliability, self-healing effect, through-

silicon-via (TSV).

I. INTRODUCTION

W

ITH the continuous technology scaling, chip integra-

tion density keeps on increasing sharply. Billions of

transistors can be built within a single chip. As a consequence,

power consumption on chip also rockets up. At the same time,

supply voltage decreases gradually for each technology gener-

ation. Thus, current density on chip elevates fast. High current

Manuscript received September 8, 2015; revised December 21, 2015

and January 31, 2016; accepted March 9, 2016. Date of publication

April 20, 2016; date of current version October 21, 2016. This work

was supported in part by the Beijing Natural Science Foundation under

Grant 4154076, in part by the Beijing Municipal of Science and Technology

under Grant D15110300320000, and in part by the National Natural Science

Foundation of China under Grant 61401008.

Y. Cheng and W. Zhao are with the School of Electrical and Infor-

mation Engineering, Beihang University, Beijing 100191, China (e-mail:

yuanqing@ieee.org; weisheng.zhao@buaa.edu.cn).

A. Todri-Sanial is with the Laboratoire d’Informatique, de Robotique

et de Microélectronique de Montpellier, Centre National de la Recherche

Scientifique, University of Montpellier, Montpellier 34095, France (e-mail:

aida.todri@lirmm.fr).

J. Yang is with the Electrical and Computer Engineering Department,

University of Pittsburgh, Pittsburgh, PA 15260 USA (e-mail: jiy64@pitt.edu).

Color versions of one or more of the figures in this paper are available

online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2016.2543260

density may induce significant electromigration (EM) effect,

which severely threatens the chip operation reliability [1], [2].

EM is caused by mass transport within metal interconnects.

When current flows in the metal line, electrons collide with

metal atoms and drag them away from their original positions.

As a result, voids generate within the region where metal

atoms are dragged away while hillocks form where they

aggregate together. Void introduces open defect and hillock

causes short with the neighboring interconnects.

For traditional metal interconnects, the following equation

is usually used for the estimation of interconnect mean time

to failure (MTTF) due to EM [1]:

MTTF = A · J

−n

· e

Q

k·T

(1)

where A is a constant, depending on the interconnect fabri-

cation technology, J is the interconnect current density, Q is

the activation energy for EM, k is the Boltzmann constant,

and T is the temperature in Kelvin. As the technology node

enters a deep submicrometer regime, EM is becoming a severe

challenge for VLSI designers due to the rocketing up current

density.

On the other hand, as semiconductor feature size

continues to shrink, global interconnects become major per-

formance bottlenecks as they cannot scale at the same

rate as transistors. The recently widely investigated 3-D

integration is considered to be one of the most promising

techniques to mitigate the above problem [3]. By stacking

planar dies and connecting them with vertical through-silicon-

vias (TSVs), the chip performance and form factor can be

improved dramatically [4], [5]. Furthermore, 3-D integrated

circuits (ICs) enable disparate technologies, such as phase

change random access memory, magnetic random access mem-

ory, and CMOS, to be integrated together without changing the

fabrication process a lot [6], [7].

However, 3-D ICs also face several challenging issues.

Among them, EM occurrence on a TSV threatens the reli-

ability of 3-D ICs [8], [9]. It is caused by several factors.

First, due to mismatch of thermal coefficients of a TSV

filling material (e.g., copper) and surrounding oxide layer,

TSVs may suffer from stress and strain and break down

during repetitive thermal cycling [8]. Second, current densities

of 3-D ICs are much larger than their 2-D counterparts as

integration density and power consumption increase [10]. High

current density imposes high current flows in TSVs, which

1063-8210 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications_standards/publications/rights/index.html for more information.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功