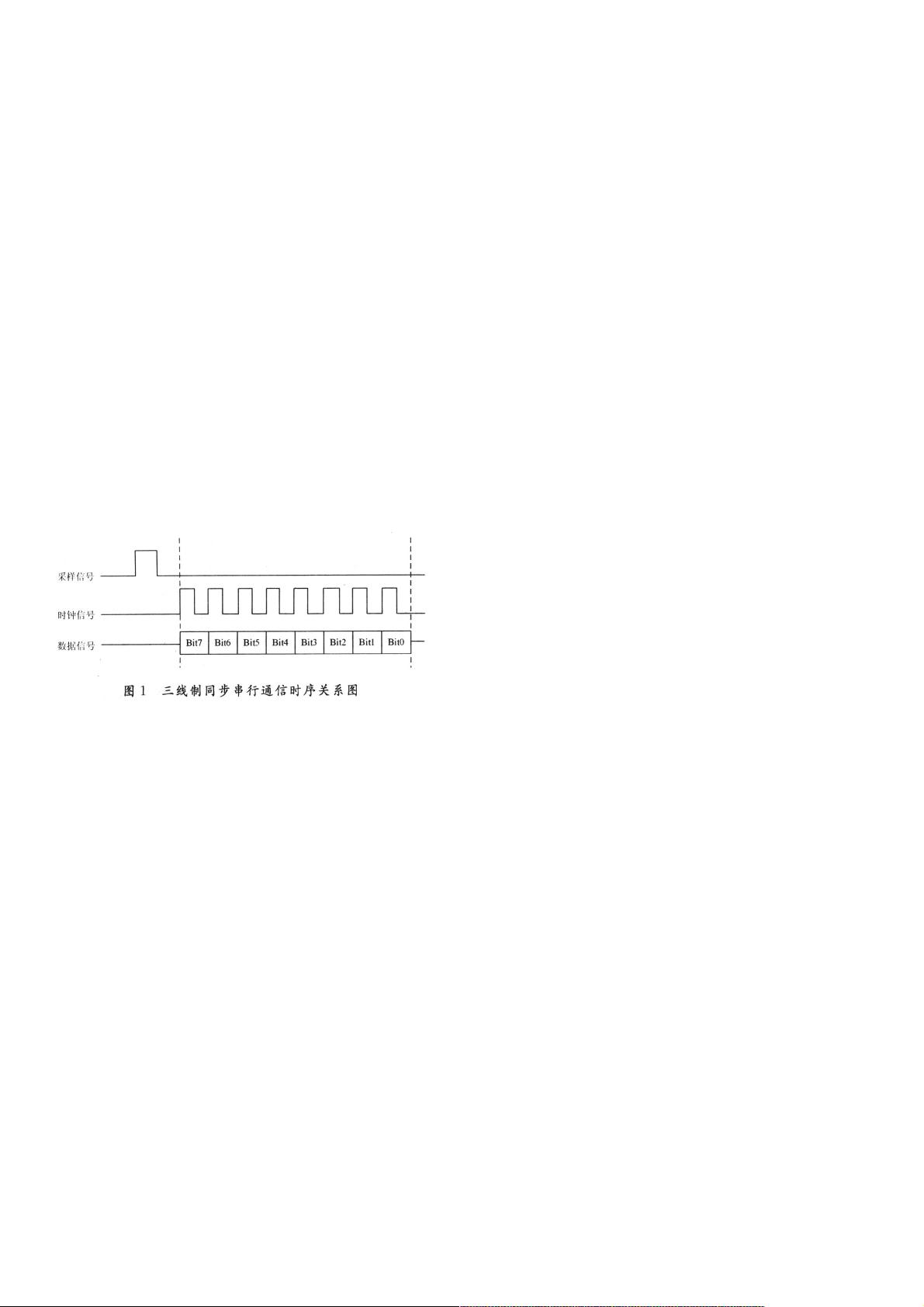

本文在介绍了三线制同步串行通信机制基础上,首先对三线制同步串行通信接口进行了硬件电路设计,然后针对传统电路设计方式的不足,构建了基于CPLD/FPGA的三线制同步串行通信控制器接口结构,详述了各个功能模块及其工作原理,设计合理,并且满足了实际应用要求。 《三线制同步串行通信控制器接口设计》 在当今的通信领域,高效、可靠的通信方式至关重要,尤其是在航天工程中的星地通讯等远距离遥测遥控应用中。三线制同步串行通信作为一种重要的通信机制,因其简洁的硬件结构和较高的通信效率而被广泛采用。然而,传统的三线制同步串行通信接口设计存在诸如元器件数量多、体积大、功耗高等问题,无法满足现代嵌入式系统对于“低成本、小体积、低功耗和灵活性”的设计需求。 本文首先阐述了三线制同步串行通信的基本原理,这种通信方式依赖于共享的时钟源以确保发送端和接收端之间的精确同步。在数据传输过程中,通常采用编码解码技术,如曼彻斯特编码或NRZ-L码,以确保数据的准确无误。NRZ-L码是本文中所采用的码型,其特点是数据信号的高低电平直接表示二进制的0和1。三线制同步串行通信涉及三个关键信号:帧同步信号、时钟信号和串行数据信号。帧同步信号先触发数据传输,接着是时钟信号,数据则在时钟的上升沿被采样和传输。 传统的三线制同步串行通信控制器接口设计通常需要包括计数器、移位寄存器、触发器以及各种门电路。接收接口通过计数器进行数据串并转换,利用D触发器存储数据,中断信号通知微处理器接收。而发送接口则通过分频产生发送时钟,D触发器锁存数据,移位寄存器完成并串转换,并通过单向总线驱动器发送数据。 为了解决传统设计的不足,本文提出了基于CPLD(复杂可编程逻辑器件)/FPGA(现场可编程门阵列)的三线制同步串行通信控制器接口结构。这种设计大大减少了硬件元器件的数量,降低了功耗,同时也提高了设计的灵活性。整个接口由四个主要模块组成:时钟分频模块、系统接口控制逻辑、数据接收模块和数据发送模块。时钟分频模块生成所需时钟信号,系统接口控制逻辑负责逻辑控制信号的处理和中断管理,数据接收模块完成串行数据到并行数据的转换并存储,而数据发送模块则执行相反的操作,将并行数据转化为串行数据进行发送。 在CPLD/FPGA的设计中,VHDL硬件描述语言被用来实现这些功能模块,使得设计更加灵活,易于修改和扩展。例如,数据接收模块中的接收FIFO(先进先出缓冲区)可以有效地缓冲接收到的数据,当缓冲区满时,会向系统发出接收完成的信号。这样,通过CPLD/FPGA的设计,不仅可以优化硬件资源,还可以方便地集成其他逻辑功能,更好地适应嵌入式系统的复杂需求。 本文提出的基于CPLD/FPGA的三线制同步串行通信控制器接口设计,不仅克服了传统设计的缺点,还提升了通信系统的整体性能。这一创新设计为未来通信系统的小型化、低功耗和高效能提供了新的解决方案,具有广泛的实践意义和理论价值。

- 粉丝: 5

- 资源: 896

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功