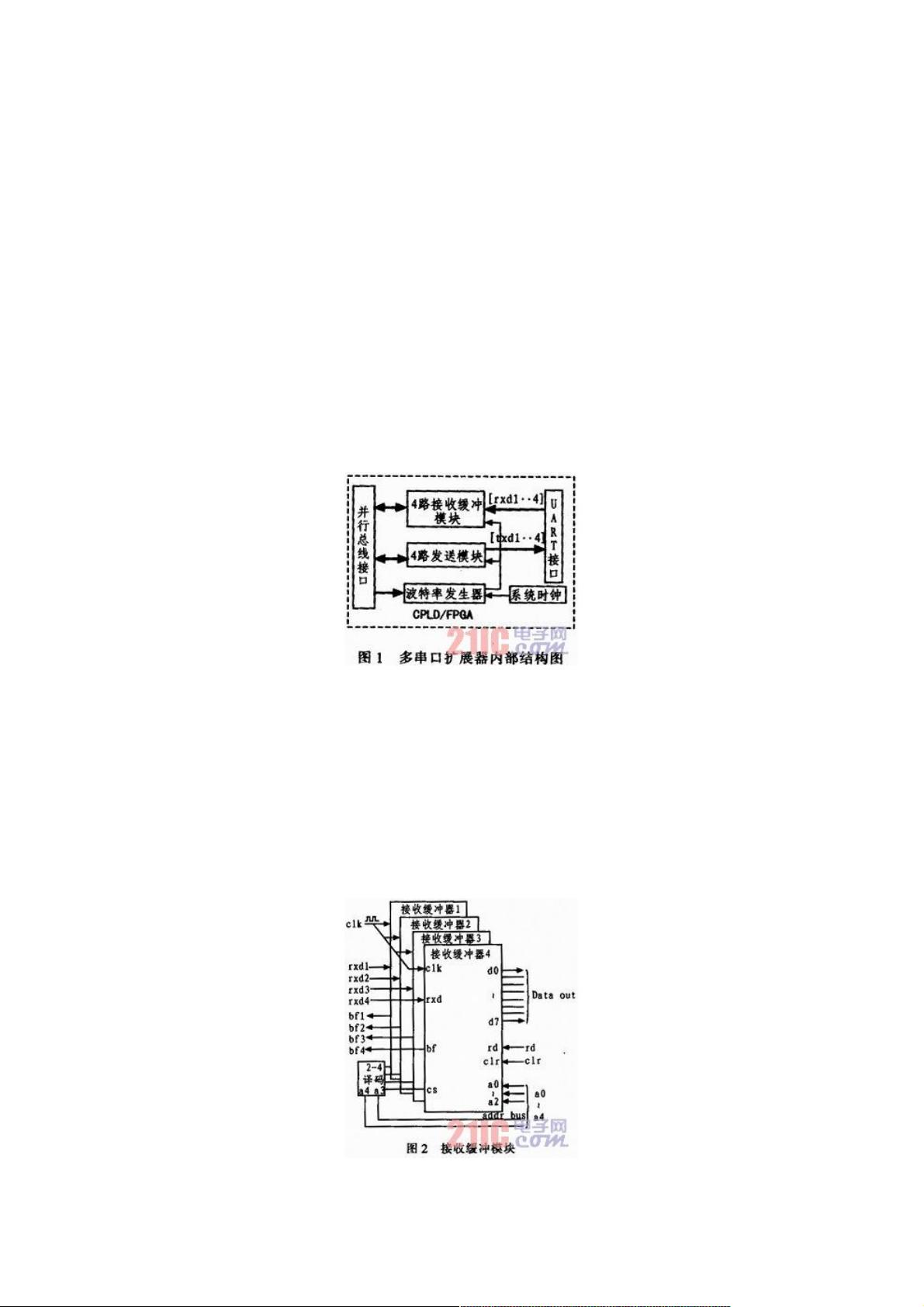

在工业控制中如何提高一对多的串口通讯可靠性和系统的集成性成为研究热点。本文利用嵌入式技术,提出基于CPLD/FPGA的多串口扩展设计方案。实现并行口到多个全双工异步通讯口之间的转换,并根据嵌入式系统实时性的需要,在每个UART接收器中开辟了8个接收缓冲单元,实现高速嵌入式CPU与RS232通讯设备之间的速度匹配,同时,串行口波特率等参数可根据需要进行设置。通过实践证明,本文设计的基于CPLD/FPGA的多串口完全符合工业控制中一对多串口通讯的要求。 在工业控制系统中,串口通信由于其简单、高效的特点,被广泛应用。然而,随着设备数量的增加,如何实现一对多的串口通讯并确保可靠性,同时提升系统的集成性,成为了研究的重点。为解决这一问题,本文提出了基于CPLD(复杂可编程逻辑器件)/FPGA(现场可编程门阵列)的多串口扩展设计方案。 CPLD/FPGA是现代电子设计中常用的两种可编程逻辑器件。CPLD通常用于实现中等规模的逻辑功能,而FPGA则适用于大规模的并行处理和定制化硬件加速。在本文的设计中,这两种器件结合使用,可以实现并行总线到多个串行口的转换,有效扩展了串口数量,满足了工业控制中一对多的通讯需求。 系统设计的核心在于CPLD/FPGA芯片,通过内部的逻辑编程,构建了包括并行总线接口、多个接收缓冲器、多个发送器、波特率发生器以及UART(通用异步接收发送器)接口的架构。其中,接收缓冲器是关键组件,它能够存储来自串行设备的数据,实现高速嵌入式CPU与RS232设备之间的速度匹配。每个接收缓冲器都包含8个接收缓冲单元,可以根据实时性需求进行调整,以适应不同速度的通讯设备。 接收缓冲模块由RXD接收器、地址及写控制器和双端口RAM组成。RXD接收器负责接收串行数据,通过检测rxd脚的电平变化来开始接收,并将数据存储到双端口RAM中。写控制器则根据接收到的负脉冲信号更新地址寄存器,并触发写操作,将数据写入RAM。双端口RAM允许在读写操作的同时访问,保证了数据的连续传输。 发送模块由TXD发送器、2-4译码器和4输入或门构成,用于发送数据到串行设备。TXD发送器共享相同的时钟和数据端口,通过译码器和或门进行地址选择和状态标志的生成,实现数据的同步发送。 此外,波特率发生器可以根据需要设定串行口的波特率,提供灵活的数据传输速率配置。这不仅提高了系统的兼容性,也增强了系统的适应性,能够在各种不同的通讯环境中工作。 实践证明,基于CPLD/FPGA的多串口设计有效地解决了工业控制中一对多串口通讯的可靠性问题,降低了硬件复杂度,提升了系统集成度。这种设计方法对于降低系统成本、简化硬件设计具有显著优势,尤其适合于嵌入式系统中的应用。 总结来说,本文提出了一种创新的多串口扩展技术,通过CPLD/FPGA的编程实现了并行到串行的转换,并通过接收缓冲和发送模块优化了数据传输流程。该技术在工业控制领域具有广泛的应用前景,对于提高系统的通讯效率和稳定性具有重要意义。

- 粉丝: 1

- 资源: 940

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Javaweb+jsp+mysql开发的论坛系统【含源码+数据库+项目运行指导视频】

- 秋招中刷题的记录,针对常见笔试面试算法题

- 3W单声道关断模式音频功率放大器8002A的设计与应用

- C++《基于网格的3D(高度地图)路径查找的基本算法:BFS,Dijkstra,A*,Theta》+项目源码+文档说明+代码注释

- 人工智能-大语言模型-基于ChatGLM-6B + LoRA的Fintune方案

- 秋招中关于FreeRTOS的知识点总结

- 微信支付Java实现 微信支付 NATIVE 方式 网页二维码的形式显示

- table-model-view-delagate核心总结

- 嵌入式硬件开发基础知识与应用指南

- java SSF项目框架源码 后台管理系统源码数据库 MySQL源码类型 WebForm

信息提交成功

信息提交成功