没有合适的资源?快使用搜索试试~ 我知道了~

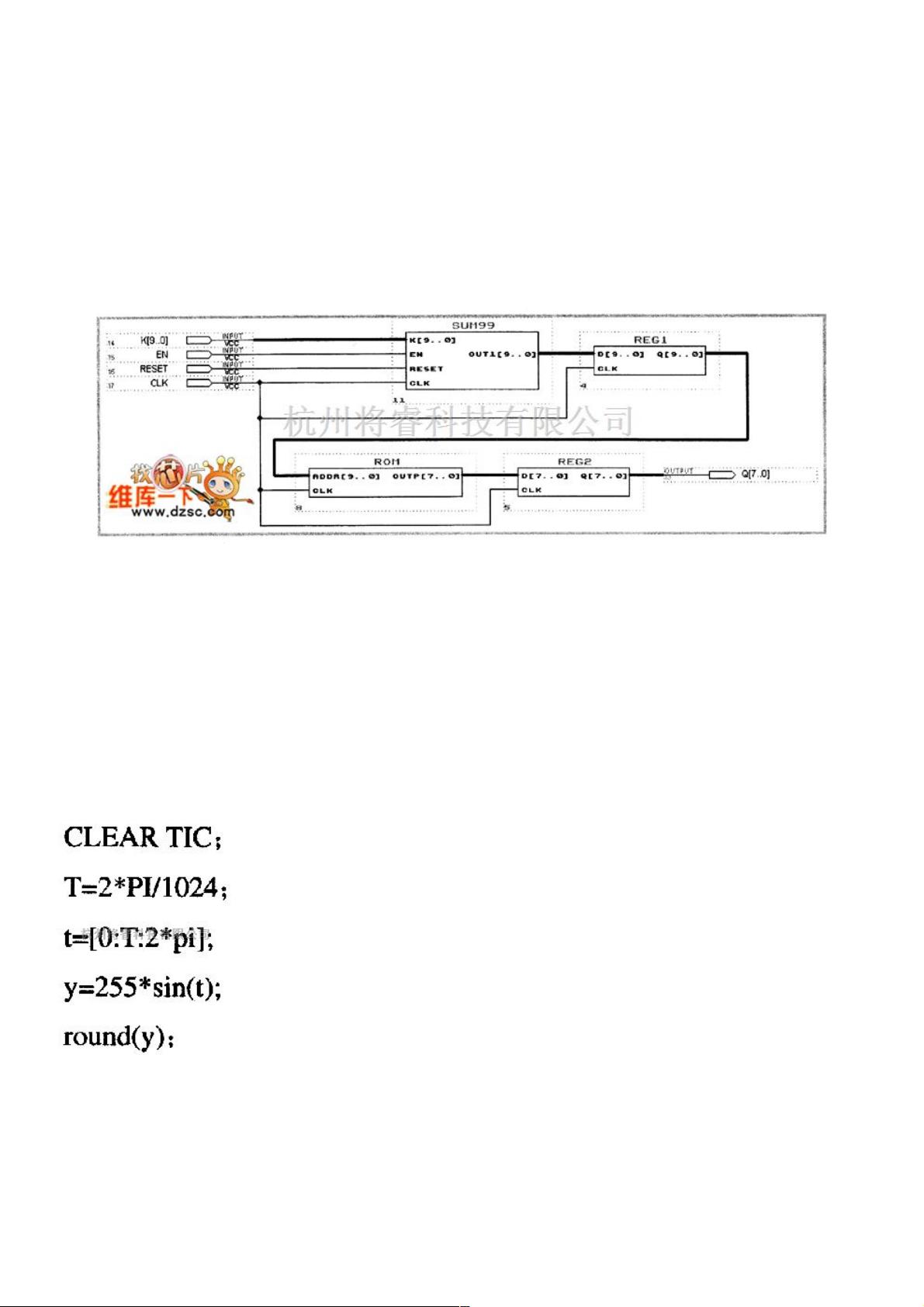

根据图1,并假定相位控制字为0,这时DDS的核心部分相位累加器的FPGA的设计可分为如下几个模块:相位累加器SUM99、相位寄存器REG1、正弦查找表ROM和输出数据寄存器REG2,其内部组成框图如图 2所示。图中,输入信号有时钟输入CLK,使能端EN,复位端RESET,频率控制字K,输出信号为Q。 图2 DDS内部组成框图 整个DDS模块采用一个时钟,以用来同步各个模块的运算速度。其中相位累加器SUM99是一个带有累加功能的10位加法器,它以设定的10位频率控制字Κ作为步长来进行加法运算,当其和满时,计数器清零,并进行重新运算。相位寄存器REG1就是一个一般的10位寄存器,它

资源推荐

资源详情

资源评论

EDA/PLD中的中的DDS的的FPGA实现设计实现设计

根据图1,并假定相位控制字为0,这时DDS的核心部分相位累加器的FPGA的设计可分为如下几个模块:相位

累加器SUM99、相位寄存器REG1、正弦查找表ROM和输出数据寄存器REG2,其内部组成框图如图 2所示。

图中,输入信号有时钟输入CLK,使能端EN,复位端RESET,频率控制字K,输出信号为Q。 图2 DDS内

部组成框图 整个DDS模块采用一个时钟,以用来同步各个模块的运算速度。其中相位累加器SUM99是一个

带有累加功能的10位加法器,它以设定的10位频率控制字Κ作为步长来进行加法运算,当其和满时,计数器清

零,并进行重新运算。相位寄存器REG1就是一个一般的10位寄存器,它

根据图1,并假定相位控制字为0,这时DDS的核心部分相位累加器的FPGA的设计可分为如下几个模块:相位累加器

SUM99、相位寄存器REG1、正弦查找表ROM和输出数据寄存器REG2,其内部组成框图如图 2所示。图中,输入信号有时钟

输入CLK,使能端EN,复位端RESET,频率控制字K,输出信号为Q。

图2 DDS内部组成框图

整个DDS模块采用一个时钟,以用来同步各个模块的运算速度。其中相位累加器SUM99是一个带有累加功能的10位加法

器,它以设定的10位频率控制字Κ作为步长来进行加法运算,当其和满时,计数器清零,并进行重新运算。相位寄存器REG1

就是一个一般的10位寄存器,它对输入端输入的数据进行寄存,当下一个时钟到来时,输出寄存的数据。正弦查找表ROM是

DDS最关键的部分,也是最复杂的部分,设计时首先需对正弦函数进行采样,接着将采样的结果放到ROM模块的对应存储单

元中,每一位地址对应一个数值,输出为9位。为了保证输出数据的稳定性,我们将ROM的输出数据先寄存在REG2中,待下

一个时钟到来时,再将其输出。整个系统各模块是在同步时钟信号CLK的控制下协调工作的。

下面介绍一下正弦查找表ROM模块的具体设计。

首先利用MATLAB或C语言编程对正弦函数进行采样;然后对采样数据进行二进制转换,其结果作为查找表地址的数值。

用MATLAB语言编写的正弦函数数据采集程序如下:

用C语言编写的正弦函数数据采样程序如下:

资源评论

weixin_38627590

- 粉丝: 13

- 资源: 919

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- java项目工时统计成本核算管理系统源码数据库 MySQL源码类型 WebForm

- Python-基于Pygame的贪吃蛇

- C#ASP.NET高校移动考勤webapp源码数据库 SQL2008源码类型 WebForm

- (2000-2023年)中国各、省、市、县、乡镇基尼系数数据(全新整理)

- JAVA的SpringBoot快速开发平台源码数据库 MySQL源码类型 WebForm

- java校园跑腿综合服务网平台小程序源码带部署搭建教程数据库 MySQL源码类型 WebForm

- 时间序列-白银-1分数据

- C#VS2015进销存管理系统源码数据库 SQL2008源码类型 WebForm

- java企业报表管理系统源码数据库 MySQL源码类型 WebForm

- 软考题库试题及其解析.docx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功