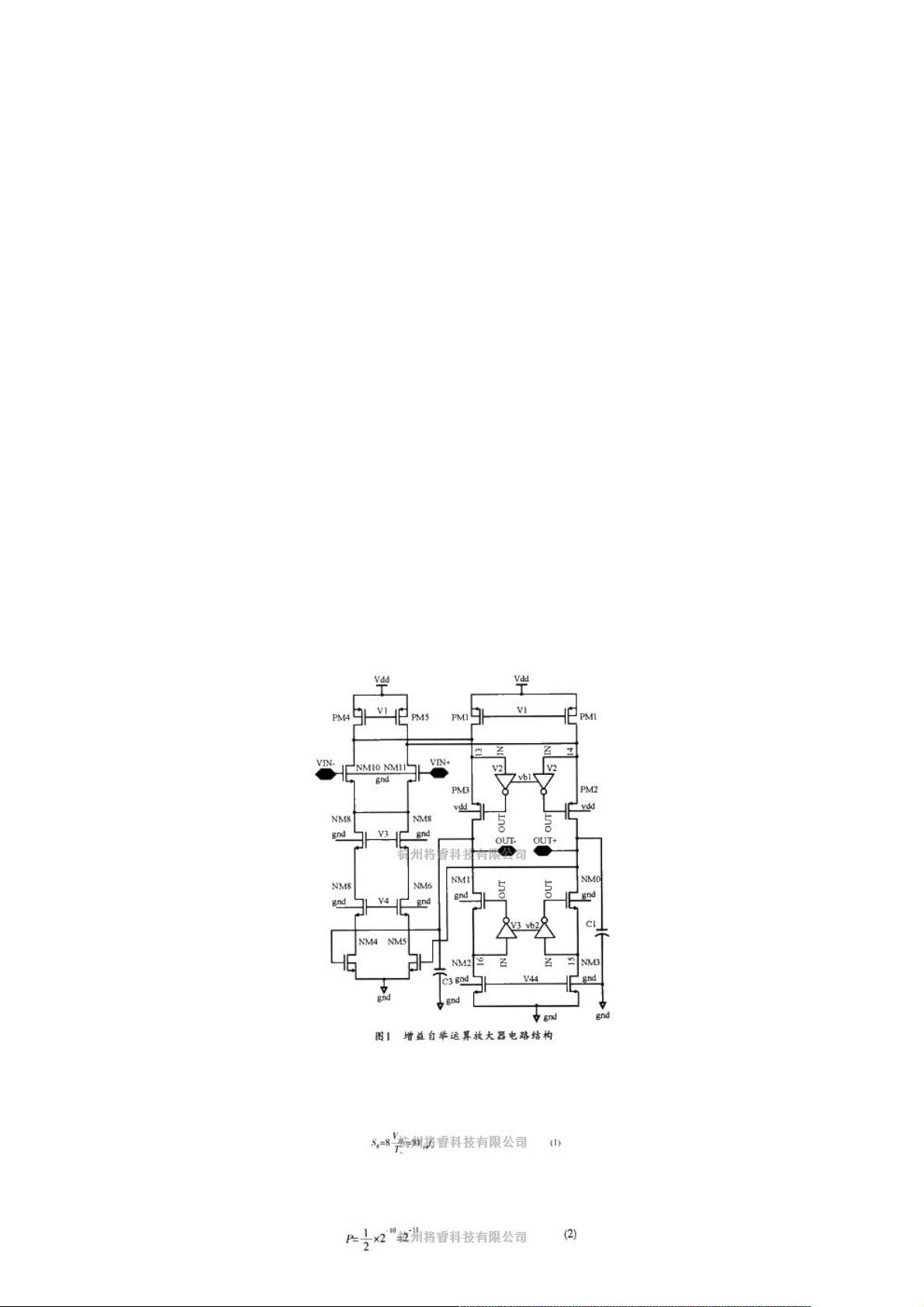

0 引言 采样/保持电路是模数转换器的重要组成部分,它的性能决定着整个A/D转换器的性能。随着科学技术的发展,系统对A/D转换器的速度和精度要求越来越高,因此,设计一个高性能的采样/保持电路就显得尤为重要。 一般的采样保持电路都是采用开关电容电路来实现的。由于MOS开关固有的电荷注入与时钟馈通效应,采样/保持电路一般难以得到理想的情况。尽管已经提出了许多技术和电路结构[1]但是电荷注人和时钟馈通效应所导致的非线性对电路性能的影响还是很大。 采样/保持电路的另外一个设计难点在于运算放大器的设计。采样/保持电路的精度决定于放大器的增益,高增益的运算放大器能够保证采样/保持电路达到 【电源技术中的高性能CMOS采样保持电路设计】 在现代电子系统中,模数转换器(ADC)扮演着至关重要的角色,而采样/保持电路是ADC的核心组件之一,直接影响着整个系统的性能。随着科技的进步,对ADC的速度和精度需求不断提高,设计高性能的采样/保持电路变得愈发关键。 传统的采样/保持电路常采用开关电容结构。然而,MOS开关在操作过程中会出现电荷注入和时钟馈通效应,导致非线性失真,这对电路性能造成负面影响。尽管已有多种技术手段和电路结构被提出以减轻这些问题,但这些效应仍然难以彻底消除。 采样/保持电路的另一设计难点在于运算放大器的选择。运算放大器的增益决定了电路的精度,而带宽则决定了采样速度。高增益放大器可确保高精度采样,但增益与带宽之间的平衡是设计中的挑战。本文提出了一种全差分结构的采样/保持电路,通过底板采样技术有效抑制电荷注入和时钟馈通效应,并采用高性能的增益自举运算放大器,减少了有限增益和不完全建立引起的误差。 增益自举运算放大器采用折叠式共源共栅结构,兼顾了大增益和高速响应。该设计无需外部共模反馈电路,降低了功耗并减少了对整体运算放大器速度的影响。运算放大器的摆率和建立时间是关键参数,必须满足采样保持电路的时序要求。通过计算,可以确定适当的相位裕度和增益提升放大器的单位增益带宽,以实现线性建立并降低误差。 采样开关的设计同样至关重要,开关的尺寸、宽长比和电荷注入效应、时钟馈通效应都会影响电路性能。低导通电阻的开关可以减少信号损失,优化采样效果。设计中需要综合考虑这些因素,确保开关能在不影响性能的前提下,有效地完成采样和保持功能。 设计高性能CMOS采样保持电路需要解决电荷注入、时钟馈通、运算放大器性能优化以及采样开关设计等问题。通过创新的电路结构和优化参数,可以实现高速、高精度的采样,满足现代系统对ADC的需求。

- 粉丝: 7

- 资源: 920

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功