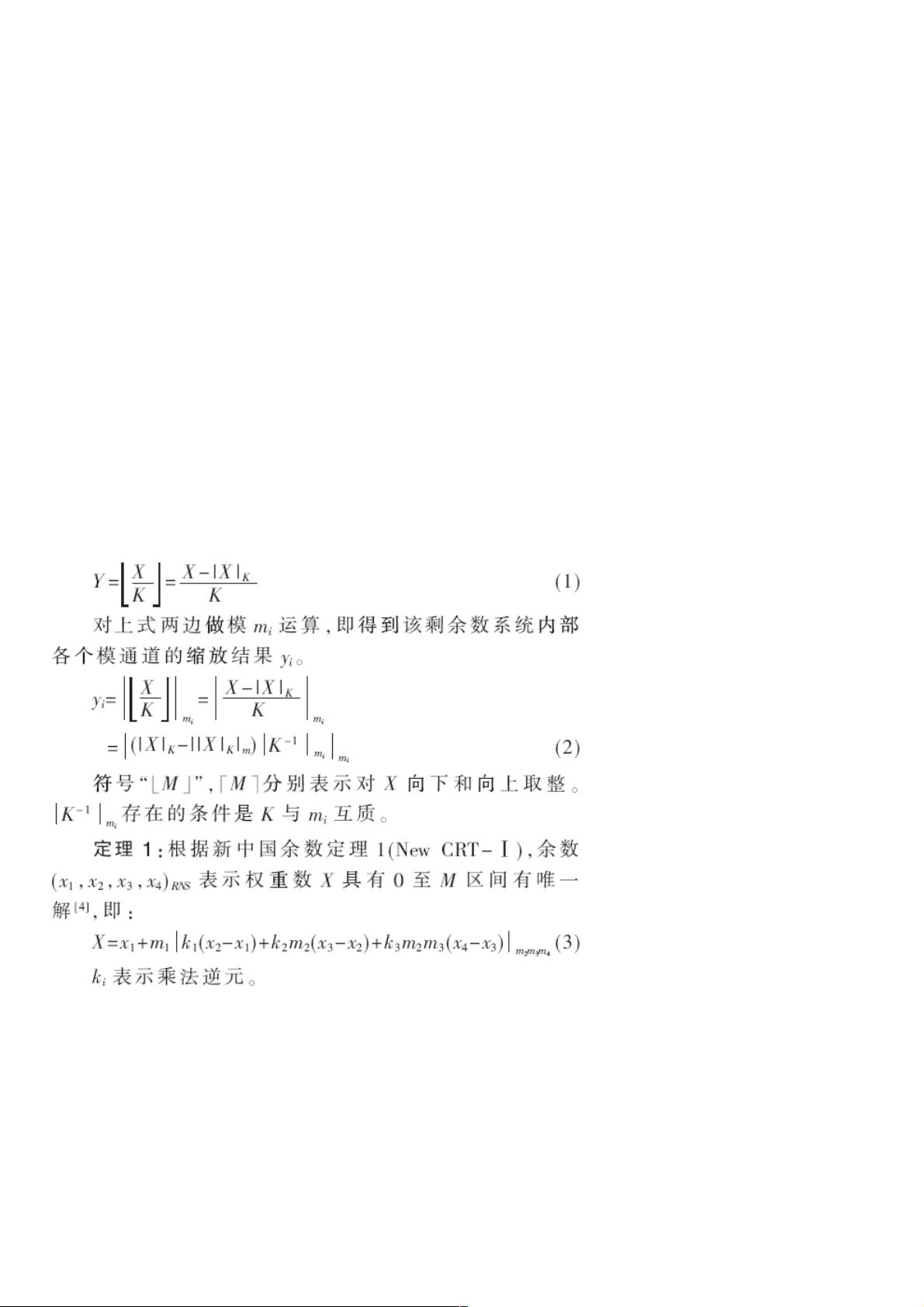

数值缩放(scaling)和奇偶检测等的高效VLSI实现已经成为剩余数系统(RNS)研究的瓶颈问题。该文基于4模集合{2n,22n+1,2n+1,2n-1},在新中国余数定理的基础上,提出了该模集合优化的2n比例变换优化算法,并基于VLSI实现其硬件结构。分析结果表明,该2n比例变换的VLSI实现具有更好的面积和功耗特性。 《4模集合余数系统比例变换的VLSI实现与优化》 在当前信息技术日新月异的时代,高性能、低能耗的电子设备成为了研究的重点。其中,剩余数系统(RNS)因其无进位和并行计算的优势,逐渐成为高速数字信号处理的重要工具。然而,RNS中的某些操作,如数值缩放和奇偶检测,因其复杂性成为系统效率提升的障碍。本文主要关注4模集合{2n,22n+1,2n+1,2n-1}中的比例变换问题,基于新中国余数定理提出了一种优化的2n比例变换算法,并设计了对应的VLSI硬件结构。 剩余数系统的比例变换在防止溢出和内部乘积处理中扮演着关键角色,但传统方法通常会导致较高的延迟和复杂的硬件需求。以往的研究多集中在3模集合上,而本文则聚焦于4模集合,通过分析反向转换和比例缩放的算法,提出了一种新的2n比例缩放策略。此策略在保持运算效率的同时,显著改善了硬件实现的面积和功耗特性。 算法描述如下:给定一个基于4模集合{2n,22n+1,2n+1,2n-1}的整数X,对其进行比例因子k的缩放,生成新的数值Y。通过一系列数学变换,可以将比例变换简化为对每个模通道的操作。例如,模2n-1的变换可以通过循环左移和位取反来实现;模22n+1和2n+1的变换需要减一和加一的校正,以及进位保留加法器的应用;模2n的变换则相对直接,仅需取低n位即可。 硬件实现部分,文章详细描述了针对y1、y2、y3和y4四个模通道的电路设计。每个模通道的实现都利用了进位保留加法器和模加法器,结合定理和特定的校正因子,以减少延迟和提高硬件效率。例如,y1的实现基于循环移位和位取反;y2和y3的实现通过缩一码加法器和校正项;y4的实现则相对简单,直接应用模2n-1的加法器即可。 性能评估显示,本文提出的2n比例变换算法在VLSI实现上的面积和延迟相比于现有文献有所改进,这得益于优化的2n比例变换算法和精心设计的硬件结构。通过与已有的4模集合2n比例变换方案对比,本文的方法在资源利用率和计算速度方面具有显著优势。 本文针对4模集合{2n,22n+1,2n+1,2n-1}的剩余数系统比例变换问题,提出了一种基于新中国余数定理的优化算法,实现了高效的VLSI硬件结构。这一工作不仅解决了比例变换的复杂性和效率问题,也为未来RNS系统的设计提供了新的思路和优化方向。

- 粉丝: 7

- 资源: 953

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 三星 Samsung Xpress SL M2820 激光打印机系列

- PyQT6 GUI编程开发桌面软件

- 测试注册使用权限.rar

- 三星 Samsung Xpress SL M2820 激光打印机系列

- TMT行业:中软国际AIGC多款产品发布与华为鲲鹏+昇腾计算生态系统繁荣

- Epay纵横支付 游戏账号点券全通道支付系统 - 抖音虎牙快手yy直播QB支付,DNF游戏点券,全通道几十种支持,站长亲测

- 海外AI应用落地进展梳理:AIGC商业化浪潮将至-多模态能力推动产业变革

- 40ab75cab55a4d9999c4cbd04a426894.mp4

- AIGC应用持续升级,国内大模型布局游戏教育等多元领域

- 体育资讯软件的实现+ssm

信息提交成功

信息提交成功