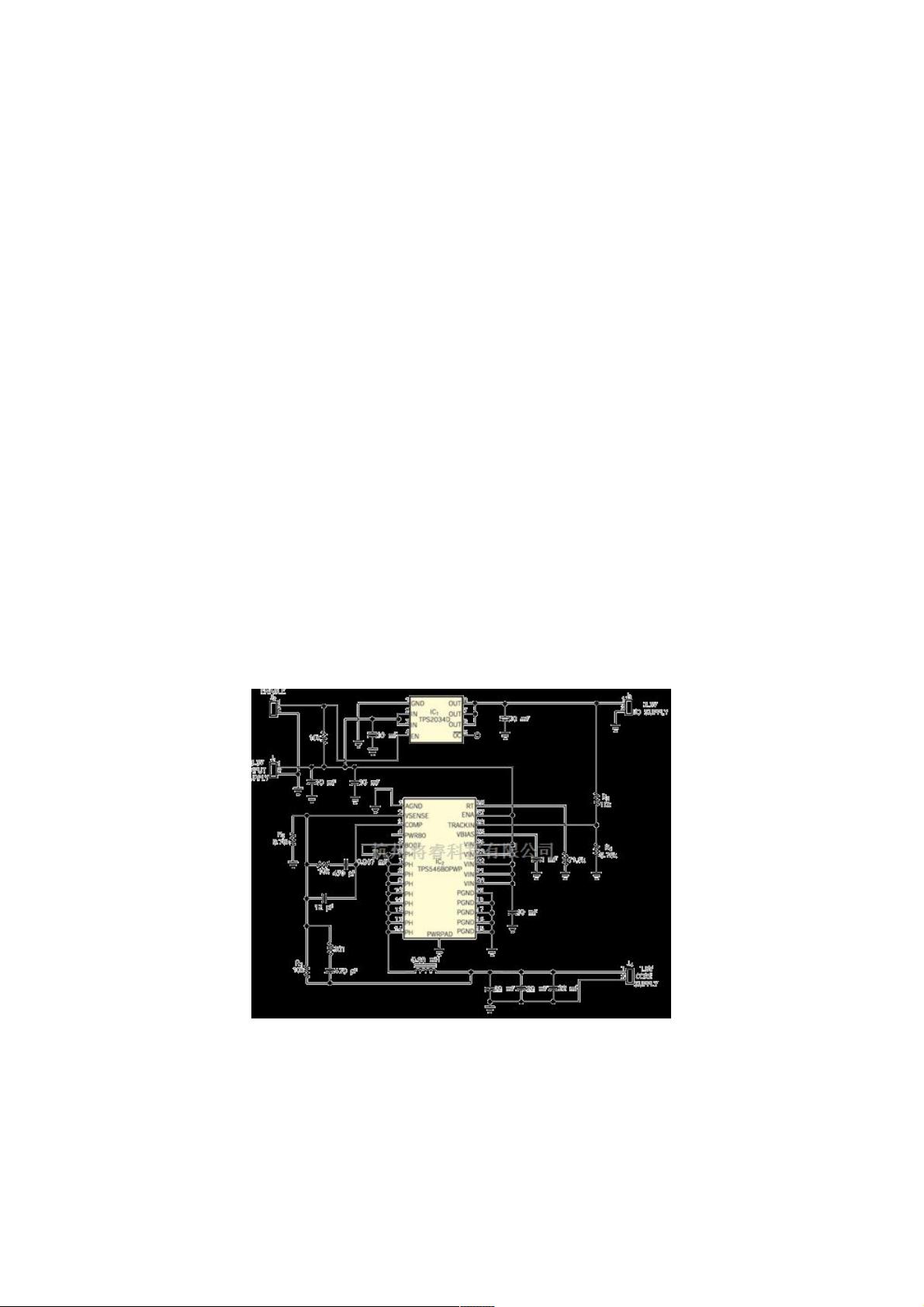

系统设计师必须考虑加电和断电期间芯核电源和I/O源之间的定时差和电压差(换言之,就是电源定序)问题。当电源定序不当时,就有可能发生闭锁失灵或电流消耗过大的现象。如果两个电源加到芯核接口和I/O接口上的电位不同时,就会出现触发闭锁。定序要求不相同的FPGA和其他元件会使电源系统设计更加复杂化。为了排除定序问题,你应当在加电和断电期间使芯核电源和I/O电源之间的电压差最小。图1所示的电源将3.3V输入电压调节到1.8V芯核电压,并在加电和断电期间跟踪3.3V I/O电压,以使两电源线之间的电压差最小。 图1所示电源包含IC1和IC2两块IC,它们分别是TPS2034电源开关和T 电源定序在FPGA(Field Programmable Gate Array)系统设计中扮演着至关重要的角色,它涉及到加电和断电过程中芯核电源(Core Power)与I/O电源(Input/Output Power)之间的电压差和时间差管理。不当的电源定序可能导致FPGA内部的闭锁失灵,也就是器件无法正常工作,或者是造成过大的电流消耗,这不仅会影响系统的稳定性,还可能损坏设备。 电源定序的主要目标是在加电和断电过程中保持芯核电源和I/O电源间的电压差最小,以避免触发闭锁现象。闭锁通常发生在电源电压不匹配时,即芯核电源和I/O电源的电位不同,导致FPGA接口间的数据传输出现问题。此外,FPGA与其他元件的电源定序要求不一致,会进一步增加电源系统设计的复杂性。 如图1所示的电源设计方案中,采用TPS2034电源开关和TPS54680降压型开关稳压器协同工作,实现电源定序。TPS2034在启动时产生一个慢斜坡电压,斜坡时间为6毫秒,这有助于降低涌入电流,从而减少对FPGA的瞬态电流冲击。同时,TPS2034确保在I/O电源加到负载前,芯核电源已有足够的偏置电压工作,这样可以避免未准备好的I/O电源对芯核电源的影响。 TPS54680的TRACKIN引脚利用模拟多路转换器实现跟踪功能。在加电和断电期间,当TRACKIN引脚电压低于0.891V内部基准时,该引脚作为开关稳压器的基准,通过调整R3和R4分压器与反馈补偿回路的R1和R2分压器保持平衡,确保电压跟踪的准确性。TPS54680拥有高效率,能提供大电流输出,确保在断电期间芯核电源和I/O电源的电压差保持在安全范围内。 在断电过程中,当I/O电源电压下降,芯核电源电压也会跟随下降,以避免电压差过大导致的问题。图3展示了这种电压钳位的过程。通常,肖特基二极管用于在断电时限制芯核电源和I/O电源间的电压差,但某些设计可能不需要额外的二极管,如图1所示的电源电路。 这种电源定序电路设计简化了系统,减少了闭锁问题,并降低了FPGA启动时的瞬态电流,从而提高了系统的可靠性和效率。通过精心设计电源定序电路,不仅可以保证FPGA的正常工作,还能优化整体系统的能源效率,减少元件数量,提升产品的质量。

- 粉丝: 6

- 资源: 917

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论0