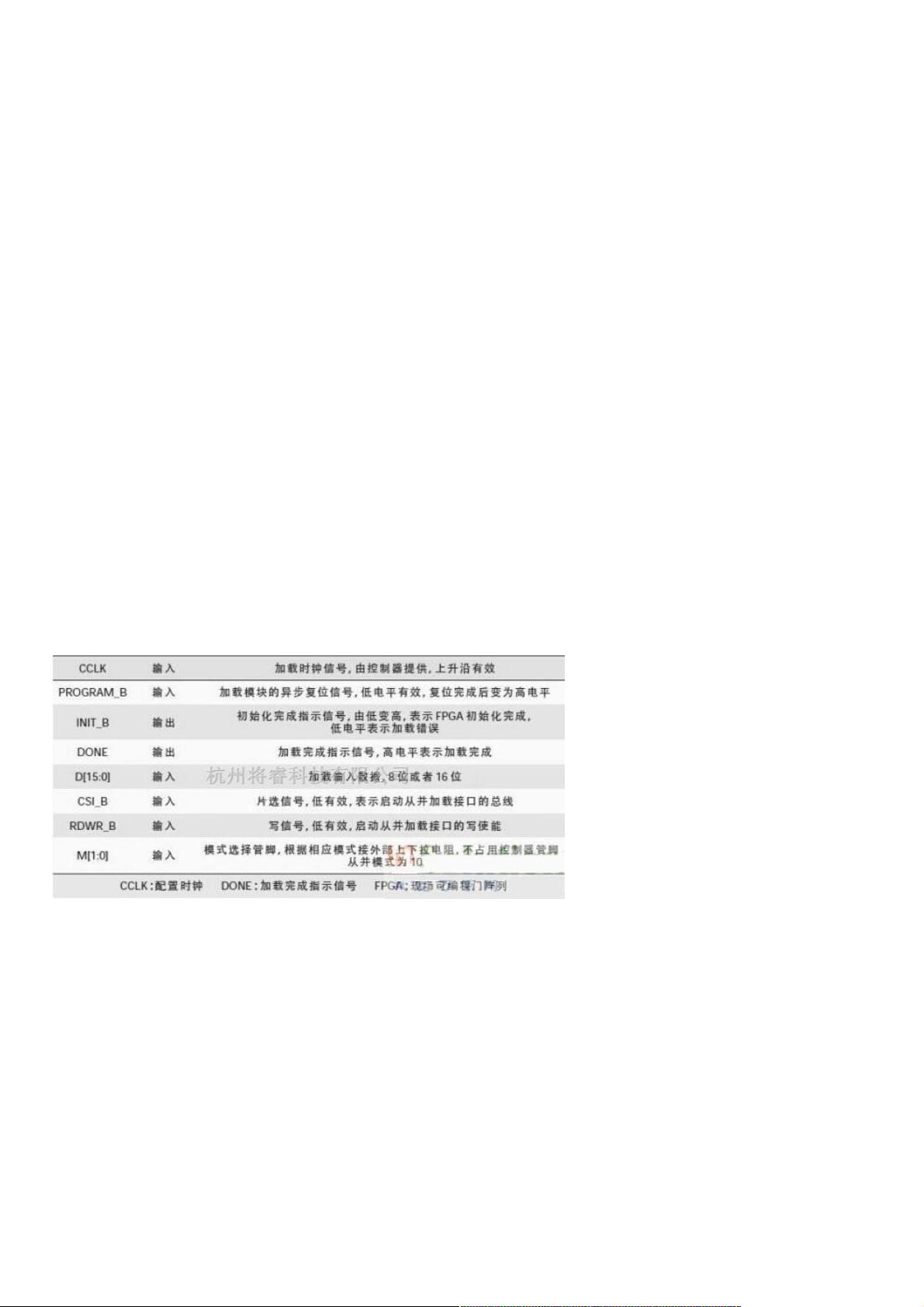

现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。FPGA 是基于静态随机存储器(SRAM) 结构的,断电后程序丢失后的每次上电都需要重新加载程序。且随着FPGA 规模的升级,加载程序的容量也越来越大,如Xilinx 公司的Spartan - 6 系列中的6SLX150T,其加载容量最大可以达到4.125 MB。 1 FPGA 常用配置方式 FPGA 的配置数据通常存放在系统中的存储器件中,上电后控制器读取存储器中的bit 文件并加载到FPGA 中,配置 在工业电子领域,现场可编程门阵列(FPGA)因其灵活性和强大的功能,被广泛应用于通信产品的设计中。FPGA基于SRAM架构,这意味着在每次电源断开后,内部配置都会丢失,需要重新加载。随着FPGA规模的扩大,如Xilinx公司的Spartan-6系列中的6SLX150T,配置文件的大小可高达4.125 MB,这使得快速有效的加载方法变得至关重要。 FPGA的配置方式主要有四种:JTAG、从串、主从和从并。JTAG主要用于调试,占用资源较多;从串方式虽占用资源少,但速度慢;主从方式需要特定型号的FLASH,增加了成本;而从并方式是本文重点讨论的解决方案,它能有效利用资源,提高加载速度。 从并加载方式中,FPGA与外部设备通过多个I/O接口进行数据传输。以Xilinx Spartan-6系列为例,其从并加载涉及多个管脚,但CPU通常没有足够的GPIO口来直接支持这种加载。因此,常常配合复杂可编程逻辑器件(CPLD)使用,通过CPLD作为数据缓冲和控制逻辑,来实现高速的数据传输。 加载流程大致分为以下几步:CPU将配置数据从FLASH移动到DDR内存中,然后通过DDR2接口快速读取数据到CPU缓存。之后,CPU通过局部总线将数据写入CPLD的寄存器,最后CPLD通过与FPGA的同步从并接口将数据快速加载到FPGA中。这种方法的优势在于,数据预处理和加载过程可以分开,加载时间主要取决于CPU写入CPLD的速度和从并接口的时钟频率。 为了实现这一加载方案,CPLD的程序使用Verilog硬件描述语言编写。加载模块的接口设计使得CPU能够高效地将数据传送到CPLD,并由CPLD控制数据传输到FPGA。通过模型模拟(如Modelsim 6.5SE)进行仿真,可以验证每字节数据的加载过程,确保加载的正确性和效率。 工业电子中的CPLD对FPGA从并快速加载方案是解决大容量FPGA配置问题的有效途径。它利用CPLD作为数据桥接和控制中心,优化了加载流程,减少了加载时间,提高了系统的整体性能。这种方法对于那些需要频繁重新配置且要求快速启动的工业应用来说,具有显著的优势。

- 粉丝: 7

- 资源: 971

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 光纤到户及通信基础设施报装申请表.docx

- 踝关节功能丧失程度评定表.docx

- 环保设施投资估算表.docx

- 既有建筑物通信报装申请表.docx

- 既有建筑物通信报装现场查勘报告.docx

- 监督机构检查记录表.docx

- 肩关节功能丧失程度评定表.docx

- 大学生创新创业训练计划大创项目的全流程指南

- 简易低风险工业厂房通信报装申请表.docx

- 建设工程消防验收各阶段意见回复表.docx

- 建设工程消防验收模拟验收意见表.docx

- 建设工程消防验收图纸核查意见表.docx

- 建设工程消防验收现场指导意见表.docx

- 建筑工程竣工验收消防设计质量检查报告(表格填写模板).docx

- 建筑工程消防查验意见和结论.docx

- 建筑工程消防施工竣工报告(表格填写模板).docx

信息提交成功

信息提交成功