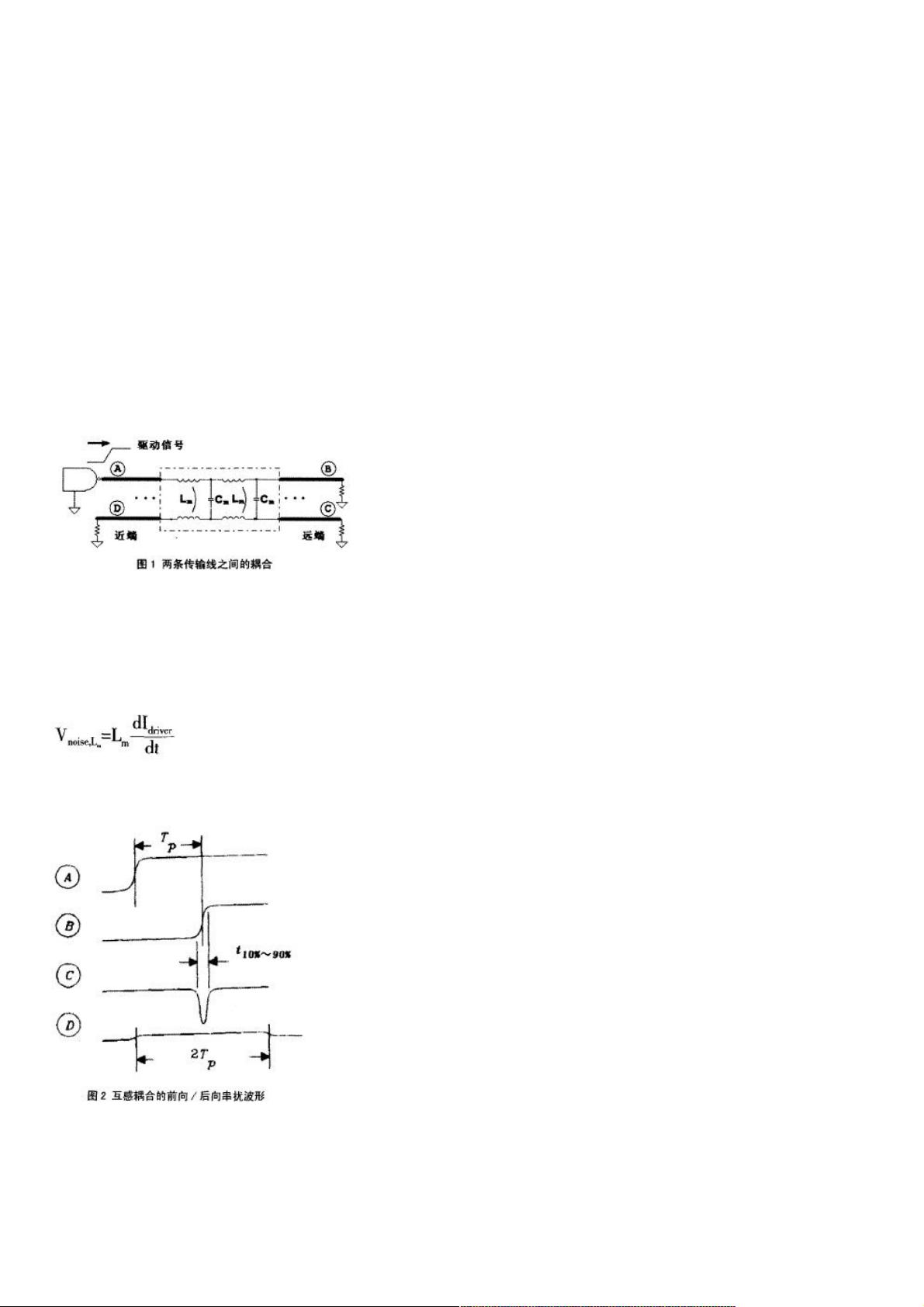

信号频率变高,边沿变陡,印刷电路板的尺寸变小,布线密度加大等都使得串扰在高速PCB设计中的影响显著增加。串扰问题是客观存在,但超过一定的界限可能引起电路的误触发,导致系统无法正常工作。本文主要是对高速PCB串扰的分析。 高速PCB设计中,串扰是一个关键问题,尤其在当今电子设备追求更高的性能和更复杂的功能背景下。串扰是由于信号在传输线间通过电磁场的耦合导致的不期望的噪声电压,它能影响电路的稳定性和正确性。本文将深入探讨高速PCB串扰的成因、变化趋势以及其对电路的影响。 串扰的产生主要分为两种类型:感性耦合和容性耦合。感性耦合源于相邻传输线间的互感Lm,类似于一系列分布式的变压器,当一个信号从一条线传播到另一条线时,会在相邻线路上感应出噪声电压。这个噪声的大小与驱动电流的变化成正比。而容性耦合则是由于互容Cm的存在,它产生的噪声与电压变化速率有关。这两种耦合在近端和远端会产生不同的效应,其中近端串扰(后向串扰)和远端串扰(前向串扰)的强度和性质各有特点。 在实际的高速PCB设计中,串扰的影响因素众多,包括传输线的几何尺寸(线宽、线距)、传输线与地平面的位置、电流流向,以及介质的电气特性(如厚度、介电常数等)。这些因素决定了耦合电容Cm、耦合电感Lm、单位长度电容C和电感l,以及传输线的特征阻抗Z0。随着信号频率的升高和边沿速度的加快,串扰问题变得更加突出。 串扰可能导致的负面影响主要有以下几点: 1. 信号质量恶化:串扰可以引入额外的噪声,降低信号的信噪比,进而影响信号的完整性,可能导致信号失真或错误。 2. 系统稳定性下降:严重的串扰可能导致电路的误触发,使得系统无法正常工作。例如,在数据传输中,串扰可能导致数据错误,影响通信的可靠性。 3. 功耗增加:为了抵消串扰影响,设计者可能需要增加电源电压或调整电路参数,这可能导致功耗的增加。 4. 设计难度增大:串扰问题使得PCB布局布线设计更加复杂,需要在有限的空间内优化信号线的布置,以减少串扰影响。 解决串扰问题的方法主要包括以下策略: 1. 布局优化:通过合理布局,尽量减少信号线之间的平行距离,利用地平面作为屏蔽,以及使用电源和地平面的分割来降低串扰。 2. 信号线的阻抗控制:确保信号线的特性阻抗匹配,以减少反射和耦合。 3. 使用差分信号:差分信号系统中,两条信号线一起传输互补的信号,相互抵消串扰,提高信号质量。 4. 屏蔽和隔离技术:利用屏蔽层、隔离带或隔离地来隔离信号线,减少耦合。 5. 选择合适的PCB材料和工艺:选择低介电常数和低损耗因子的材料,以及优化制造工艺,有助于减小串扰。 6. 软件辅助设计:使用专业的PCB设计软件进行仿真,提前预测和分析串扰,优化设计。 高速PCB设计中的串扰分析和控制是提升系统性能和可靠性的关键环节。通过理解串扰的原理,结合有效的设计策略,设计师可以有效地管理和减少串扰的影响,从而实现高性能的电子产品。

- 粉丝: 5

- 资源: 997

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Spring Cloud商城项目专栏 049 支付

- sensors-18-03721.pdf

- Facebook.apk

- 推荐一款JTools的call-this-method插件

- json的合法基色来自红包东i请各位

- 项目采用YOLO V4算法模型进行目标检测,使用Deep SORT目标跟踪算法 .zip

- 针对实时视频流和静态图像实现的对象检测和跟踪算法 .zip

- 部署 yolox 算法使用 deepstream.zip

- 基于webmagic、springboot和mybatis的MagicToe Java爬虫设计源码

- 通过实时流协议 (RTSP) 使用 Yolo、OpenCV 和 Python 进行深度学习的对象检测.zip

信息提交成功

信息提交成功