没有合适的资源?快使用搜索试试~ 我知道了~

摘要:介绍了 PCI 9054接口芯片的性能及数据传输特点,提出了一种基于 PCI 9054外扩异步 FIFO(先进先出)的 FPGA(现场可编程门阵列)实现方法。由于 PCI 9054内部 FIFO存储器主要用于数据的读写控制,容量有限,不能满足半实物仿真系统数据传输的要求。因此,本文利用 FPGA来实现外扩异步 FIFO的方法。该方法采用模块化的设计思想,用 FPGA作为系统的控制核心,解决了半实物仿真系统数据传输过程中由计算机中断而引起的数据传输间歇性问题。 0. 引言 目前,计算机上的系统总线常见的有 ISA总线、 PCI总线以及 VXI总线等。在实际应用中,PCI总线已经成

资源推荐

资源详情

资源评论

基于基于PCI接口芯片外扩接口芯片外扩FIFO的的FPGA实现实现

摘要:介绍了 PCI 9054接口芯片的性能及数据传输特点,提出了一种基于 PCI 9054外扩异步 FIFO(先进先

出)的 FPGA(现场可编程门阵列)实现方法。由于 PCI 9054内部 FIFO存储器主要用于数据的读写控制,容

量有限,不能满足半实物仿真系统数据传输的要求。因此,本文利用 FPGA来实现外扩异步 FIFO的方法。该方

法采用模块化的设计思想,用 FPGA作为系统的控制核心,解决了半实物仿真系统数据传输过程中由计算机中

断而引起的数据传输间歇性问题。 0. 引言 目前,计算机上的系统总线常见的有 ISA总线、 PCI总线以

及 VXI总线等。在实际应用中,PCI总线已经成

摘要:介绍了 PCI 9054接口芯片的性能及数据传输特点,提出了一种基于 PCI 9054外扩异步 FIFO(先进先出)的

FPGA(现场可编程门阵列)实现方法。由于 PCI 9054内部 FIFO存储器主要用于数据的读写控制,容量有限,不能满足半实

物仿真系统数据传输的要求。因此,本文利用 FPGA来实现外扩异步 FIFO的方法。该方法采用模块化的设计思想,用 FPGA

作为系统的控制核心,解决了半实物仿真系统数据传输过程中由计算机中断而引起的数据传输间歇性问题。

0. 引言

目前,计算机上的系统总线常见的有 ISA总线、 PCI总线以及 VXI总线等。在实际应用中,PCI总线已经成为主流的应用

总线,具有较高的数据传输效率,能满足大多数数据采集和发送系统的需求。由于 PCI总线规范相当复杂,一般实际应用中都

选择专用的 PCI接口芯片来设计 PCI接口。本文选择美国 PLX公司生产的 PCI总线通用接口芯片 PCI 9054,利用该专用芯片

桥接 PCI总线与本地总线。在实际半实物仿真测试系统的应用中,要求仿真计算机能够快速、稳定的连续输出所需数据,而由

于 PCI 9054内部 FIFO存储器主要用于数据的读写控制,容量有限,不能满足半实物仿真测试系统数据传输的要求。因此,本

文提出利用 FPGA内部的嵌入式阵列块( EAB)(Embedded Array Blocks)来实现外扩 FIFO的功能,目的是用于存储由

PCI总线传输过来的仿真数据,并在 D/A转换期间起到数据缓存的作用。

1. PCI 9054特性及 FPGA内部 EAB模块简介

1.1 PCI 9054接口芯片简介及配置

PCI 9054内部有六个可编程的 FIFO存储器,它们可分别实现 PCI发起读、写操作, PCI目标读、写操作和 DMA方式

读、写操作。这里采用 DMA方式传输数据,可实现大量数据的突发传输而不丢失,数据通过 PCI 9054内部的 FIFO进行双向

传输。为此,核心控制芯片 FPGA内部专门设计了与 PCI 9054进行数据通信的逻辑控制单元,通过查询 FIFO的当前状态,实

时地把数据传送到相应的存储单元。

PCI 9054内部提供一个串行 EEPROM配置接口,为 PCI总线和局部总线配置部分重要信息,如本地总线的基地止空间、

I/O空间、中断控制信号等信息,总容量为 2 K字节或 4 K字节,其内容可通过 PCI总线写入,也可通过编程器直接烧写。

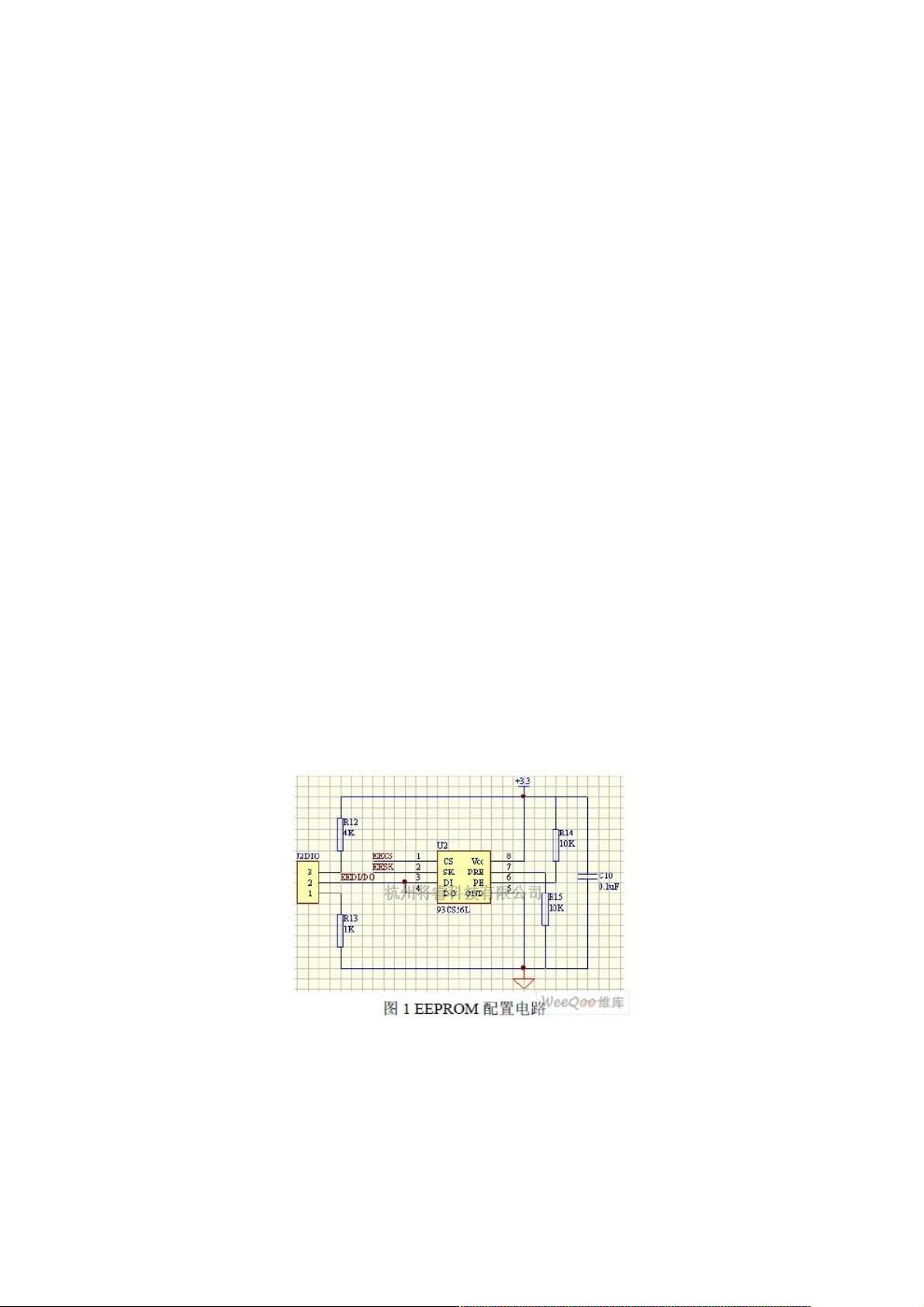

EPROM一定要选择支持串行传输方式的芯片,这里选用 93CS56L作为外接 EEPROM,容量为 2 K字节, EEPROM的配置

电路如图 1所示。图中 93CS56L的 1、2、3/4引脚与 PCI9054上的 EECS、EESK、EEDI/EEDO引脚相连,系统启动时自动

检测 EEPROM,并将初始化配置参数装入 PCI配置寄存器中,根据本地总线对内存、 I/O端口和中断等统一划分空间,自动

配置。EEPROM的配置至关重要,其配置不正确可导致整个系统无法运行。

1.2嵌入式逻辑阵列块( EAB)结构

嵌入式逻辑阵列块( EAB)具有逻辑和存储功能,在输入、输出端口上带有寄存器的 RAM块,利用它们可以实现

ROM、RAM、双端口 RAM和 FIFO等功能设计。每个 EAB模块均含有 2 K的数据容量,每个 EAB单元中还包括数据区、总线

和读 /写控制等。数据区是 EAB的核心部分,可根据数据/地址线的不同设置将其配置为 2048×1bit,1024×2bit,

512×4bit,256×8bit等。相应的数据总线可以配置成 8bit、4bit、2bit或 1bit宽,地址总线可以配置成 8bit、9bit、10bit或 11bit

宽。而输入输出总线相对应,这三条总线都可以设置为同步/异步两种工作方式。

2. 外扩异步 FIFO的 FPGA实现

2.1异步 FIFO存储器的内部结构及工作原理

资源评论

weixin_38553791

- 粉丝: 3

- 资源: 915

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功