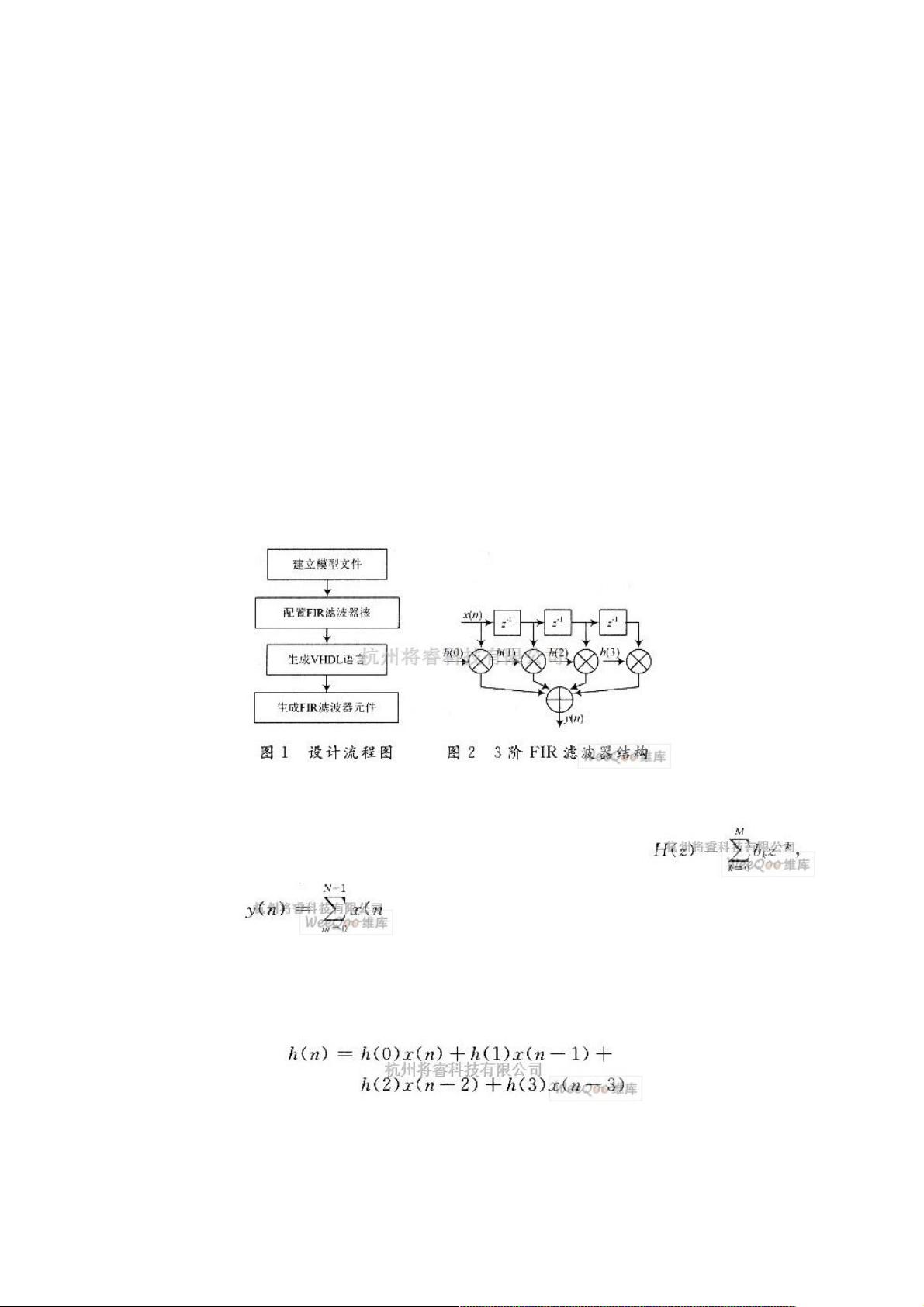

0 引言 数字滤波(idgital filter)是由数字乘法器、加法器和延时单元组成的一种计算方法。其功能是对输入离散信号的数字代码进行运算处理,以达到改变信号频谱的目的。数字滤波器根据频域特性可分为低通、高通、带通和带阻4个基本类型;根据时域特性可分为无限脉冲响应(infinite impulse response,IIR)滤波器和有限脉冲响应(finite impulse response,FIR)滤波器。FIR滤波器不存在稳定性和是否可实现的问题,容易做到线性相位,故在数据通信、图像处理等领域广泛应用。 目前,FIR滤波器的硬件实现有以下几种方式:一种是使用通用数字滤波器集 在模拟技术领域,基于SoPC(System on a Programmable Chip,可编程片上系统)的FIR(Finite Impulse Response,有限脉冲响应)滤波器设计与实现是一种高效且灵活的信号处理方法。FIR滤波器是数字信号处理中的重要组成部分,它通过数字乘法器、加法器和延时单元对输入离散信号进行运算,以改变信号的频谱特性。由于FIR滤波器具有稳定的性能和易于实现线性相位的特性,它们在数据通信、图像处理等领域有着广泛的应用。 FIR滤波器的设计主要关注其频率响应,可以设计成低通、高通、带通或带阻滤波器,以满足特定的信号过滤需求。此外,FIR滤波器的时域特性是有限的,这意味着它们的响应在某个时刻后将消失,这使得它们在实现上更为简单和可靠,无需担心稳定性问题。 FIR滤波器的硬件实现有多种途径。传统的实现方式包括使用通用数字滤波器集成电路,虽然使用方便,但可能受限于固定的字长和滤波器阶数,难以满足复杂需求。另外,使用DSP(Digital Signal Processor,数字信号处理器)芯片也是一个常见选择,DSP芯片拥有专门的信号处理功能,但速度可能受到程序顺序执行的限制,并且不同系列的DSP芯片可能需要不同的编程指令,增加了开发难度。 相比之下,FPGA(Field Programmable Gate Array)提供了一种更为灵活的解决方案。FPGA允许用户自定义硬件逻辑,特别适合实现FIR滤波器的并行结构,能有效提高处理速度。通过利用FPGA的并行性和可扩展性,可以在单个时钟周期内完成一个FIR滤波器的输出计算,大大提升了效率。 在SoPC系统中,FIR滤波器可以与微处理器、存储器和其他硬件组件集成在同一芯片上,形成一个完整的嵌入式系统。这种方式可以简化系统设计,降低功耗,并且便于调试和优化。在具体实现过程中,可以利用Altera公司的FIR Compiler和DSP Builder工具,它们提供了在Simulink环境中设计和仿真FIR滤波器模型的功能。通过配置FIR核的参数,如滤波器阶数、系数精度等,可以生成定制化的FIR滤波器硬件描述语言(HDL)代码,进一步在FPGA中实现。 在模型文件建立后,通过配置FIR滤波器核的参数,可以设定滤波器的性能指标,例如选择合适的系数精度以确保计算的精度。一旦参数设置完毕,工具将自动生成相应的HDL代码,并将其综合进FPGA设计中。经过硬件仿真和测试,确保滤波器功能正确无误后,可以将设计下载到FPGA中进行实际运行。 基于SoPC的FIR滤波器设计与实现是一种先进的信号处理技术,它利用了FPGA的灵活性和并行性,以及SoPC的系统集成优势,为数字信号处理提供了高效、精确且可定制的解决方案。这种方法不仅简化了设计流程,还提高了系统性能,为各种领域的应用带来了显著的优势。

- 粉丝: 8

- 资源: 915

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 快速定制中国传统节日头像(源码)

- hcia 复习内容的实验

- 准Z源光伏并网系统MATLAB仿真模型,采用了三次谐波注入法SPWM调制,具有更高的电压利用效率 并网部分采用了电压外环电流内环 电池部分采用了扰动观察法,PO Z源并网和逆变器研究方向的同学可

- 海面目标检测跟踪数据集.zip

- 欧美风格, 节日主题模板

- 西门子1200和三菱FXU通讯程序

- 11种概率分布的拟合与ks检验,可用于概率分析,可靠度计算等领域 案例中提供11种概率分布,具体包括:gev、logistic、gaussian、tLocationScale、Rayleigh、Log

- 机械手自动排列控制PLC与触摸屏程序设计

- uDDS源程序publisher

- 中国风格, 节日 主题, PPT模板

信息提交成功

信息提交成功