没有合适的资源?快使用搜索试试~ 我知道了~

单片机与DSP中的单片机多机冗余设计及控制模块的VHDL语言描述

0 下载量 176 浏览量

2020-12-07

08:17:01

上传

评论

收藏 128KB PDF 举报

温馨提示

试读

3页

摘要:以三个单片机组成的系统为例介绍一种单片机多机冗余容错设计。阐述设计中关键的时钟同步技术和总线仲裁方法,给出控制模块的VHDL语言描述。 关键词:单片机 冗余容错 时钟 总线 VHDL 本文提出一种表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复杂的机间通讯协议实现系统重构,不太注重系统的实时性。本方案结构简单,易于实现,具有极强的实时性,没有电子开关切换总线的咔嗒声输出。单片机价格低廉、功能灵活,也使得该设计在类似仪器仪表的小系统中的运用成为可能。 1 设计原理 设计结构如图1所示。完成整个冗余设计的电路被置于一个核心

资源详情

资源评论

资源推荐

单片机与单片机与DSP中的单片机多机冗余设计及控制模块的中的单片机多机冗余设计及控制模块的VHDL语语

言描述言描述

摘要:以三个单片机组成的系统为例介绍一种单片机多机冗余容错设计。阐述设计中关键的时钟同步技术和总

线仲裁方法,给出控制模块的VHDL语言描述。 关键词:单片机 冗余容错 时钟 总线 VHDL 本文提出一种

表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复

杂的机间通讯协议实现系统重构,不太注重系统的实时性。本方案结构简单,易于实现,具有极强的实时性,

没有电子开关切换总线的咔嗒声输出。单片机价格低廉、功能灵活,也使得该设计在类似仪器仪表的小系统中

的运用成为可能。 1 设计原理 设计结构如图1所示。完成整个冗余设计的电路被置于一个核心

摘要: 摘要:以三个单片机组成的系统为例介绍一种单片机多机冗余容错设计。阐述设计中关键的时钟同步技术和总线仲裁方

法,给出控制模块的VHDL语言描述。

关键词:关键词:单片机 冗余容错 时钟 总线 VHDL

本文提出一种表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复杂

的机间通讯协议实现系统重构,不太注重系统的实时性。本方案结构简单,易于实现,具有极强的实时性,没有电子开关切换

总线的咔嗒声输出。单片机价格低廉、功能灵活,也使得该设计在类似仪器仪表的小系统中的运用成为可能。

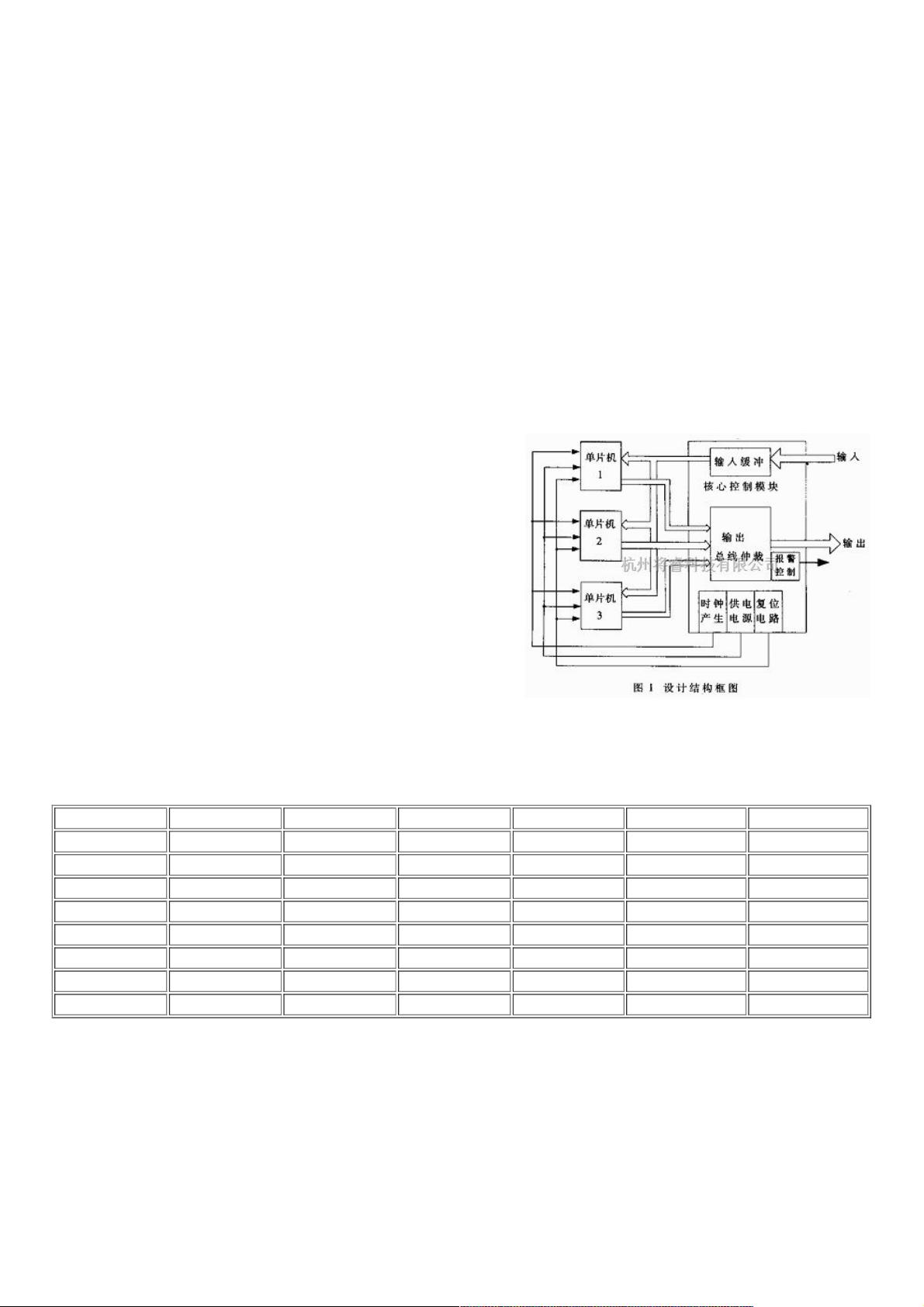

1 设计原理设计原理

设计结构如图1所示。完成整个冗余设计的电路被置于一个核心控制

模块中,如果该模块以FPGA实现也就是一块芯片。图1中单片机1、2、

3被假定为冗余的三个单片机,它们的输入总线并联,接收核心控制模块

中输入缓冲的输出。输出总线分别接到模块的输出总线仲裁器。核心控

制模块包括输入缓冲、输出总线仲裁、电源控制、时钟产生、复位电路

和报警控制输出六个部分。

1.1 输入缓冲

为了消除输入端并联输入阻抗带来的影响,在输入端增加了一级缓

冲器,减小外围电路的影响。采用输入缓冲,可以实现单片机和外围电

路的输入隔离。

1.2 输出总线仲裁

该总线仲裁是建立在所有单片机在时钟级上同步的基础上,通常采用总线表决法。即相同输出总线上的值作为仲裁的结构

输出,不同输出总线被当作出错而封止,所有的输出皆不相同同是失败状态,无表决输出。表决的实现当然不能采用软件比

较,以三个单片机系统的一位为例介绍表决方法。假设位输入变量X1、X2、X3,输出Q,状态指示:正常N、X1出错E1、X2

出错E2、X3出错E3。真值表如表1所示,位仲裁单元如图2所示。

表表1 真值表真值表

X1 X2 X3 Q E1 E2 E3

0 0 0 0 0 0 0

0 0 1 0 0 0 1

0 1 0 0 0 1 0

0 1 1 1 1 0 0

1 0 0 0 1 0 0

1 0 1 1 0 1 0

1 1 0 1 0 0 1

1 1 1 1 0 0 0

显然以上位单片机用数字电路难实现,后面给出整体的VHDL语言描述。总线仲裁由多个这样的位单元组成,个数由单片机输

出总线的最大数n决定。仲裁器除了n根输出线,同时还对每个位单元的状态位进行逻辑组合输出正常、出错、失败三个状态

指示。失败信号也用作报警保护控制输出,或重新复位输出。失败输出有效时输出失效。

以三个单片机的系统为例,如果将仲裁器的三个总线某一时刻输入看作为n位二进制变量X,Y,Z。如果X,Y,Z在任何时钟

都逐位相同,而系统处于正常工作状态。如果三者中有两个变量逐位相同,而另一个不同,则系统处于出错状态。如果三者皆

不相则系统失败。正常和出错状态可以运行,而失败状态必须保护和处理。

FPGA技术的发展,使得设计中的比较、决策等数字电路的设计实现变得非常容易,而且系统简明可靠。如果采用中规模集成

电路来实现的话,将相当烦琐和复杂。

1.3 单片机时钟级同步的实现

系统的所有单片机必须达到时钟级的同步。单片机选用相同的型号(可以是不同的厂家),完全相同的程序和同一机器时

钟。

weixin_38515362

- 粉丝: 3

- 资源: 946

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于matlab实现首先研究了语音激活检测算法

- 基于matlab实现人工蜂群算法优化无刷直流电机PID控制,并采用三种评价指标函数IAE、ITAE、ITSE来进行对比分析

- 《vue.js实战开发系列》 课件.rar

- 基于matlab实现水声通信中海洋噪声的仿真,wenz测量的噪声谱线级,噪声估计MATLAB.rar

- 基于matlab实现通过PID调节器实现炉温控制,原理图+matlab源码+matlab仿真.rar

- 基于matlab实现遗传算法的BP网络设计,应用背景为交通流量的预测.rar

- 基于matlab实现遗传算法优化BP神经网络,通过遗传算法对BP神经网络进行优化.rar

- java-leetcode面试题解Stack之第1047题删除字符串中的所有相邻重复项-题解.zip

- java-leetcode面试题解Stack之第232题用栈实现队列-题解.zip

- java-leetcode面试题解Stack之第225题用队列实现栈-题解.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0