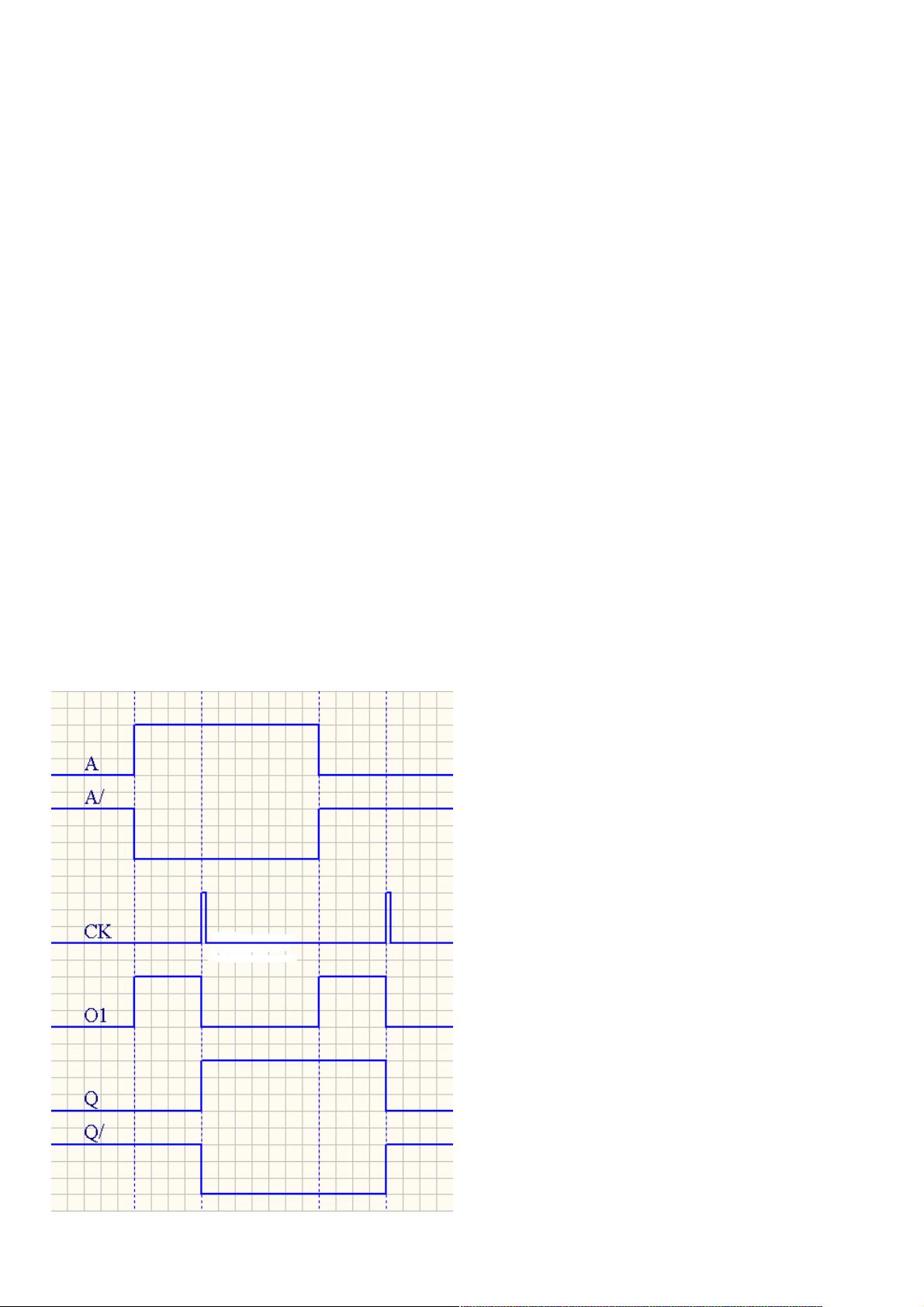

Kicker电源是“九五”国家重大科学工程之一兰州重离子加速器冷却储存环(HIRFL-CSR)的注入引出系统中一个重要组成部分[1] ,电源系统共包括六个分电源,它们需从共同的信号源接收信号,由于要求它们接收到的信号为同步信号而又因为地理位置致使其接收的信号是不可能完全同步的,为使其接收到同步信号需要在各分电源前端各配置一高速脉冲数字延迟线。 【基于CPLD的高速可程控数字延迟线系统的设计】 在现代电子系统尤其是高精度科学设备中,如“九五”国家重大科学工程兰州重离子加速器冷却储存环(HIRFL-CSR)的注入引出系统,同步信号的处理至关重要。Kicker电源作为该系统的一部分,需要六个分电源接收来自同一信号源的同步信号。然而,由于地理位置差异,这些信号无法做到绝对同步。为解决这个问题,每个分电源前端都需要配置高速脉冲数字延迟线,以调整信号到达的时间,确保同步。 数字延迟线是一种能够将电信号延迟一定时间的元件,常用于雷达、计算机、电视系统、通信和测量设备等。延迟线的基本要求是延迟时间可调且范围广,例如5ns到300ns。在高速、实时的测控领域,复杂可编程逻辑器件(CPLD)因其纳秒级的时钟延迟、并行工作模式、高集成度、高可靠性和片上系统(SoC)能力而被广泛应用。随着EDA技术的发展,CPLD在速度、集成度、功能和灵活性方面不断进步,成为实现高速可程控数字延迟线的理想选择。 数字延迟线的工作原理通常基于两个参数相同的延迟模块来延迟脉冲的上升沿和下降沿。然而,实际中难以找到完全一致的延迟模块,导致延迟精度不高。为提高精度和降低成本,本文提出了一种新的设计思路:使用单一延迟模块同时处理脉冲的前后沿,通过逻辑控制电路和反馈网络结构实现。这种方法使得延迟线结构更加紧凑,性能更稳定。 具体实现中,数字延迟线的电路包括延迟模块、逻辑控制模块和可逆计数器模块。输入信号A及其反相信号 通过逻辑控制模块选择输出O1,当O1上升沿到来时,可逆计数器开始计数。计数器的输出CK触发T触发器,使得输出端Q的电平发生变化,从而延迟输入信号A。T触发器的输出Q同时作为逻辑控制模块的控制信号,确保信号的正确选择和传输。在输入信号A上升沿时,计数器开始减计数,当计数至预设值时,输出CK上升沿触发T触发器反相,完成一次延迟过程。在下降沿到来时,同样的机制使得计数器重新预置,保持系统的同步。 采用CPLD实现的数字延迟线系统,不仅可以精确调整延迟时间,还能简化电路设计,提高系统的可靠性,并有助于系统的小型化和数字化。这种设计方法对于满足像HIRFL-CSR这样的大型科学工程中的同步信号处理需求具有重要的实际意义。

- 粉丝: 3

- 资源: 963

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功