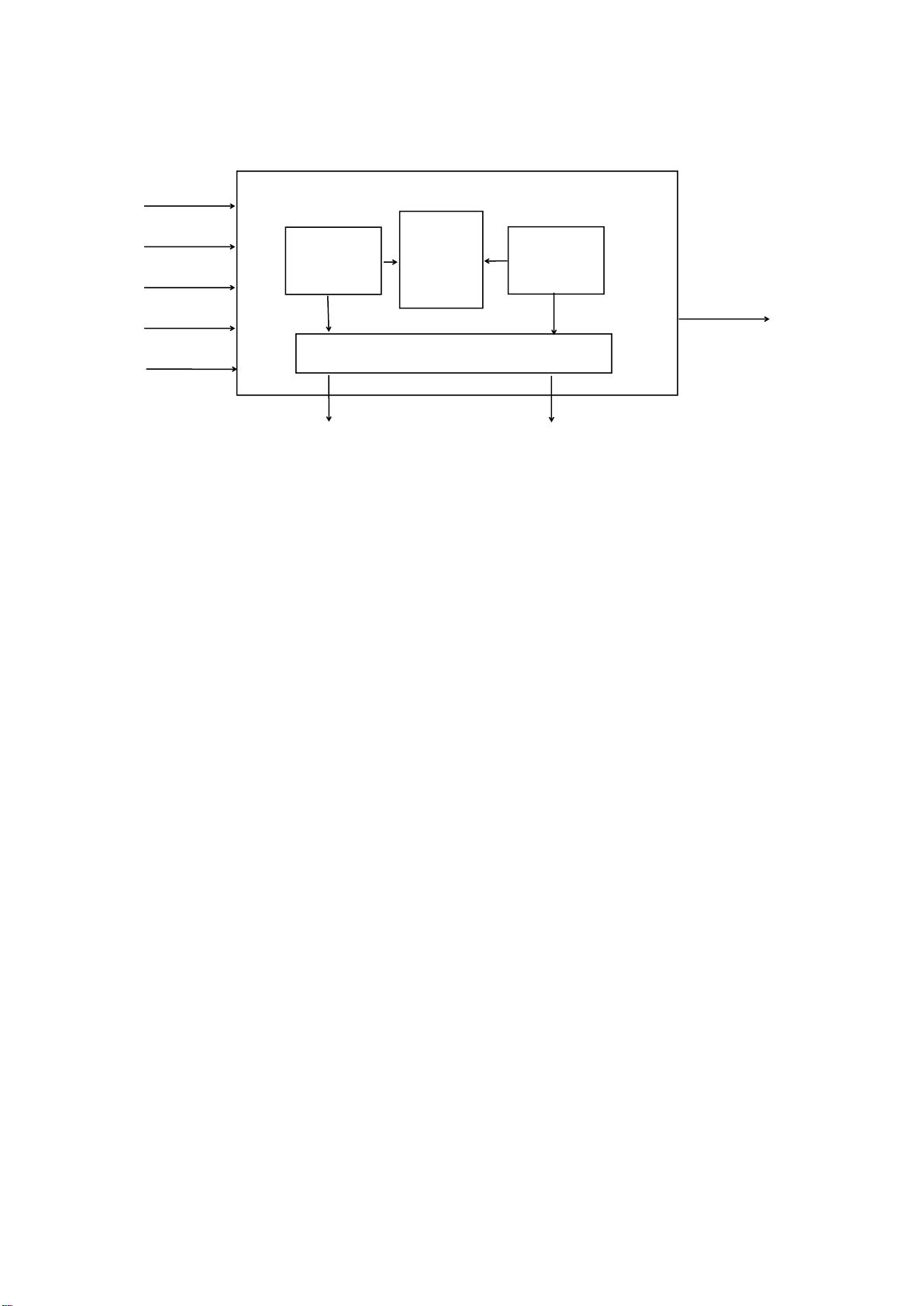

同步 fifo

Verilog 代码部分

module syn_fifo #(

parameter DSIZE = 16,

ASIZE = 8

)

(

input clk, rst, ren, wen,

input [DSIZE-1:0] wdata,

output [DSIZE-1:0] rdata,

output wfull,rempty

);

reg [ASIZE-1:0] waddr, raddr, rdata_cnt;

wire read_only,write_only;

always@(posedge clk or negedge rst) begin

if (~rst)

{waddr,raddr}<=0;

else begin

raddr<=raddr+(ren & ~rempty);

waddr<=waddr+(wen & ~wfull);

end

end

always@(posedge clk or negedge rst) begin

if(~rst)

rdata_cnt<=0;

else if(write_only)

rdata_cnt<=rdata_cnt+1’b1;

else if(read_only)

rdata_cnt<=rdata_cnt-1’b1;

end

assign rempty=(rdata_cnt==0);

assign wfull =(rdata_cnt==8’hff);

assign read_only=(ren & ~rempty)&(~(wen & ~wfull));

assign write_only=(wen & ~wfull)&(~(ren & ~rempty));

fifomem #(DSIZE,ASIZE)

fifomem_inst(

.rst (rst),

.clk(clk),

评论0

最新资源