2

CDCE62005

SCAS862G –NOVEMBER 2008–REVISED JULY 2016

www.ti.com

Product Folder Links: CDCE62005

Submit Documentation Feedback Copyright © 2008–2016, Texas Instruments Incorporated

Table of Contents

1 Features.................................................................. 1

2 Applications ........................................................... 1

3 Description ............................................................. 1

4 Revision History..................................................... 2

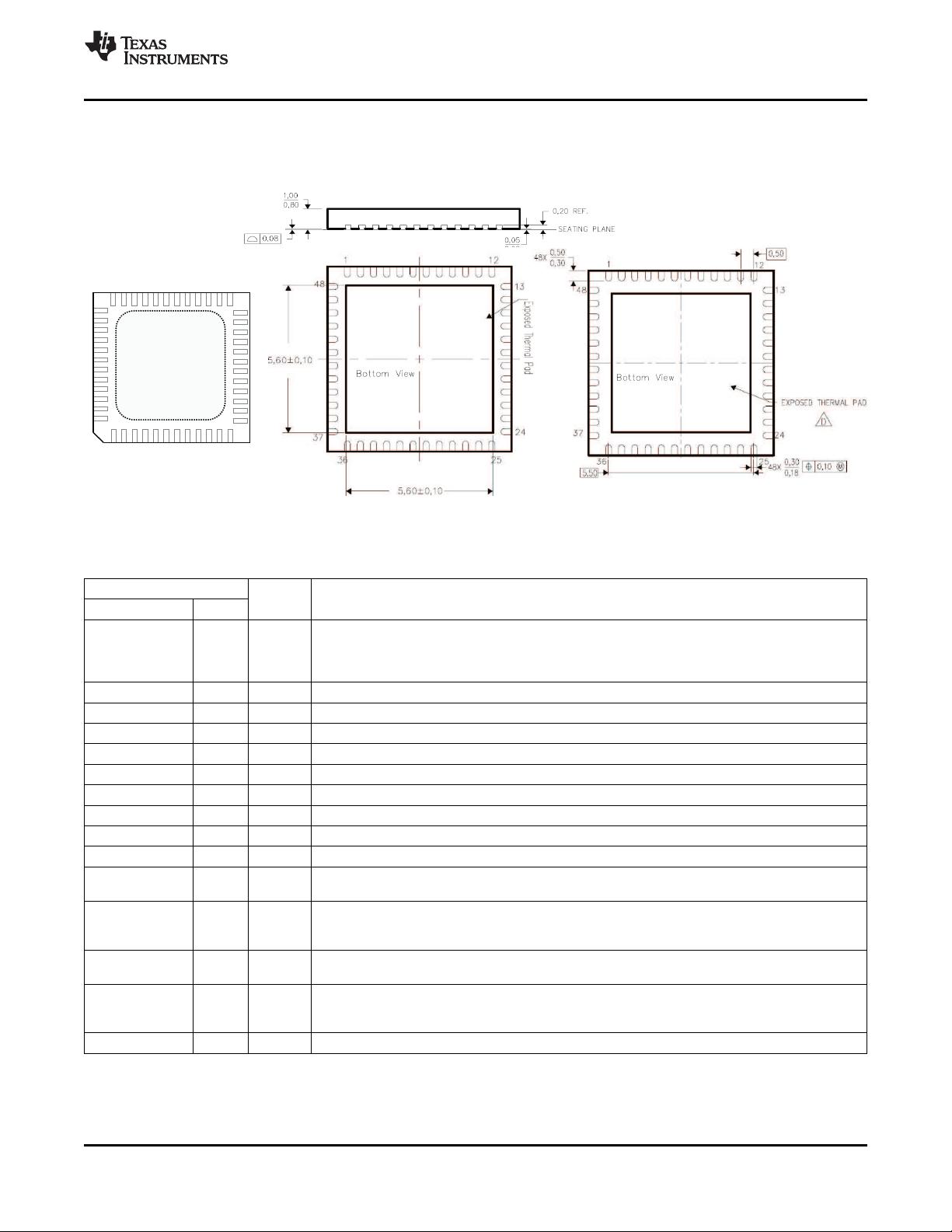

5 Pin Configuration and Functions......................... 4

6 Specifications......................................................... 6

6.1 Absolute Maximum Ratings ...................................... 6

6.2 ESD Ratings.............................................................. 6

6.3 Thermal Information.................................................. 6

6.4 Electrical Characteristics........................................... 7

6.5 Timing Requirements.............................................. 11

6.6 SPI Bus Timing Characteristics .............................. 11

6.7 Typical Characteristics............................................ 12

7 Parameter Measurement Information ................ 13

8 Detailed Description............................................ 14

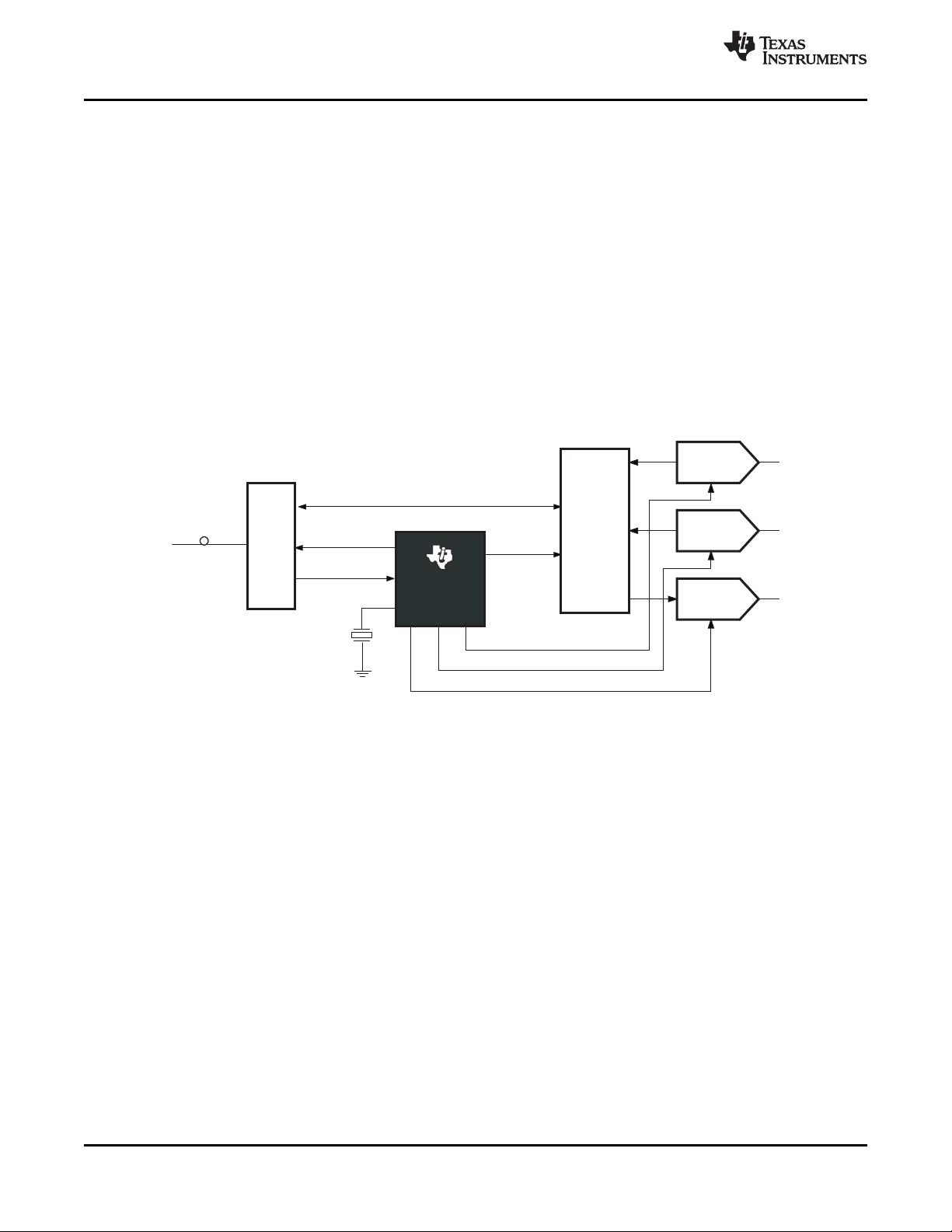

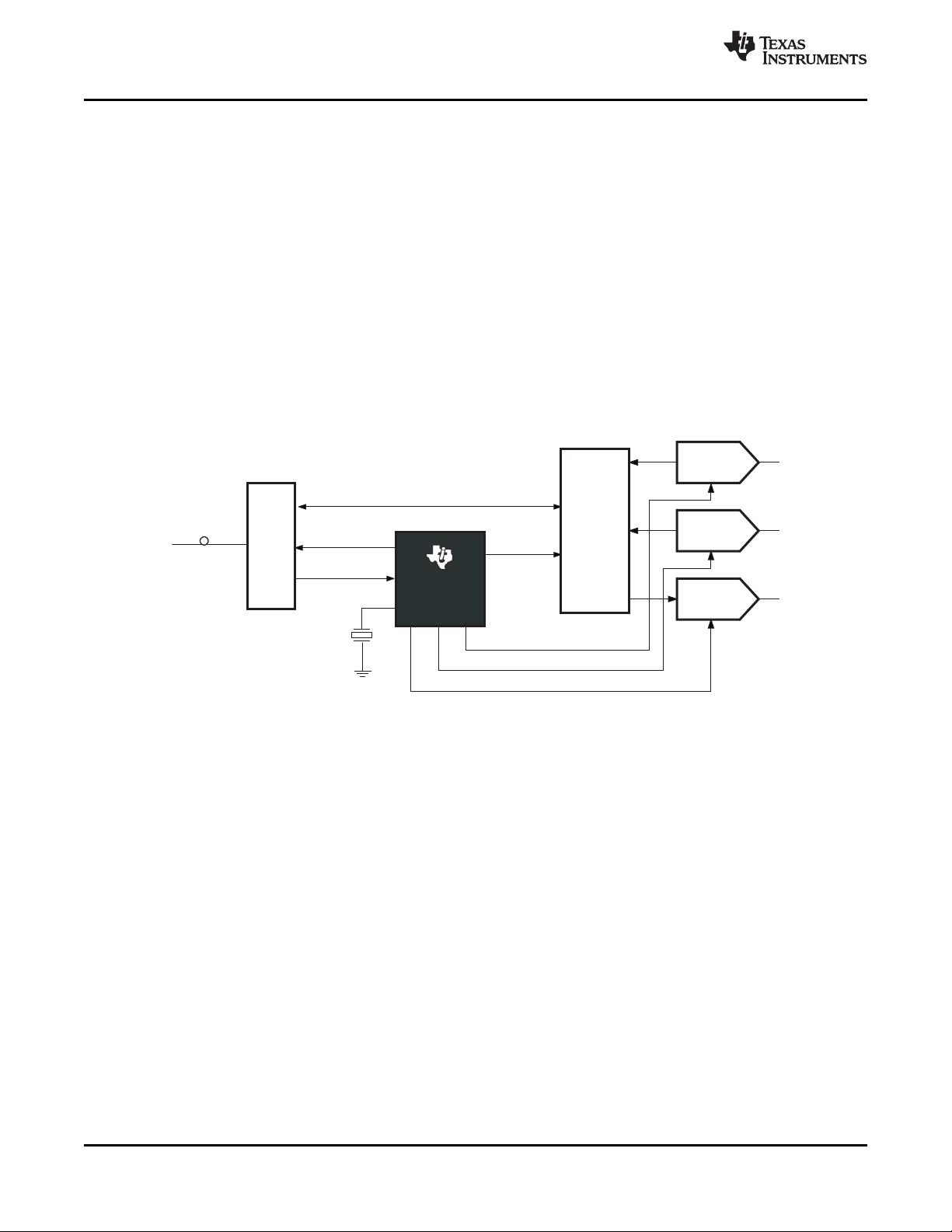

8.1 Overview ................................................................. 14

8.2 Functional Block Diagrams ..................................... 14

8.3 Feature Description................................................. 20

8.4 Device Functional Modes........................................ 52

8.5 Programming........................................................... 55

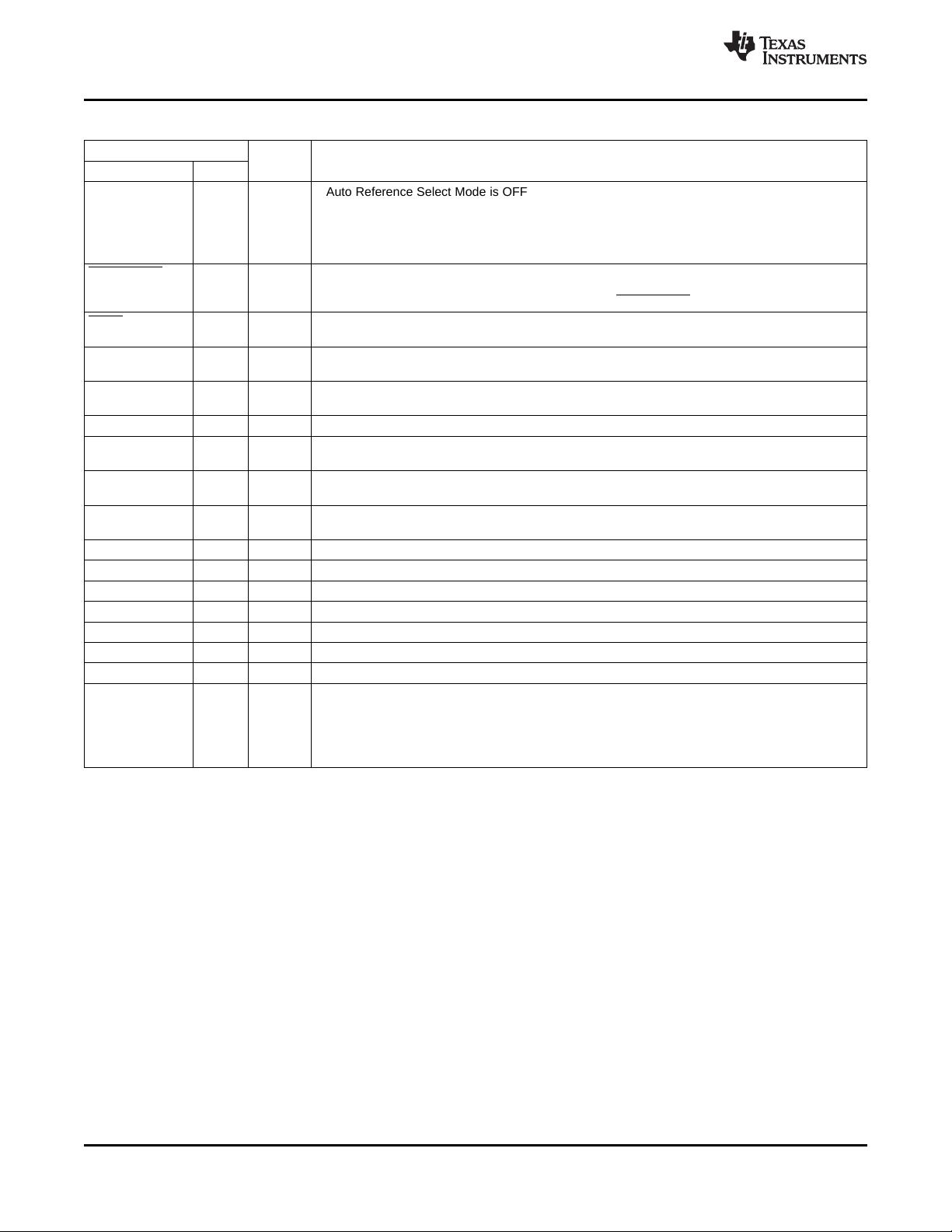

8.6 Register Maps......................................................... 61

9 Application and Implementation ........................ 70

9.1 Application Information............................................ 70

9.2 Typical Application .................................................. 70

10 Power Supply Recommendations ..................... 74

11 Layout................................................................... 76

11.1 Layout Guidelines ................................................. 76

11.2 Layout Example .................................................... 76

12 Device and Documentation Support ................. 77

12.1 Trademarks........................................................... 77

12.2 Documentation Support ........................................ 77

12.3 Electrostatic Discharge Caution............................ 77

12.4 Glossary................................................................ 77

13 Mechanical, Packaging, and Orderable

Information ........................................................... 77

4 Revision History

Changes from Revision F (January 2015) to Revision G Page

• Removed minimum and maximum values and added typical value to on-chip load capacitance in Electrical

Characteristics ....................................................................................................................................................................... 7

Changes from Revision E (July 2014) to Revision F Page

• Added Low Noise Clock Generator: 550 fs rms typical (10 kHz to 20 MHz Integration Bandwidth), F

C

= 100 MHz in

Features section ..................................................................................................................................................................... 1

• Added Low Noise Jitter Cleaner: 2.6 ps rms typical (10 kHz to 20 MHz Integration Bandwidth), F

C

= 100 MHz in

Features section ..................................................................................................................................................................... 1

Changes from Revision D (April 2011) to Revision E Page

• Changed Added, updated, or revised the following sections: Features; Application and Implementation; Power

Supply Recommendations ; Layout ; Device and Documentation Support ; Mechanical, Packaging, and Ordering

Information ............................................................................................................................................................................. 1

• Changed Bit Name from LOCKW(3) to LOCKW(2).............................................................................................................. 48

• Changed Bit Name from LOCKW(2) to LOCKW(1).............................................................................................................. 48

• Changed Bit Name from LOCKW(1) to LOCKW(0).............................................................................................................. 48

• Changed REGISTER.BIT from 5.26 to 5.25, from 5.25 to 5.24, from 5.24 to 5.23, from 5.23 to 5.22. .............................. 48

Changes from Revision C (February, 2010) to Revision D Page

• Changed 0 to 1 in SPI_LE description ................................................................................................................................... 4

• Changed last sentence in Description column of Pin 46 and Pin 2 ....................................................................................... 5

• Changed Outputs to Output 1 in P

LVCMOS

Test Conditions, changed PD to Power_Down in LVCMOS INPUT MODE,

and deleted (LVCMOS signals) from Input capacitance in Electrical Characteristics............................................................ 7

• Changed TIMING REQUIREMENTS table........................................................................................................................... 11

• Added 1 row to TIMING Requirements table - Input Clock Slew Rate... ............................................................................. 11