更多技术文章:http://www.edadoc.com

全球最大的高速 PCB 设计中心

设计-制板-贴片-元器件供应一站式平台

1、搜索微信号“高速先生”

2、扫描右侧二维码,开始学习

【高速先生原创|DDR 系列】DDRX 的关键技术介绍(下)

DDRX 的关键技术介绍(下)

今天要介绍的是 DDR3 和 DDR4 最关键的一些技术,write leveling 以及 DBI 功能。

Write leveling 功能与 Fly_by 拓扑

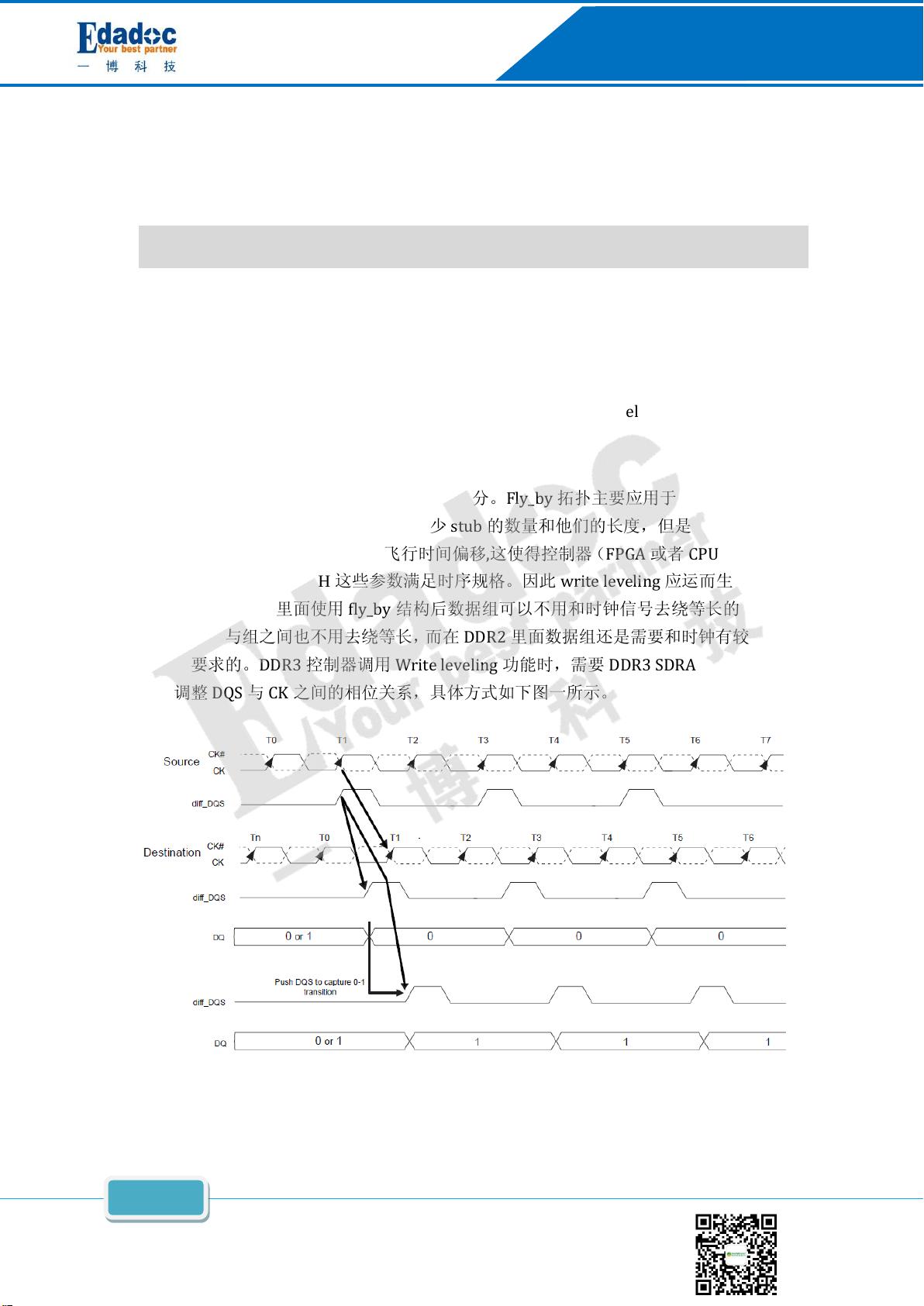

Write leveling 功能和 Fly_by 拓扑密不可分。Fly_by 拓扑主要应用于时钟、地址、

命令和控制信号,该拓扑可以有效的减少 stub 的数量和他们的长度,但是却会导致时

钟和 Strobe 信号在每个芯片上的飞行时间偏移,这使得控制器(FPGA 或者 CPU)很难保

持 tDQSS、tDSS 和 tDSH 这些参数满足时序规格。因此 write leveling 应运而生,这也

是为什么在 DDR3 里面使用 fly_by 结构后数据组可以不用和时钟信号去绕等长的原因,

数据信号组与组之间也不用去绕等长,而在 DDR2 里面数据组还是需要和时钟有较宽松

的等长要求的。DDR3 控制器调用 Write leveling 功能时,需要 DDR3 SDRAM 颗粒的反

馈来调整 DQS 与 CK 之间的相位关系,具体方式如下图一所示。

图一、 Write leveling

评论0

最新资源