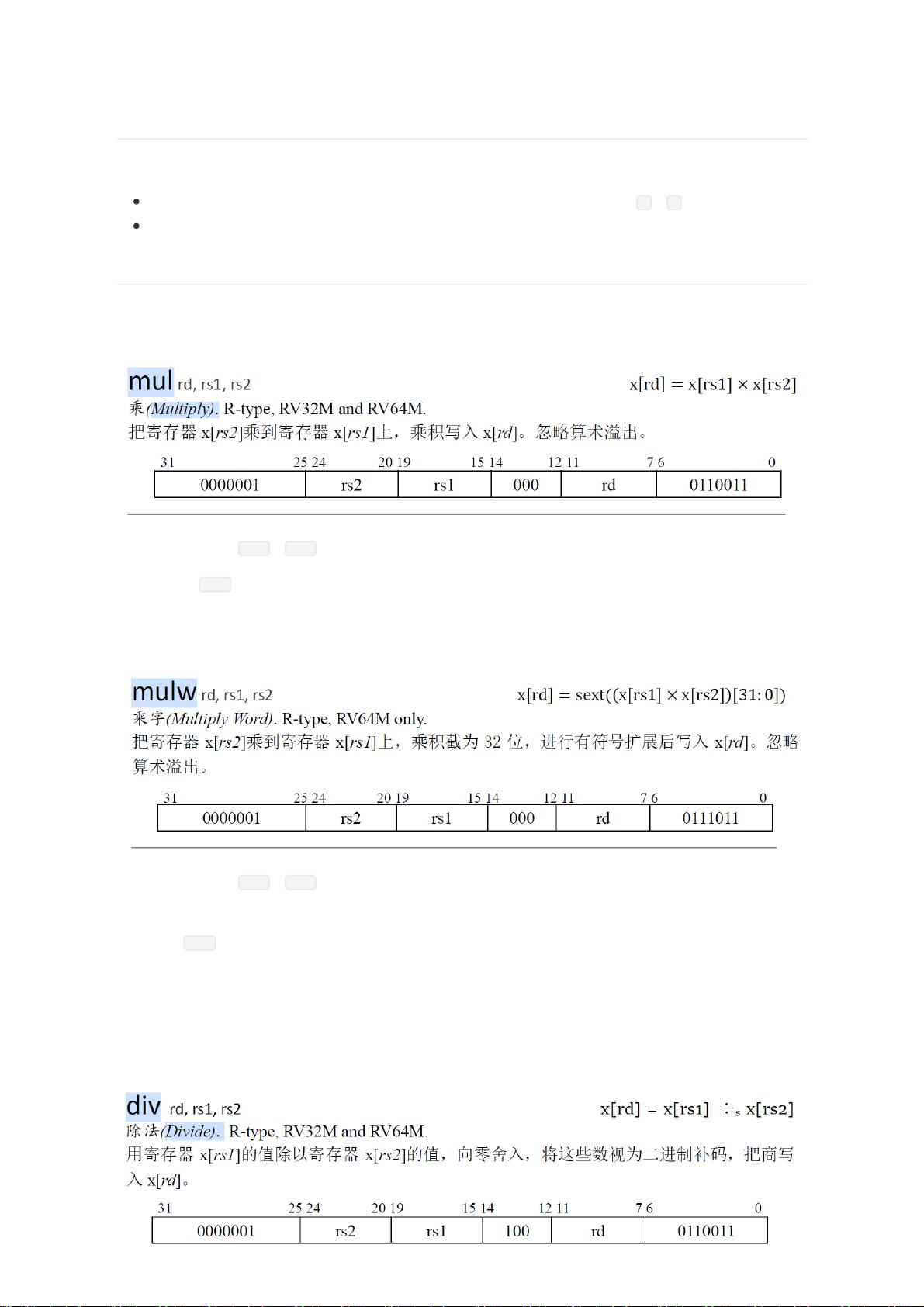

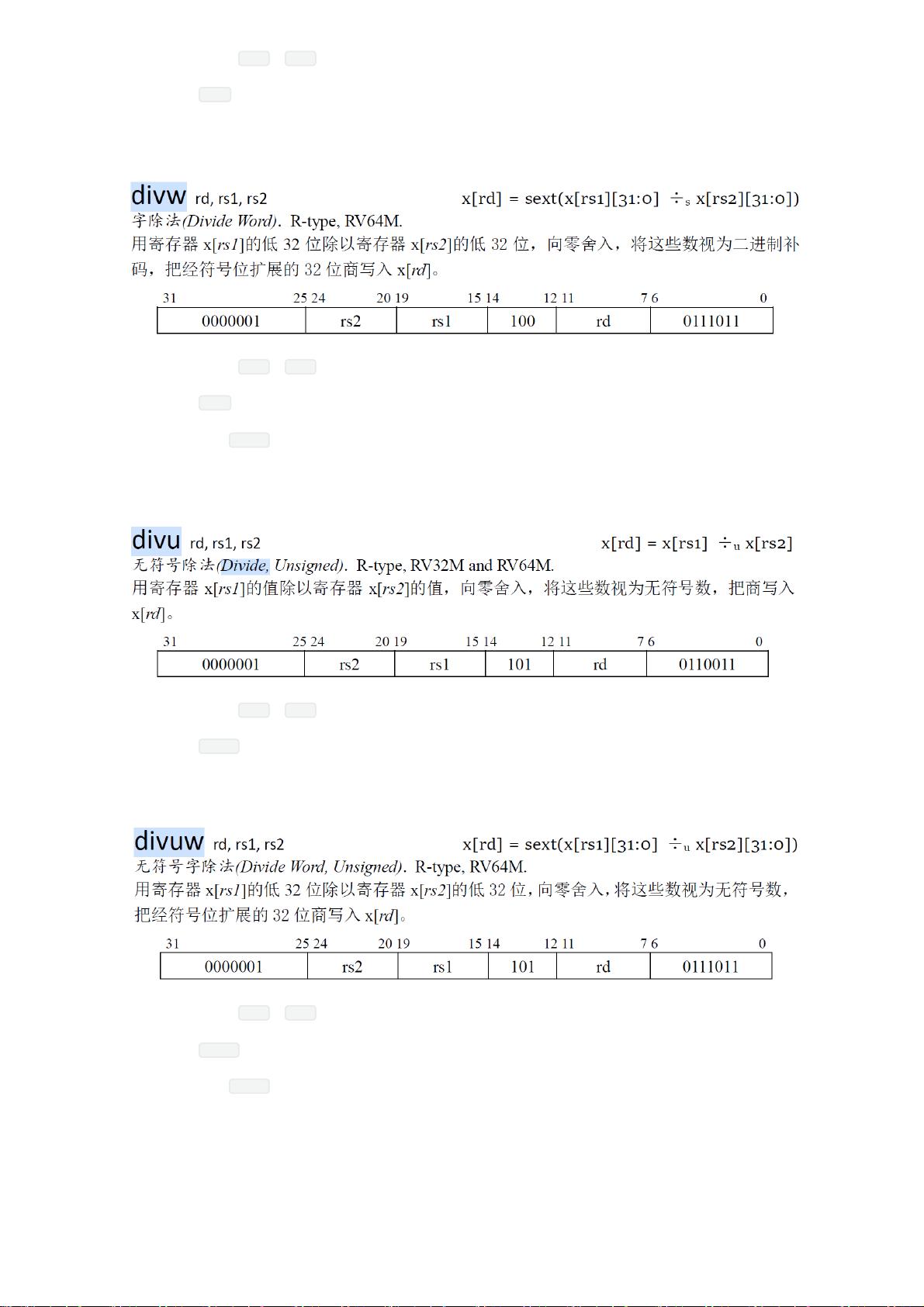

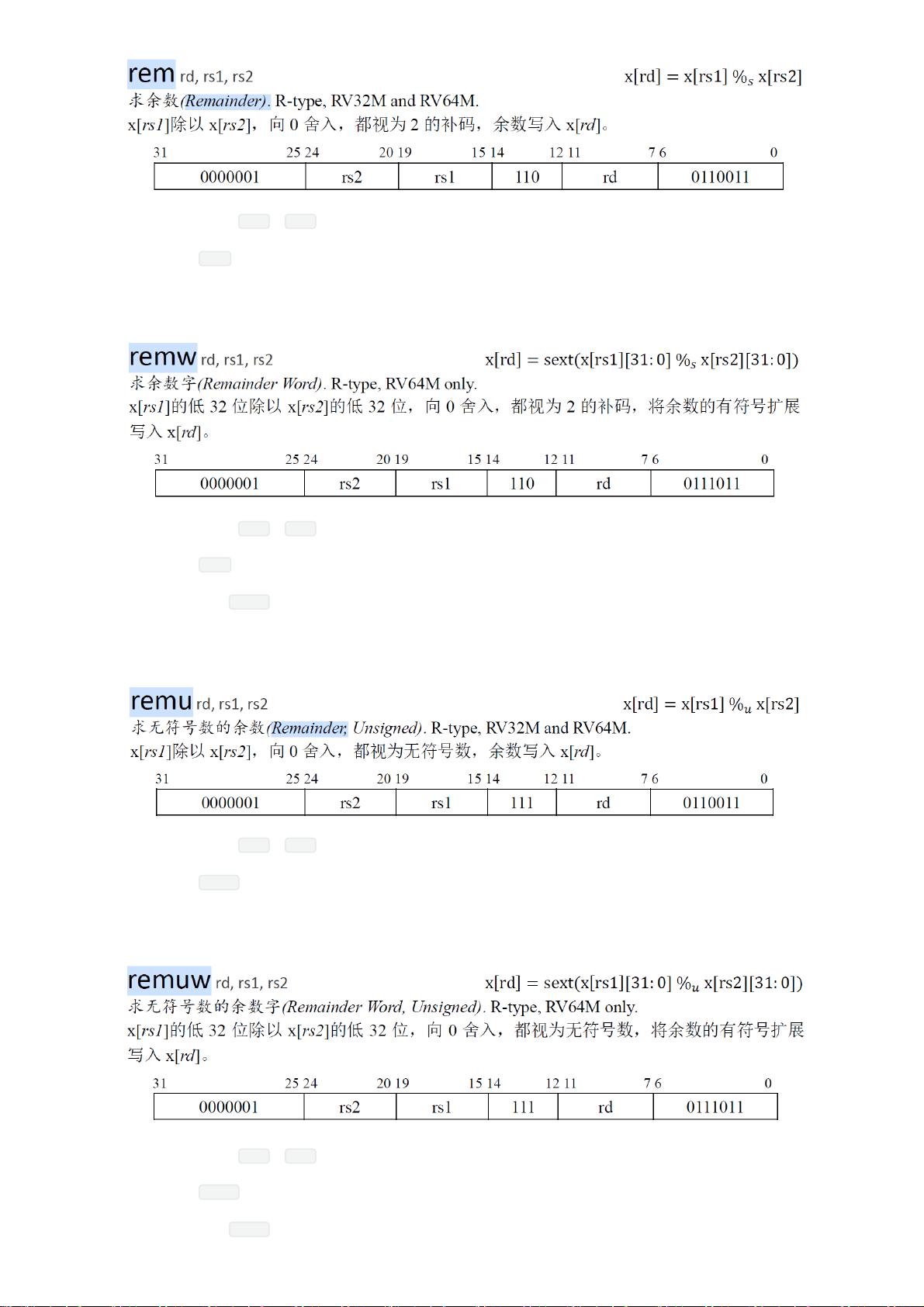

在本文中,我们将深入探讨RISC-V架构中实验室3(Lab 3)的分析与设计,主要关注缓存参数、缓存的端口设计以及缓存的状态转化与行为。此外,我们还将讨论如何为RISC-V处理器添加乘除法指令以及ALU的改进。 让我们来了解新增的乘除法指令。在RISC-V指令集架构中,Lab 3要求实现6个乘法指令(mul、mulw)和4个除法指令(div、divw、divu、divuw),以及相应的取模运算(rem、remw、remu、remuw)。这些指令均基于R-type格式,将两个寄存器中的数据进行运算,并将结果写入目标寄存器。乘法指令使用了MUL和MULW操作,除法指令使用DIV和DIVW,而无符号版本使用DIVU和DIVUW。取模运算对应MOD和MODW,无符号取模则对应MODU和MODUW。这些指令的处理逻辑涉及到数据截取、符号扩展和乘法/除法运算。 接下来,为了支持这些新的运算,ALU需要进行改进。传统的ALU通常处理简单的算术和逻辑运算,但乘除法运算需要更复杂的硬件,即多周期的乘法器(multiplier)和除法器(divider)。这两种运算器通过有限状态机控制,使用竖式计算的逻辑来实现电路计算。乘法器和除法器的输入输出端口包括时钟信号、复位信号、有效信号、操作数以及计算结果等。ALU需要调整为时序逻辑,接收同步时钟信号,并在乘法或除法运算时与运算器进行握手通信。例如,当检测到乘法操作时,ALU会启动乘法器并等待done信号,表明运算完成,然后处理下一条指令。 缓存是处理器优化访问主内存的关键组件。在Lab 3中,我们需要关注缓存的参数,这可能包括缓存的大小(如字节数)、块大小(line size)、缓存行的数量、替换策略(如LRU或随机)、以及缓存的层次结构(如L1、L2缓存)。缓存的端口设计则涉及读写端口的数量、地址映射方式(如直接映射、全相联映射或组相联映射)、缓存状态(如空、满、脏、命中、未命中)的管理。缓存的状态转化与行为包括读取数据时的命中与未命中处理、写回策略(如写通、写回、写分配)以及缓存一致性协议(如MESI或MOESI)的应用,尤其是在多核系统中。 为了实现缓存,我们需要考虑以下步骤: 1. 定义缓存的大小和结构。 2. 设计地址映射函数,将虚拟地址映射到缓存中的位置。 3. 实现缓存的替换策略,决定何时替换旧的数据块。 4. 设计读写操作的流程,包括缓存命中和未命中的处理。 5. 实现写回策略,处理写操作。 6. 如果是多核环境,还需处理缓存一致性问题。 Lab 3不仅涉及RISC-V处理器的指令集扩展,还涵盖了缓存系统的设计,这些都是计算机体系结构中的核心概念。通过这个实验,学生可以深入理解处理器性能优化的关键技术,并学习如何在实际设计中应用这些技术。

剩余18页未读,继续阅读

- 粉丝: 25

- 资源: 300

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Ashampoo WinOptimizer v27.00.05 阿香婆一款专业的垃圾清理、碎片整理启动项管理系统优化工具.rar

- misc设备驱动 正点原子阿尔法

- youleng-wms JAVA开发的WMS源码可以借签学习 数据库MYSQL

- 385大神asp.net三层设计停车场管理系统毕业课程源码设计+参考论文

- 数据集,训练数据集,深度学习

- 384大神asp.net基于三层汽车进销存销售管理系统毕业课程源码设计

- AutoSAR基础学习资源

- 383大神asp.net软件测试用例库管理系统毕业课程源码设计

- Open-Industry-Project-main C#

- C0858 手机之家(1页).Zip

信息提交成功

信息提交成功

评论0