3-异常与中断1

需积分: 0 64 浏览量

更新于2022-08-03

收藏 1.49MB PDF 举报

异常与中断是处理器中至关重要的概念,它们是处理器与外部世界交互、处理突发事件以及调度任务的关键机制。在本文中,我们将深入探讨RISC-V架构下的异常和中断处理,特别是基于平头哥E902处理器的SoC设计,如无剑100 SoC。

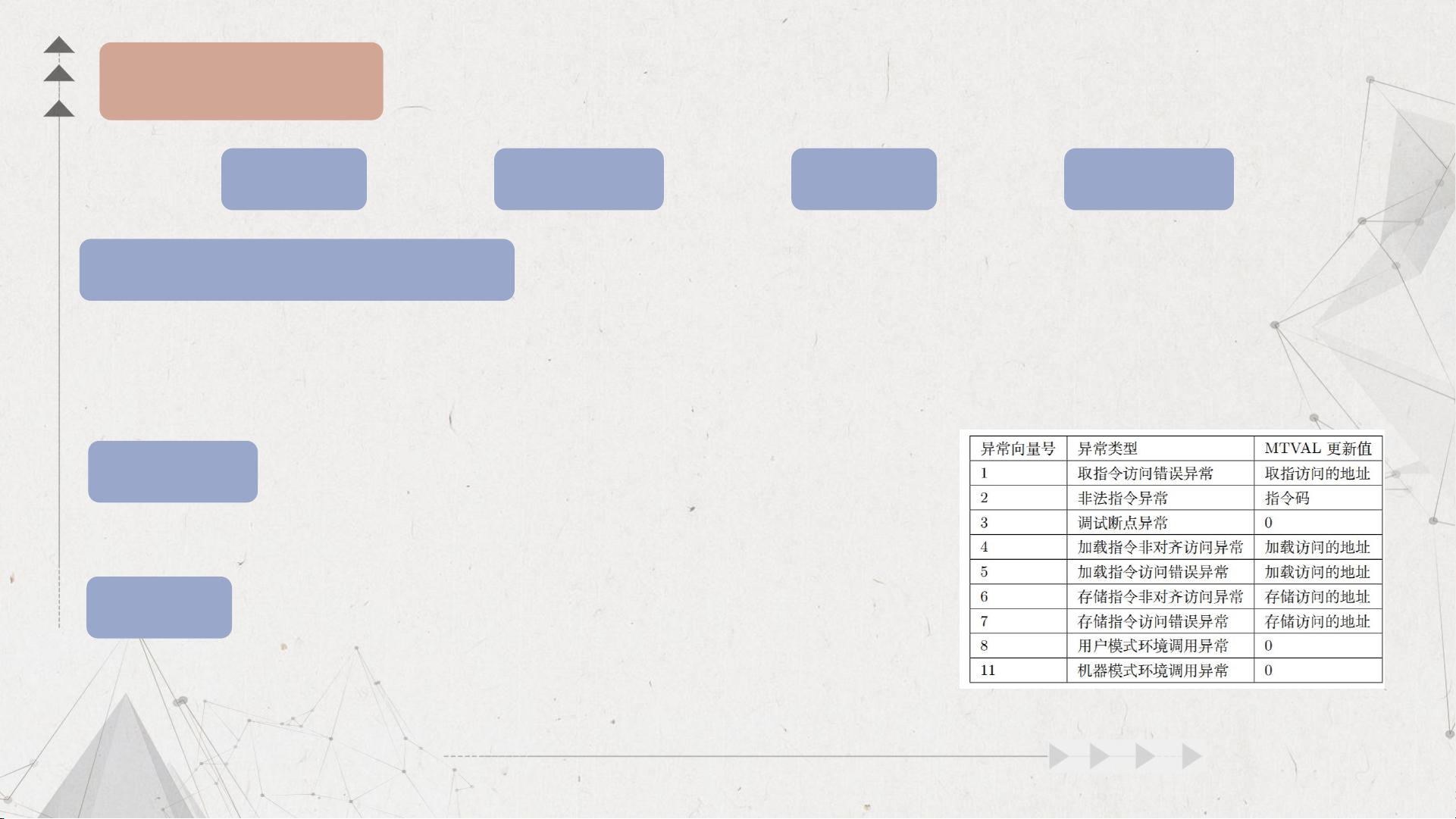

在RISC-V编程模型中,异常和中断被视为广义上的异常事件。异常通常包括内部事件,如非法指令、非对齐访问错误或执行特定的系统服务指令(如ecall、ebreak),而中断则是由外围硬件设备产生的外部请求。一旦发生异常或中断,当前程序的执行会被立即打断,处理器会按照预定义的机制进行响应。

异常响应的过程在RISC-V架构中是高度规范化的。当异常发生时,硬件会自动执行一系列操作,包括更新特定的控制和状态寄存器,如mcause、mtval、mepc和mstatus。mcause寄存器记录异常或中断的原因,mtval寄存器存储异常的具体信息,如错误地址。mepc寄存器保存了异常发生时的程序计数器(PC)值,以便在异常处理完成后恢复程序执行。mstatus寄存器则记录了处理器的状态,如MIE(Machine Interrupt Enable)域控制全局中断的开启和关闭,MPP(Machine Previous Privilege Mode)域记录了异常发生前的工作模式。

异常响应时,处理器会跳转到由MTVEC(Machine Trap-Vector Base-Address Register)寄存器指定的地址开始执行。MTVEC定义了异常处理的入口,使得可以根据异常向量号跳转到对应的处理程序。需要注意的是,RISC-V不支持硬件自动保存和恢复上下文,因此异常服务程序需要显式地保存和恢复通用目的寄存器(GPR)和其他必要的寄存器。

在无剑100 SoC中,异常处理通常由一个默认的服务函数Default_Handler执行。这个函数首先会检查是否有中断发生,如果有,则优先处理中断。接着,它会保存上下文,将GPR等寄存器压入堆栈,然后调用trap_c函数,通过a0寄存器传递堆栈指针。trap_c函数负责通过串口输出异常信息,以便调试。

异常服务程序的返回是通过MRET指令实现的,它恢复CPU现场,包括将PC设置回mepc的值,继续执行被异常中断的指令。在处理某些特定异常,如ecall和ebreak时,为了避免无限循环,需要在返回前修改mepc的值,使其指向下一条指令。

异常服务程序的设计和实现是关键,因为它直接影响到系统的可靠性和性能。开发者需要自定义trap_c函数来满足特定的需求,如错误诊断、故障恢复和任务切换。此外,对于中断服务程序,还需要确保在返回前处理完中断事件,避免再次触发异常。

总结起来,RISC-V异常和中断机制的核心在于其规范化的响应流程和软件驱动的上下文管理。理解和熟练掌握这些机制对于开发基于RISC-V的SoC系统至关重要,因为它们是保证系统正确运行和高效响应外部事件的基础。在实际应用中,开发者需要根据具体需求编写异常和中断处理代码,以确保系统的稳定性和灵活性。