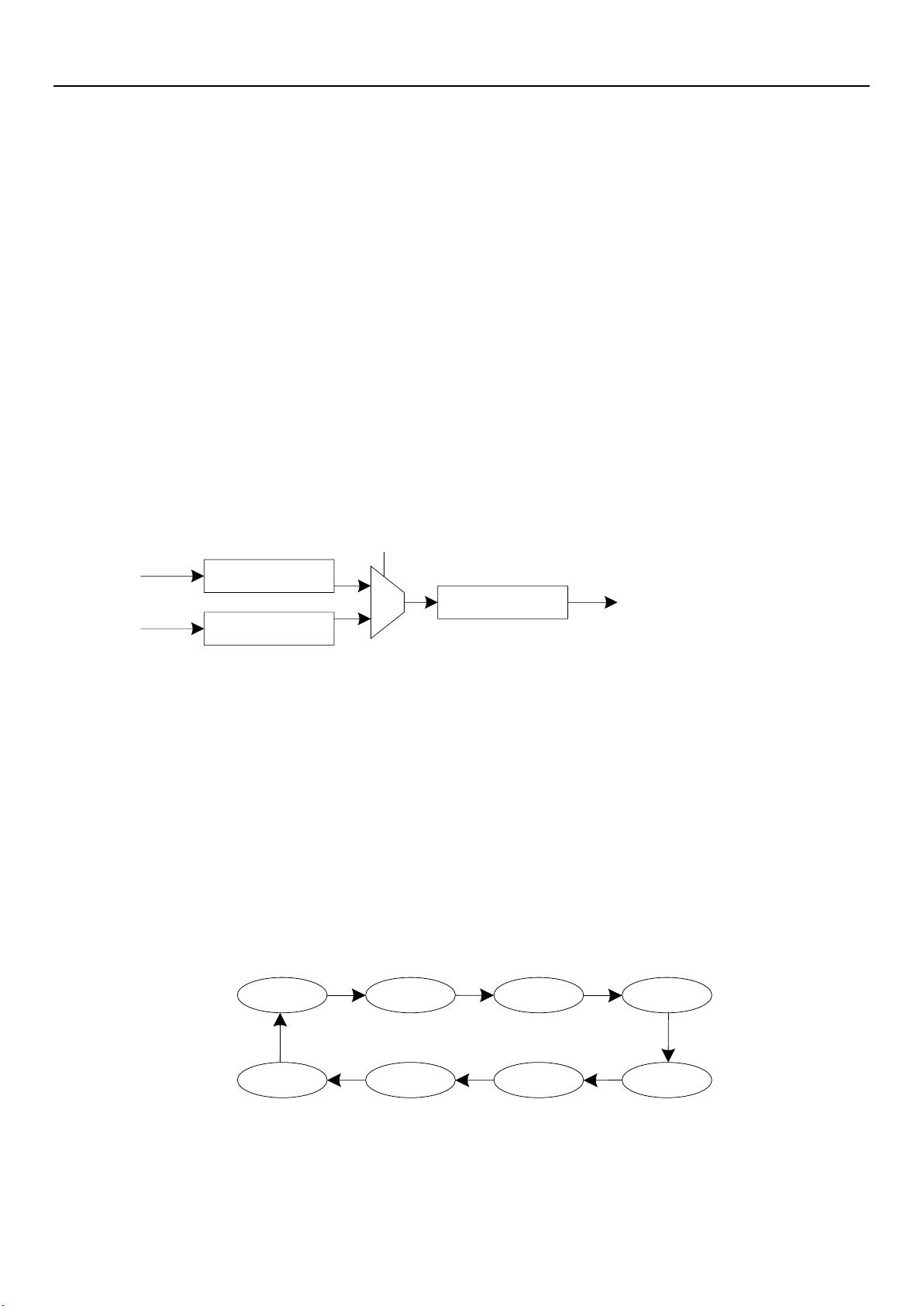

【序列检测器1】实验主要涉及FPGA开发中的序列检测器设计,这是一项在电子系统设计中至关重要的任务。实验目标包括理解并掌握信号发生器、状态机以及序列检测器的工作原理与设计方法,同时也要求熟悉VHDL语言中元件的使用及例化,以及Altera FPGA设计流程。 信号发生器是产生特定信号的设备,通常在通信、测试等领域应用广泛。在实验中,你需要用VHDL实现两个序列产生器,一个产生预设序列“111010011”,另一个则不产生。序列产生可以视为有限状态机,它具有多个状态,每个状态对应一个输出,根据状态转换规则产生序列。 状态机在本实验中扮演关键角色。序列检测器同样基于状态机原理,它接收序列产生器的输出,当检测到“111010011”序列时,输出标志为“1”,否则为“0”。设计时,你需要依据特定的状态转换图,如图3所示,用VHDL编写检测器的代码并进行仿真验证。 实验步骤包括: 1. 使用VHDL实现序列产生器模块。这涉及到状态机的设计,可以理解为没有输入信号的状态转换图,每个状态按顺序转换,产生特定的序列。 2. 编写序列检测器的VHDL代码,它接收前一步产生的序列,并通过状态机逻辑判断是否检测到目标序列。 3. 编写仿真激励VHDL Test Bench文件,模拟输入信号和时钟,确保序列检测器功能正确。时钟信号需单独产生,例如,通过定义一个过程生成20ns周期的时钟信号。 4. 添加工程约束,进行管脚分配,这通常参照Altera FPGA的文档来完成,确保设计能够在硬件上正确实现。 在实验过程中,除了基本的VHDL语法,你还需要理解如何将状态机的逻辑转化为硬件描述语言代码,并在ALTERA的开发环境中进行综合、布局布线和下载验证。这将深化你对FPGA设计流程的理解,以及如何使用VHDL进行硬件描述和测试。 通过这个实验,你可以掌握从理论到实际的FPGA设计技能,包括状态机的设计、序列检测算法的实现,以及VHDL编程和仿真技术,这些都是现代数字系统设计的基础。此外,对于信号发生器和序列检测器的实践操作,将有助于你在未来处理更复杂的数据通信和信号处理问题。

- 粉丝: 33

- 资源: 300

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 行政管理人员面试题.doc

- 行政秘书.doc

- 秘书笔试题.doc

- 01.经典行为面试题目(个人品行).doc

- 02.经典行为面试题目(认知能力).doc

- 05.素质模型与行为面试题库(销售).doc

- 06.外企面试常见问题114例(中英文对照).doc

- 12.中外知名企业的招聘典型试题精选.doc

- 13.经典行为面试题目(动力系统二).docx

- 20.行为面试法精讲精练.ppt

- 19.校园招聘及行为面试法.ppt

- 22.基于胜任力的行为面试法.pptx

- 01.20XXjava面试题全攻略.doc

- 03.IT MRPII人员考试试题.doc

- 06.JAVA-SSH面试题.doc

- 12.SQL面试题目汇总.doc

信息提交成功

信息提交成功

评论0