02_Quartus II时序优化策略1

需积分: 0 44 浏览量

更新于2022-08-03

收藏 4.69MB PDF 举报

在FPGA开发过程中,时序优化是提升设计性能的关键步骤。Quartus II是Altera公司的一款强大的FPGA设计软件,提供了多种时序优化策略来帮助开发者实现更高效的设计。以下是一些重要的时序优化技术:

1. **时钟优化**:

- 为了速度优化,应全局应用时钟。这意味着在整个设计中统一考虑时钟网络,确保时钟信号的同步性。

- 可以采用分层方法优化时钟,针对特定的时钟域进行调整,以提高特定部分的性能。

- 启用网表优化和物理综合,这两者都是时序优化的重要组成部分,可以改善逻辑门的布局和布线,进一步缩短路径延迟。

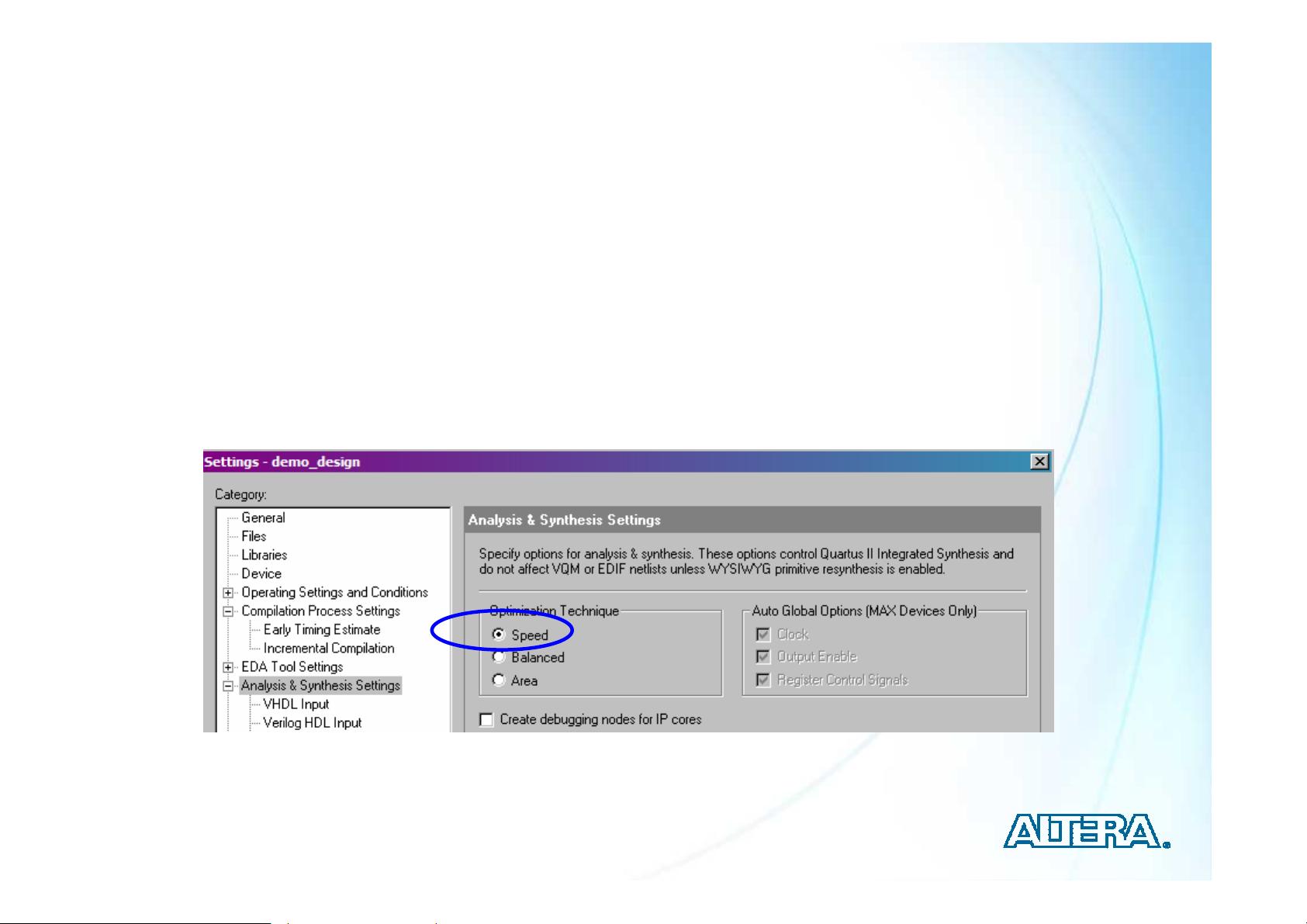

2. **全局速度优化**:

- 在Quartus II中,可以选择不同的速度设置,默认为平衡模式。对于面积优化的设计,即使牺牲一些面积,也可能获得速度上的提升。

- 这种优化可能会导致逻辑资源的使用量增加,但总体上可以提高系统的运行速度。

3. **个体优化**:

- 通过逻辑选项的优化技术,可以在分配编辑器或Tcl脚本中对层次化的模块进行单独优化,以针对性地提升特定部分的性能。

- 对于时钟域的优化,可以设定针对特定时钟域或跨时钟域的速度优化技术,确保不同域之间的时序协调。

4. **合成网表优化**:

- 在合成阶段对网表进行进一步优化,可以减少延迟并改进逻辑结构。

- 常见的优化类型包括“所见即所得”(WYSIWYG)优化、逻辑等效替换、门级并行化等,这些方法旨在压缩路径长度,提高逻辑效率。

5. **分析时序失败**:

- 在优化过程中,分析时序失败至关重要。这涉及识别违反时序约束的路径,并理解它们为何未能满足要求。

- 通过Quartus II的时序分析工具,可以定位这些问题并提出解决方案,如改变时钟树结构、增加寄存器或者重新分配逻辑资源。

6. **异步控制信号处理**:

- 异步控制信号可能导致时序问题,因为它们可能引入额外的不确定性和延迟。合理设计异步接口,使用适当的同步电路来处理这些信号,是避免时序问题的有效方法。

7. **参考资料**:

- Quartus II的时序优化顾问和手册提供了许多这些建议,开发者可以参考这些资料深入学习和实践。

在实际设计中,应结合具体项目需求和资源限制,灵活运用上述策略,以达到最佳的时序性能。同时,持续的迭代和测试也是优化过程中的重要环节,以确保优化措施确实提高了设计的时序性能。

型爷

- 粉丝: 24

- 资源: 337

最新资源

- 基于fpga的2psk调制解调器实现,代码包括quartus和vivado两个工程版本,使用到的所有滤波器全部采用matlab设计参数,verilog代码实现,没有调用滤波器ip,可以进行任意调整或者

- 提高Python网络编程实战视频教程网络抓取爬虫07socket编程基础-.avi

- FPGA GTP aurora 8b 10b视频传输 FPGA GTP全网最细讲解 aurora 8b 10b协议OV5640视频传输 提供2套工程源码和 详细设计文档参考链接:

- C语言实现串口通信的方式

- comsol磁可调双带吸收器

- 提高Python网络编程实战视频教程网络抓取爬虫08爬虫.mp4

- 自己开发的永磁同步电机FOC矢量控制模型和代码,目前已经在项目中使用,simulink界面结合源代码仿真 包含FOC算法,SVPWM,DPWM,死区补偿,过调制,母线电流估算等功能

- 基于c++的视觉框架,不仅提供了可视化操作界面源码,还提供了视觉算法源码,方便您二次开发 视觉算法主要有:标定工具,对位工具,几何工具等等 具体涉及的常用视觉算法有:模板匹配,卡尺工具,直线拟合,边缘

- 提高Python网络编程实战视频教程网络抓取爬虫09django初探-.wmv

- Maven 设置国内源,settings.xml

- abaqus焊接仿真培训资料,含热源模型,子程序 焊接应力应变场及其数值模拟理论简介 热力耦合理论(热应力分析) 协同软件的安装和修改、Abaqus软件使用基础 焊接模型的前处理部分Dflux子程序(

- hello kitty.exe

- 水平钻进钻机(step+exb+说明书)全套技术资料100%好用.zip

- 英飞凌芯片Traveo-II Overview产品线介绍,和芯片选型

- Comsol达西与pde结合描述地下水流作用下,孔隙率不断增大,孔隙率非均质,,可进行导水路径的查看,渗流速度场,压力场均可导出 SPKC

- 利用Matlab制作一个贼简单的粒子圣诞树.txt