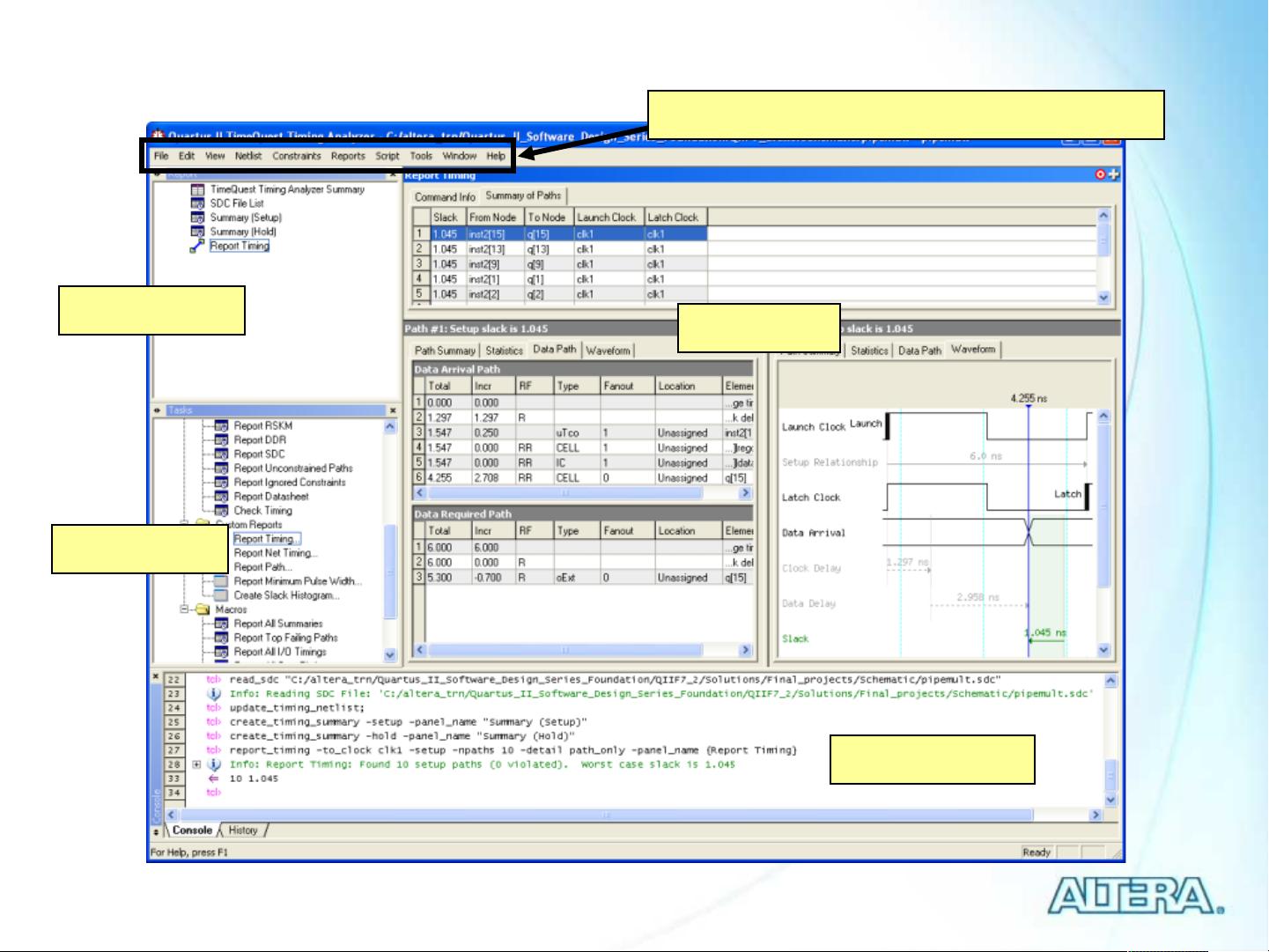

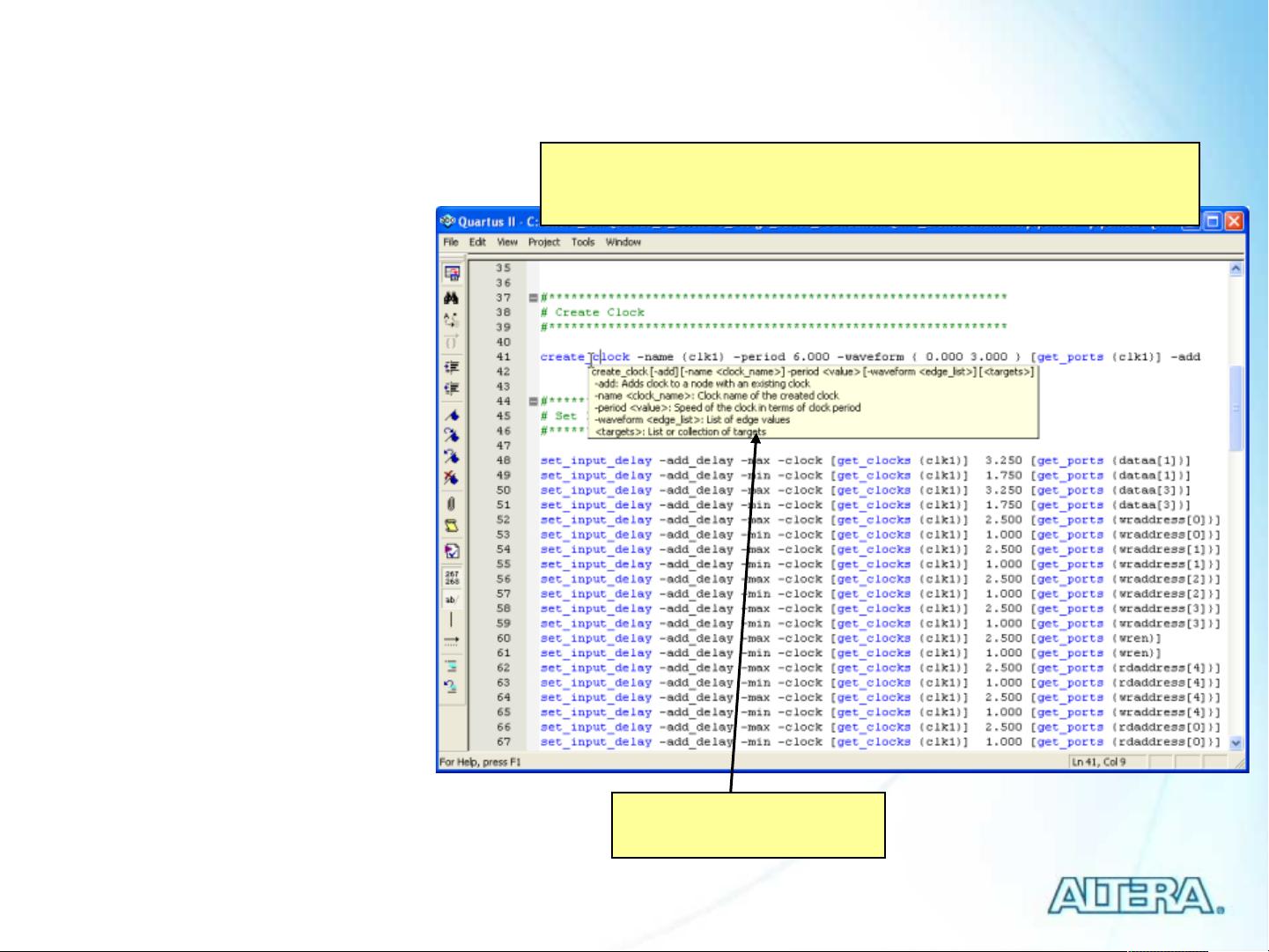

Quartus II Timequest时序分析器约束分析设计 本资源主要介绍了使用Quartus II Timequest时序分析器对设计进行约束分析的方法。 Quartus II是Altera Corporation的一款EDA(Electronic Design Automation)工具,用于开发和设计可编程逻辑器件(PLD)。Timequest是Quartus II中的时序分析器,用于分析和优化数字电路的时序性能。 本资源的主要内容包括: 一、时序分析基础 时序分析是指对数字电路的时序性能进行分析和优化的过程。时序分析的目的是确保数字电路的时序性能达到预期的要求。Timequest是Quartus II中的时序分析器,提供了强大的时序分析功能,能够对数字电路的时序性能进行详细的分析和优化。 二、时序约束 时序约束是指对数字电路的时序性能进行约束的规则。时序约束是时序分析的关键,通过时序约束,可以确保数字电路的时序性能达到预期的要求。SDC(Synopsys Design Constraints)文件是时序约束的文件格式,用于描述数字电路的时序约束。 三、TimeQuest基础 TimeQuest是Quartus II中的时序分析器,提供了强大的时序分析功能。TimeQuest的用户界面简洁易用,能够快速地对数字电路的时序性能进行分析和优化。TimeQuest的主要功能包括时序分析、时序优化、时序报告生成等。 四、时序约束文件编辑器 时序约束文件编辑器是用于创建和编辑SDC文件的工具。Quartus II提供了一个内置的时序约束文件编辑器,用户可以使用该编辑器来创建和编辑SDC文件。时序约束文件编辑器提供了语法高亮、tooltip提示等功能,方便用户快速地创建和编辑SDC文件。 五、TimeQuest文件菜单 TimeQuest文件菜单提供了对TimeQuest的所有功能的访问。用户可以通过TimeQuest文件菜单来创建和打开SDC文件、生成时序报告、保存时序约束等。 六、基本步骤 使用TimeQuest进行时序分析需要遵循以下基本步骤: 1. 生成时序网表 2. 输入时序约束 3. 更新时序网表 4. 生成时序报告 5. 保存时序约束(可选) 本资源为读者提供了使用Quartus II Timequest时序分析器对设计进行约束分析的详细指导,涵盖了时序分析基础、时序约束、TimeQuest基础、时序约束文件编辑器、TimeQuest文件菜单和基本步骤等内容。

剩余121页未读,继续阅读

- 粉丝: 1

- 资源: 7

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【全年行事历】5团建医药箱常备药清单.docx

- 【全年行事历】4团建活动物料清单.xlsx

- 【全年行事历】7团建活动策划书.docx

- 【全年行事历】ZOL团建活动策划方案.pptx

- 【全年行事历】XXX团建活动计划.pptx

- 【全年行事历】86团建活动培训PPT完.pptx

- 【全年行事历】公司年度活动计划.xls

- 【全年行事历】大型企业公司活动进度表.xlsx

- 【全年行事历】公司户外团建活动方案-某公司.pptx

- 【全年行事历】公司团建费用统计表.xlsx

- 【全年行事历】公司团建拓展行程方案-模版.docx

- 【全年行事历】公司全年团建活动方案.xls

- 【全年行事历】公司员工一年度关怀方案预算.xls

- 【全年行事历】公司团建活动项目介绍.pptx

- 【全年行事历】行政部年度活动策划及经费预算.xlsx

- 【全年行事历】行政全年活动筹备规划.xlsx

信息提交成功

信息提交成功