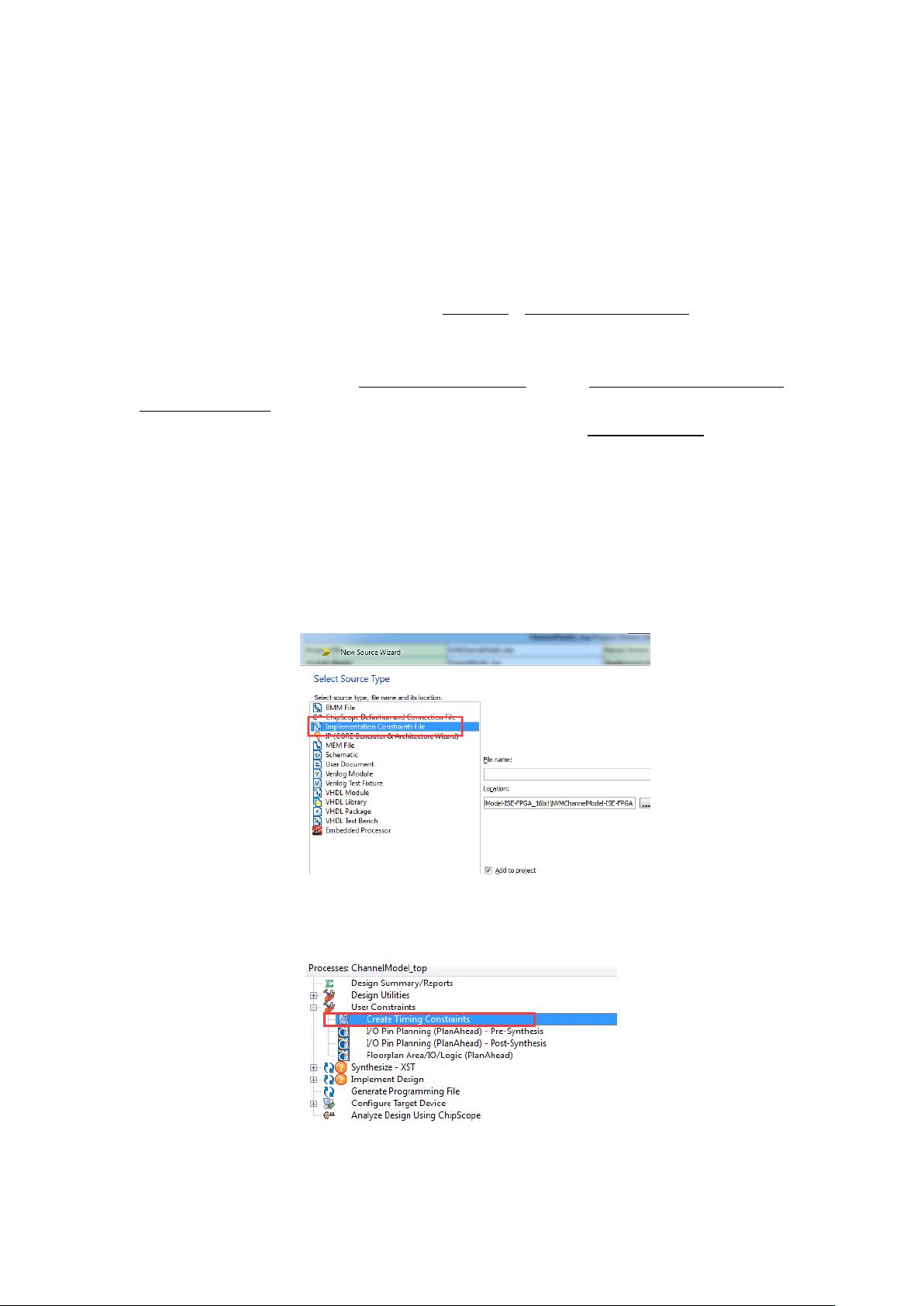

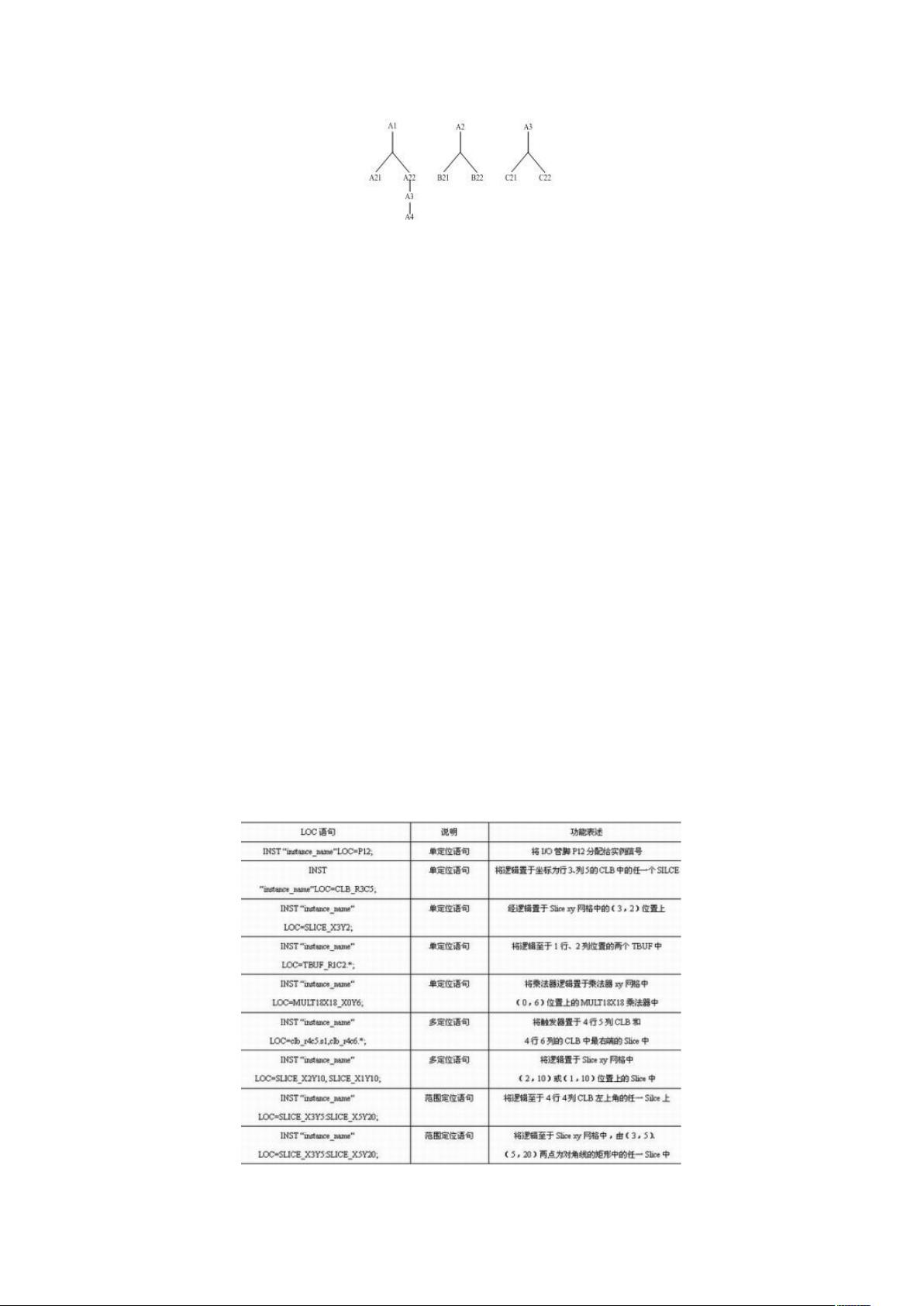

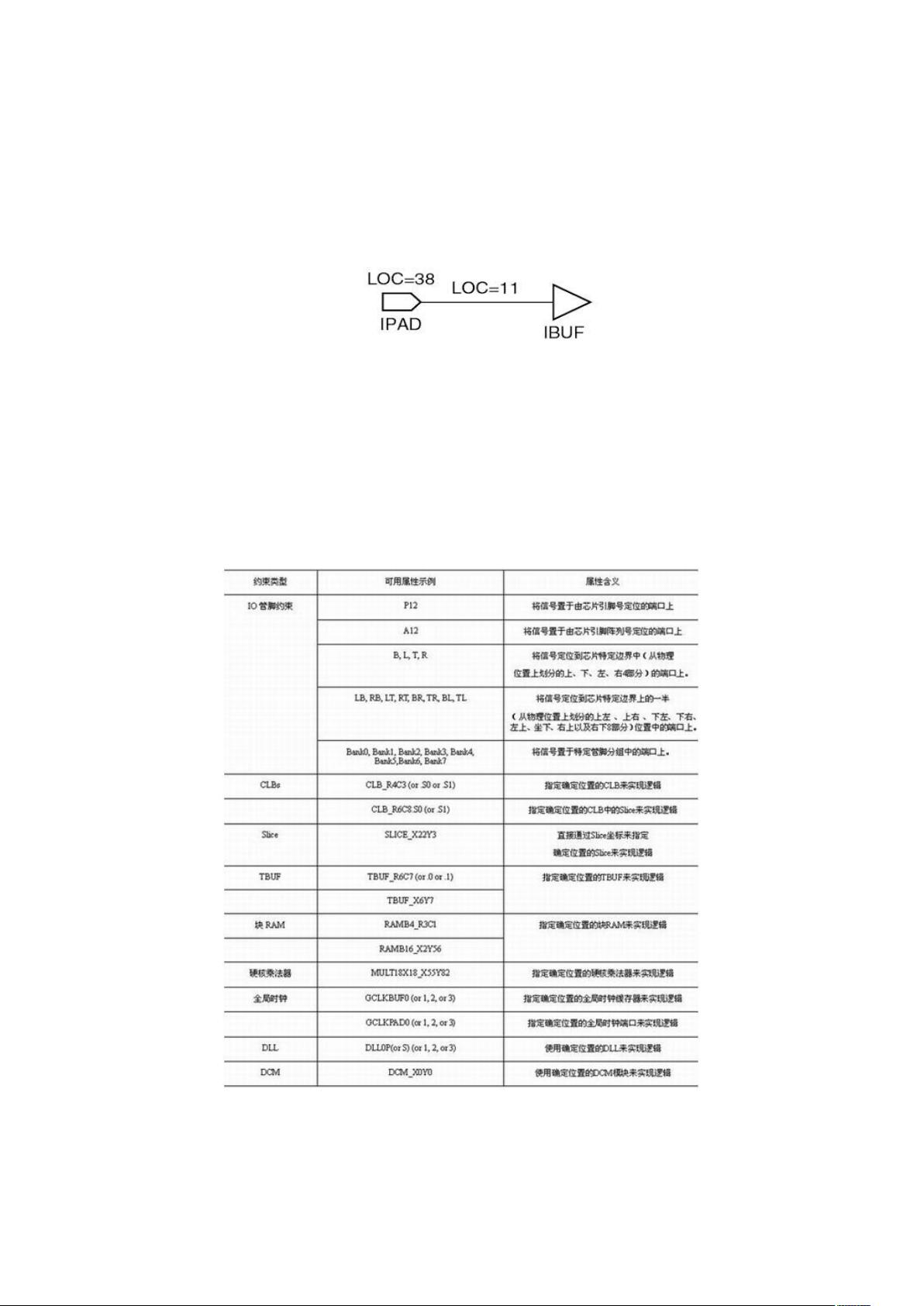

在FPGA开发中,时序约束是至关重要的一个环节,它直接影响着设计的性能和时钟速度。Xilinx FPGA设计的时序约束涉及到三种类型的约束文件:用户设计文件(.UCF)、网表约束文件(.NCF)和物理约束文件(.PCF)。这三者分别用于不同阶段的约束设定。 用户设计文件(.UCF)是在设计输入阶段由用户编写的,用于定义逻辑设计的约束,如时钟路径、I/O口等。UCF文件采用ASCII格式,可以通过文本编辑器或Xilinx提供的约束文件编辑器进行编辑。其中,信号名需与源代码中的名称完全匹配,并且是大小写敏感的,而约束关键字则不强制大小写要求。 网表约束文件(.NCF)是由综合工具自动生成的,它包含了综合后的设计信息。NCF文件的语法与UCF文件相同,但在两者冲突时,UCF文件的优先级更高,因为它是用户直接指定的约束。 物理约束文件(.PCF)则是在实现阶段生成的,用于指定元件在FPGA物理布局上的位置。PCF文件可以分为两部分:一部分是自动映射的物理约束,另一部分是用户输入的约束。用户约束同样具有最高优先级,尽管如此,不推荐直接修改NCF和PCF文件,而应通过UCF文件进行修改。 创建约束文件主要有两种方式:一是新建源文件,选择“Implementation Constrains File”,并指定约束文件名;二是通过过程管理器,将“Source for”设置为“Synthesis/Implementation”,然后在“User Constrains”下创建时序约束。 UCF文件的语法包括对象(NET、INST、PIN)、信号名、约束描述以及注释。通配符“*”和“?”可用于选取一组具有共同字符串的信号,方便批量约束。例如,"NET "*CLK?" FAST;"会将所有以"CLK"开头的信号设为高速信号。使用"*"还可以指定设计层次,例如,Level1/*将遍历level1及其下层的所有模块。 LOC约束是FPGA设计中的关键,用于指定设计单元在芯片上的位置。例如,INST "instance_name" LOC = location; 其中,location是具体的位置信息,可以是绝对位置、范围或区域。LOC约束不仅用于布局,还对综合和优化有直接影响。 在进行FPGA设计时,正确和充分的时序约束是确保设计满足时序要求的关键步骤。理解并熟练运用UCF、NCF和PCF文件,以及LOC约束等概念,能够帮助开发者优化设计,提高系统性能。因此,掌握这些知识点对于FPGA开发人员来说至关重要。

剩余48页未读,继续阅读

- 粉丝: 21

- 资源: 288

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 《济南的冬天》教学设计与反思.docx

- 基于java+springboot+vue+mysql的古典舞在线交流平台 源码+数据库+论文(高分毕业设计).zip

- 形状检测32-YOLO(v5至v9)、COCO、CreateML、Darknet、Paligemma数据集合集.rar

- 百度智能云千帆大模型平台推进企业多模态生成式AI应用

- 互联网金融发展指数 (第二期,2014年1月-2015年12月).zip

- 社区团购网站:技术驱动下的电子商务新模式

- 2025年人形机器人产业发展蓝皮书-量产及商业化关键挑战

- C# 面试题 100 问:从基础到进阶,全面解析与实战.docx

- 基于java+springboot+vue+mysql的读书笔记共享平台 源码+数据库+论文(高分毕业设计).zip

- Python+Django+Mysql个性化图书推荐系统 图书在线推荐系统 基于用户、项目、内容的协同过滤推荐算法 帮远程安装部署 一、项目简介 1、开发工具和实现技术 Python3.8,Djan

- 基于Java的环境保护与宣传网站的设计与实现毕业论文.doc

- 基于java+springboot+vue+mysql的海滨体育馆管理系统 源码+数据库+论文(高分毕业设计).zip

- 2025年 UiPath AI和自动化趋势:代理型AI的崛起及企业影响

- 基于java+springboot+vue+mysql的网上超市系统 源码+数据库+论文(高分毕业设计).zip

- 电力系统静态稳定性仿真simulink仿真 用simulink搭建搭建单机无穷大系统,对其静态稳定性进行仿真分析

- 柑橘多种疾病类型图像分类数据集【已标注,约1,000张数据】

信息提交成功

信息提交成功

评论0