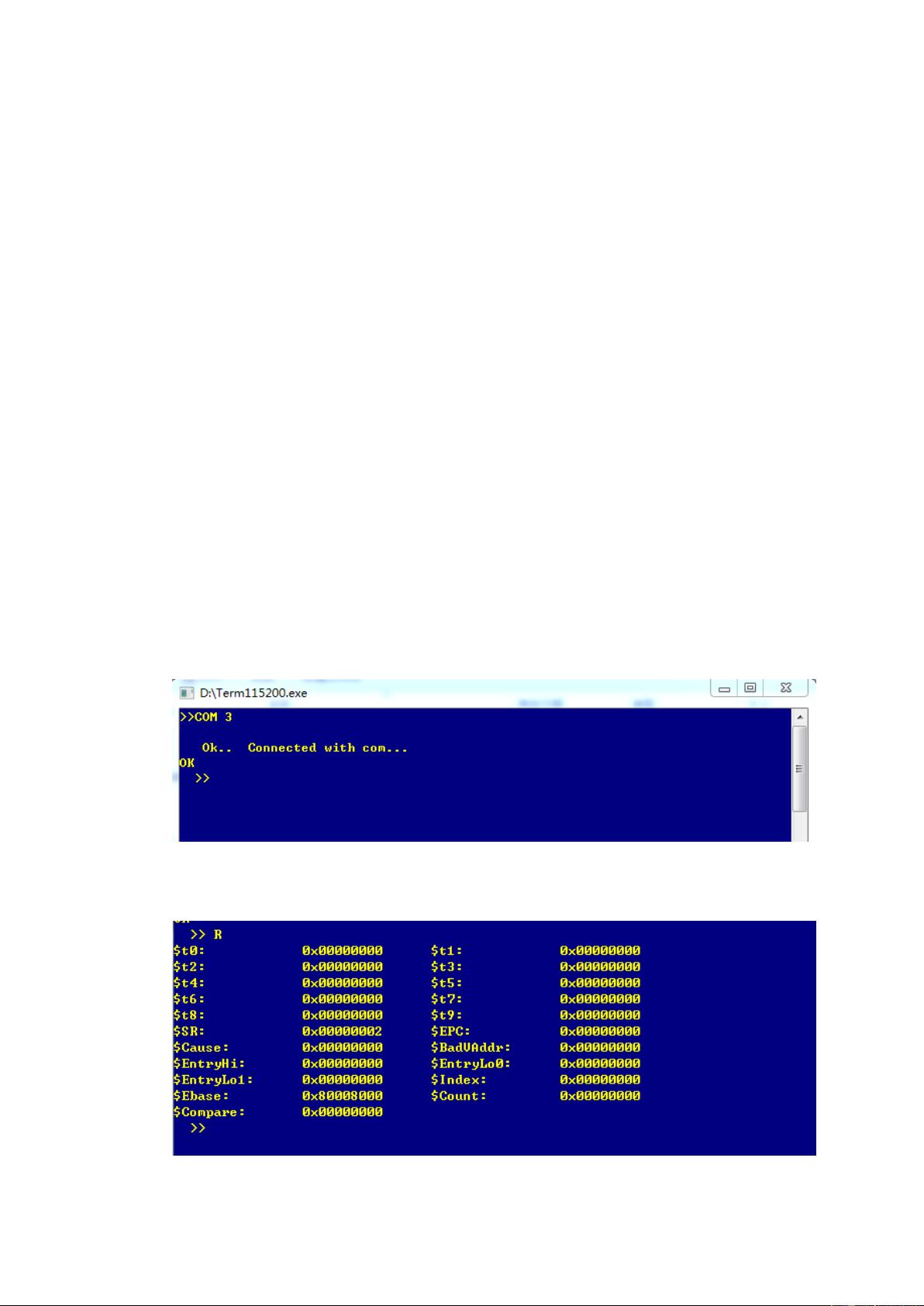

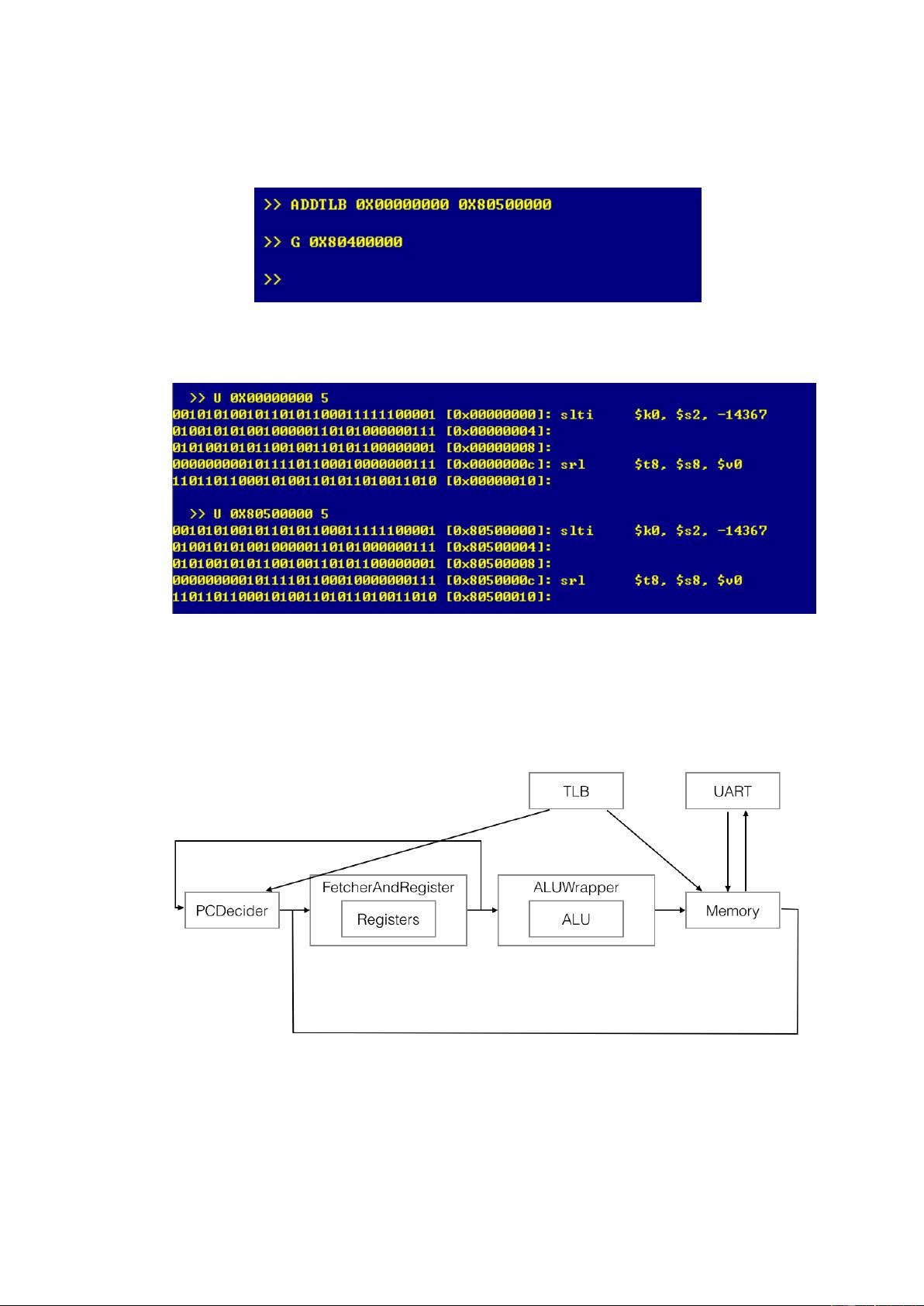

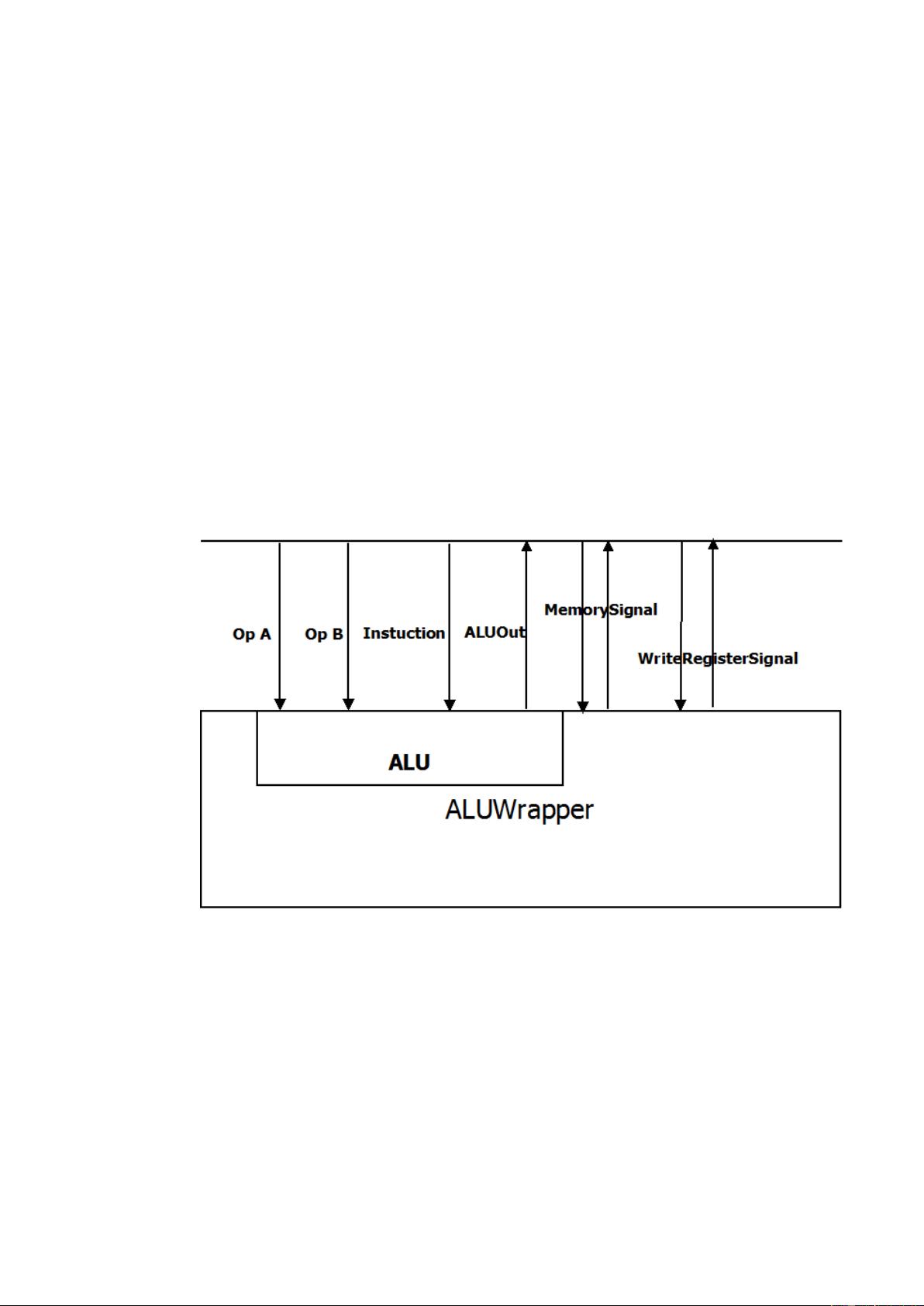

《MIPS32流水CPU设计实验报告》详细解析 MIPS32流水线CPU的设计是一项复杂的计算机体系结构任务,旨在实现一种高效的处理器架构,能够执行MIPS32指令集,并具备中断和异常处理能力。本实验报告将详细介绍设计的目标、运行效果、总体设计以及各模块的分析。 1. **设计目标** - 目标之一是构建一个支持MIPS32指令集的五段流水线结构CPU。 - CPU需能处理中断和异常,包括TLB(Translation Lookaside Buffer)缺失和系统调用。 - 开发与32位THINPAD教学计算机相关的测试工具,如串口测试和SRAM测试。 - 针对32位CPU的新特性,对原有监控程序进行小规模修改,并用Python重写终端程序,使其能在多个平台上运行。 2. **运行效果** - CPU启动后,通过Term.exe与实验平台通信,R指令查看通用寄存器的值,D指令检查预设内存位置的值。 - 使用LOAD指令加载用户编写的二进制程序,G指令运行该程序,实现冒泡排序功能。 - A指令用于向内存写入汇编代码,触发TLB缺失异常,然后使用ADDTLB命令建立虚拟地址和物理地址的映射,确保程序正常运行。 - U指令验证TLB添加成功后的内存一致性。 3. **总体设计** - **ALUWrapper** 包含ALU运算单元,连接FetcherAndRegister和Memory模块,负责算术和逻辑运算,处理异常信号,进行地址转换。 - **Register(FetcherAndRegister)** 与PCDecider、ALUWrapper连接,包含通用寄存器和CP0寄存器组,负责指令解码、读取寄存器值、响应内存操作信号和异常处理。 - **Memory** 与ALUWrapper和FetcherAndRegister连接,管理SRAM、ROM和UART读写,执行内存操作和特定地址的UART交互。 - **PCDecider** 接收信号判断跳转、等待或顺序执行,向RAM发送地址信号,输出当前PC值。 - **TLB** 提供虚拟地址到物理地址的映射表,处理TLB缺失异常,中断流水线并跳转到中断处理程序。 4. **模块分析** - **ALU** 的结构和功能包括执行算术和逻辑运算,传递信号,以及处理TLB未找到的情况。 - **Register** 的核心是寄存器组,通过signal实现快速存取,简化实验过程。 - **Memory** 控制内存访问,处理UART通信,并向FetcherAndRegister返回写寄存器信号。 - **PCDecider** 根据输入信号决定PC的更新方式,如顺序执行、跳转或等待。 - **TLB** 通过表项映射虚拟地址,处理异常,确保正确执行内存访问。 通过以上分析,可以看出MIPS32流水线CPU设计的复杂性和各组件间的协同工作。每个模块都有其特定的职责,共同保证了CPU的正常运行和高效性能。实验报告不仅展示了CPU设计的基本原理,还演示了如何通过测试工具验证其功能,从而加深了对计算机体系结构的理解。

剩余22页未读,继续阅读

- 粉丝: 42

- 资源: 319

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于springboot+vue的在线拍卖系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的学生网上请假系统设计与实现(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的新冠病毒密接者跟踪系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的新闻稿件管理系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的学生选课系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的疫苗发布和接种预约系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的在线商城系统设计与开发-代码(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的疫情打卡健康评测系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的智能物流管理系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的知识管理系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的在线文档管理系统的设计与实现(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的中小型医院网站(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的“衣依”服装销售平台的设计与实现(Java毕业设计,附源码,部署教程).zip

- 基于springboot的房屋租赁系统(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的车辆管理系统设计与实现(Java毕业设计,附源码,部署教程).zip

- 基于springboot+vue的it技术交流和分享平台的设计与实现(Java毕业设计,附源码,部署教程).zip

信息提交成功

信息提交成功

评论0