实验4 - 数据通路和有限状态机设计1

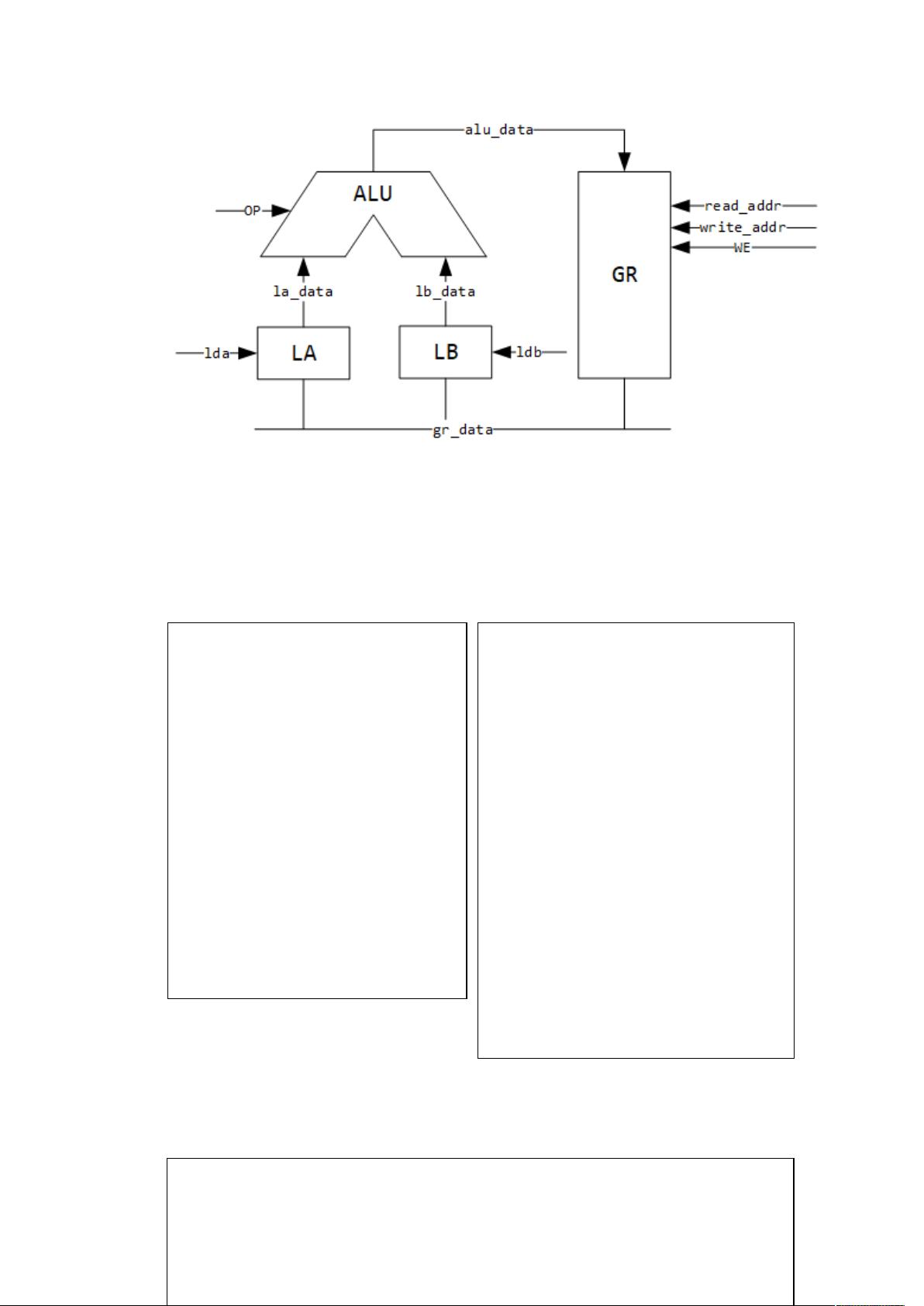

实验4 - 数据通路和有限状态机设计1的焦点在于理解和设计处理器中的核心组件,包括数据通路和控制器。在这个实验中,你需要构建一个n位的存储器模块,该模块用于存储特定的链表结构。链表的首个节点位于0号地址,每个节点的第一个地址存储了下一个节点的地址,而第二个地址则包含了需要处理的数据。 数据通路是处理器的硬件部分,它执行实际的算术和逻辑运算以及数据传输。在图2所示的样例中,数据通路由计算单元ALU、两个寄存器LA和LB以及一个双端口存储器GR组成。这些单元通过各种控制信号(如OP、lda、ldb、read_addr、write_addr、WE等)协同工作,同时内部数据通过la_data、lb_data、gr_data和alu_data流动。 在设计过程中,你需要为每个逻辑单元创建独立的Verilog模块。例如,ALU模块接受两个输入a和b,以及操作码op,输出结果q。它根据op的值执行加法、按位与、按位异或和按位或操作。寄存器模块则包含时钟信号clk、复位信号rst_n、使能信号en、数据输入d和数据输出q,它在时钟上升沿并在使能信号为高时更新其内容。RAM模块使用读写地址、数据、时钟和写使能信号来读取或写入存储器内容。 在实现数据通路时,你需要使用结构化描述方法,即组合上述模块来构造整个数据通路。输入信号包括读写地址、写使能、操作码等,输出则对应于这些操作的结果。 控制器,通常以有限状态机(FSM)的形式存在,负责控制数据通路中数据的流动顺序。它接收控制流的输入,产生控制信号输出,以协调数据通路中的操作。在这个实验的第二步,你需要设计这样一个有限状态机,确保它可以正确地指导数据通路执行所需的指令序列。 实验的第三步是整合前两步的设计,构建一个能够自动执行运算的处理器。这要求你将数据通路和控制器结合起来,形成一个可以读取指令、解码指令并执行计算的完整系统。 在整个实验过程中,可能会遇到的问题可能包括同步和异步信号的处理、状态机的死锁或自锁、数据通路中的竞争条件以及存储器的初始化和访问。这些问题通常通过仔细分析时序逻辑、优化控制逻辑和验证设计来解决。完成实验后,应反思自己的学习过程,提出改进建议,以便于后续的学习和提高。 这个实验旨在通过实践提升你对处理器内部工作原理的理解,以及如何用硬件描述语言(如Verilog)设计和实现这些原理。通过这个实验,你将更深入地了解数据通路、有限状态机和处理器设计的核心概念。

剩余26页未读,继续阅读

- 粉丝: 31

- 资源: 311

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 通过C#实现冒泡排序示例代码(含代码解释)

- 保险交叉销售预测数据集.zip

- StartAllBack-3.6.3-setup, win不同风格的开始菜单

- c语言实现希尔排序基础

- emoji表情使用趋势数据集.zip

- 抖音 douyin 视频评论 spider

- Beyond.Compare.v3.1.10

- 2016年年度培训计划及跟踪表.xls

- 2016年公司员工年度培训计划表.xls

- 《如何设计年度培训计划与预算方案》.ppt

- 公司培训规划之一--员工素养培训(PPT 63页).ppt

- 麦肯锡:进度安排培训.ppt

- 北大讲义《如何设计年度培训计划与预算方案》.ppt

- 美的校园招聘面试官培训方案(ppt 14页).ppt

- 培训与发展.ppt

- 培训管理.ppt

信息提交成功

信息提交成功

评论0