没有合适的资源?快使用搜索试试~ 我知道了~

实验4+-+数据通路和有限状态机设计1

需积分: 0 1 下载量 136 浏览量

2022-08-08

18:39:49

上传

评论

收藏 1010KB DOCX 举报

温馨提示

试读

27页

实验4 数据通路和有限状态机设计任务描述相关知识实验内容遇到问题和解决方法实验心得、意见和建议任务描述综合应用掌握的简单组合电路(实验2)和简单时序电路(实验3

资源详情

资源评论

资源推荐

实验 4 数据通路和有限状态机设计

任务描述

相关知识

实验内容

遇到问题和解决方法

实验心得、意见和建议

任务描述

综合应用掌握的简单组合电路(实验 2)和简单时序电路(实验 3)的设计方法,完成

一个数据通路的设计,并为该数据通路配上一个控制器(有限状态机),最后将所有的实验

综合起来,实现一个简单的处理器(自动运算电路)。

相关知识

在学习完实验 3(简单时序电路设计)后,实验 4 将尝试较为复杂的时序电路设计(比

如处理器)。此类电路设计主要包含“数据通路”(Datapath)和“控制器”(Controller)两

大部分,在经典计算机模型中,处理器部分如图 1 红框所示。其中,数据通路负责数据的操

作,包括算术运算和传输数据;控制器负责数据的控制,通常以有限状态机(FSM:Finite State

Machine)方式实现,包括控制流的输入、输出,以及控制数据通路中数据的传输顺序。另

外,处理器旁通常会有一个“存储器”(Memory),可根据地址存取程序指令和数据。注意,

数据通路自身并不能工作,只能通过控制器输出控制信号,输入到数据通路的各个单元,才

能完成处理器的工作。因此,一个经典处理器通常是由数据通路和控制器组合完成的;与之

对应的,本实验共包含三个步骤:数据通路(步骤 1),有限状态机(步骤 2),和自动运算

处理器(步骤 3)。

图 1 处理器由数据通路和控制器构成

实验内容

1. 数据通路设计(步骤 1)

【实验样例】

图 2 所示处理器中,有 4 个逻辑单元,包括一个计算单元 ALU,两个寄存器单

元 LA 和 LB,以及一个双端口存储器 GR。各个单元的外部控制信号包括 OP,

lda, ldb, read_addr, write_addr, WE 等,数据通路内部传输数据包括 la_data, lb_data,

gr_data 和 alu_data。

图 2 某处理器的数据通路

首先实现各个单元的模块:

module alu(a, b, op, q);

parameter WIDTH = 8;

input [WIDTH-1:0] a, b;

input [1:0] op;

output reg [WIDTH-1:0] q;

always @(*) begin

case(op)

2'b00: q = a + b;

2'b01: q = a & b;

2'b10: q = a ^ b;

2'b11: q = a | b;

default: q = 0;

endcase

end

endmodule

module register(clk, rst_n, en, d, q);

parameter WIDTH = 8;

input clk, rst_n, en;

input [WIDTH-1:0] d;

output reg [WIDTH-1:0] q;

always @(posedge clk) begin

if (!rst_n) q <=0;

else if (en) q <= d;

end

endmodule

module ram(data, read_addr, write_addr, clk, we, q);

parameter DATA_WIDTH = 8;

parameter ADDR_WIDTH = 3;

input clk, we;

input [DATA_WIDTH-1:0] data;

input [ADDR_WIDTH-1:0] read_addr, write_addr;

output reg [DATA_WIDTH-1:0] q;

// 申明存储器数组

reg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];

initial begin //对存储器初始化

$readmemh("ram_init.txt", ram); end

always @(posedge clk) begin

if (we)

ram[write_addr] <= data;

q <= ram[read_addr];

end

endmodule

其次利用结构描述设计方法,利用以上模块实现图 2 的数据通路:

注:register #(32) LA (clk, rst, lda, gr_data, la_data)传递参数 32 到 LA 模块,使得

其 WIDTH = 32。

【实验要求】

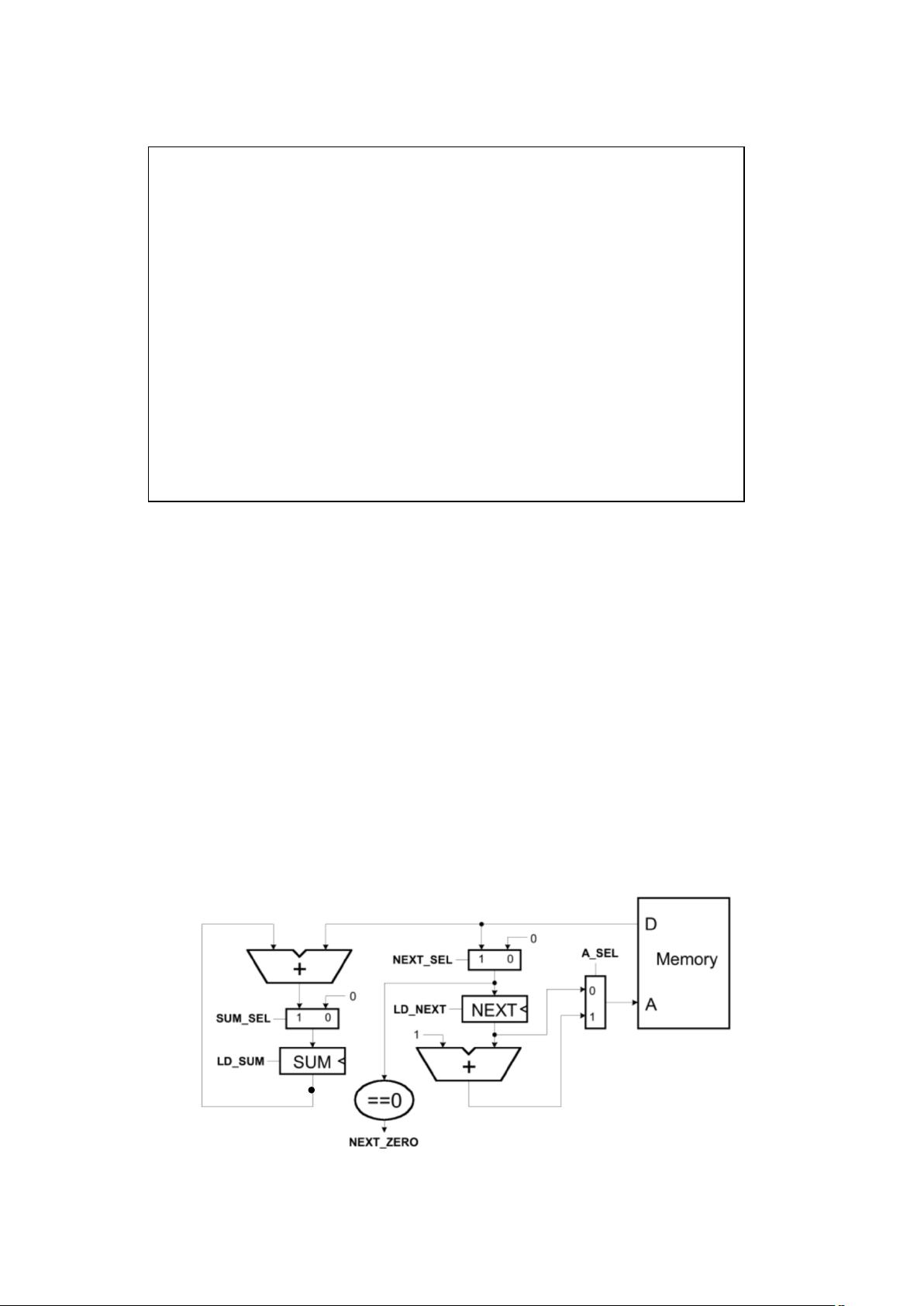

请参照实验样例,实现图 3 所示的数据通路。图 3 给出的数据通路里,SUM 和

NEXT 是寄存器,Memory 是存储器,+是加法器,==0 是比较器,其它则是多路

选择器。具体要求如下:

图中数据线的宽度和各个器件的数据线宽度初始设计时均为 8 位,要求

构成数据通路时可以扩充至 16 位或者是 32 位;

设计的数据通路能够正确综合,Vivado 所示的电路原理图与图 3 给出的

一致。

图 3 数据通路图

module datapath_top(clk, rst, lda, ldb, read_addr, write_addr, we, op);

input clk, rst, lda, ldb, we;

input [4:0] read_addr, write_addr;

input [1:0] op;

wire [31:0] gr_data, alu_data;

wire [31:0] la_data, lb_data;

register #(32) LA (clk, rst, lda, gr_data, la_data);

register #(32) LB (clk, rst, ldb, gr_data, lb_data);

ram #(32, 5) GR (alu_data, read_addr, write_addr, clk, we, gr_data);

alu #(32) ALU (la_data, lb_data, op, alu_data);

endmodule

sum_out

【实验提示】

(1)分别设计 n 位加法器模块,n 位 2 选 1 多路选择器模块,n 位比较器

模块。(用 parameter 传参来扩展)

(2)设计一个含同步复位 rst 和加载 load 端的 n 位寄存器模块

当 load=1 时,对输入的 n 位数据进行同步寄存,即让输入 D 的值赋给输出

Q。

(3)设计一个 n 位存储器模块,存储器中存放如下的链表(具体见图 7),

链表第 1 个节点在 0 号地址,各节点的第一个地址存放下一个节点的地址,各

节点的第二个地址中存放着要进行求和运算的数据,当下一个节点的地址为 0

时,表示到达链表的结尾,求和运算结束。

00000003

00000002

00000000

00000007

00000004

00000000

00000000

0000000b

00000006

00000000

00000000

00000000

00000008

00000000

00000000

00000000

注:存储器存放该链表的过程可以如下实现:1) 将该链表存入一个文本文件;

2) 用系统函数$readmemh 读该文本文件对存储器进行初始化。具体可见教材

readmemh 的语法。

剩余26页未读,继续阅读

网络小精灵

- 粉丝: 25

- 资源: 335

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0