没有合适的资源?快使用搜索试试~ 我知道了~

518030910374_曾锴鹏_实验31

需积分: 0 2 下载量 87 浏览量

2022-08-04

15:41:14

上传

评论

收藏 1.15MB PDF 举报

温馨提示

试读

18页

1. 理解计算机指令流水线的协调工作原理,初步掌握流水线的设计和实现原理 2. 深刻理解流水线寄存器在流水线实现中所起的重要作用 3. 理解和掌握流水段的划分、

资源详情

资源评论

资源推荐

五段流水线CPU设计

实验目的

1. 理解计算机指令流水线的协调工作原理,初步掌握流水线的设计和实现原理。

2. 深刻理解流水线寄存器在流水线实现中所起的重要作用。

3. 理解和掌握流水段的划分、设计原理及其实现方法原理。

4. 掌握运算器、寄存器堆、存储器、控制器在流水工作方式下,有别于实验一的设计和实现方法。

5. 掌握流水方式下,通过 I/O 端口与外部设备进行信息交互的方法。

实验特殊说明

1. 本次实验的 和 跳转在 阶段完成,因此移除了顶层设计中的 信号。

2. 本次实验没有采用转移延迟槽的设计而实采用 信号解决 等跳转信号产生的控制冒险,

因此本次实验采用的 中跳转语句的后方无需插入 语句进行停顿。

3. 本次实验 信号位高电平有效。

实验思路和代码实现

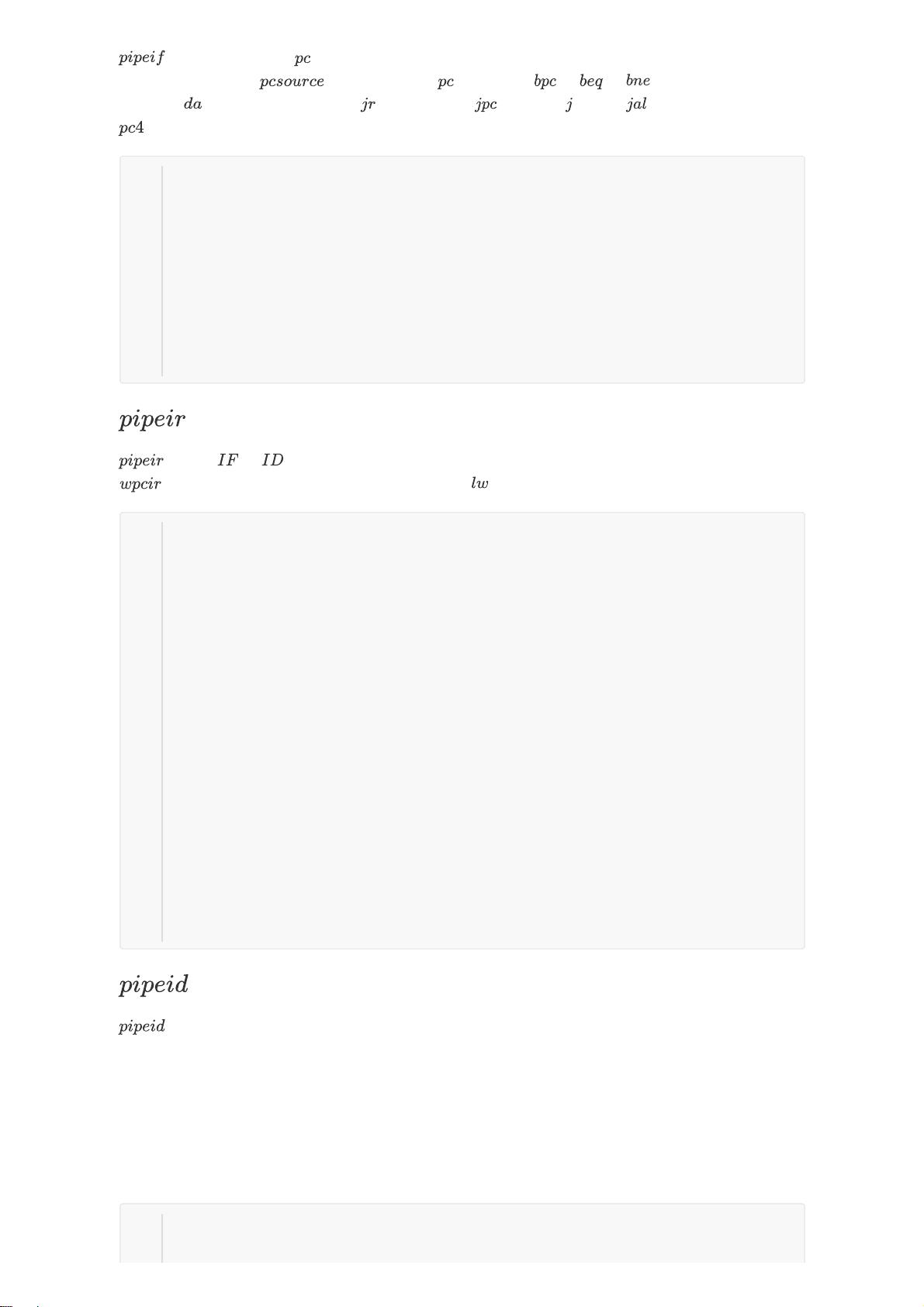

实现

的作用是获取下一条即将执行的指令的 值。该模块由时钟驱动,在时钟的上升沿处更新

值。在 信号出现时,将 值设为无效的 -4,同时方便在一个周期后进入重新从 处读取

指令开始执行。同时 信号决定是否对 的值进行更新,以解决由 指令造成的数据冒险。

实现

module pipepc(newpc, wpcir, clock, resetn, pc);

input [31:0] newpc;

input resetn, wpcir, clock;

output reg [31:0] pc;

always @(posedge clock or negedge resetn)

begin

if(resetn == 0)

begin

pc <= -4;

end

else

if(wpcir != 0)

begin

pc <= newpc;

end

end

endmodule

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

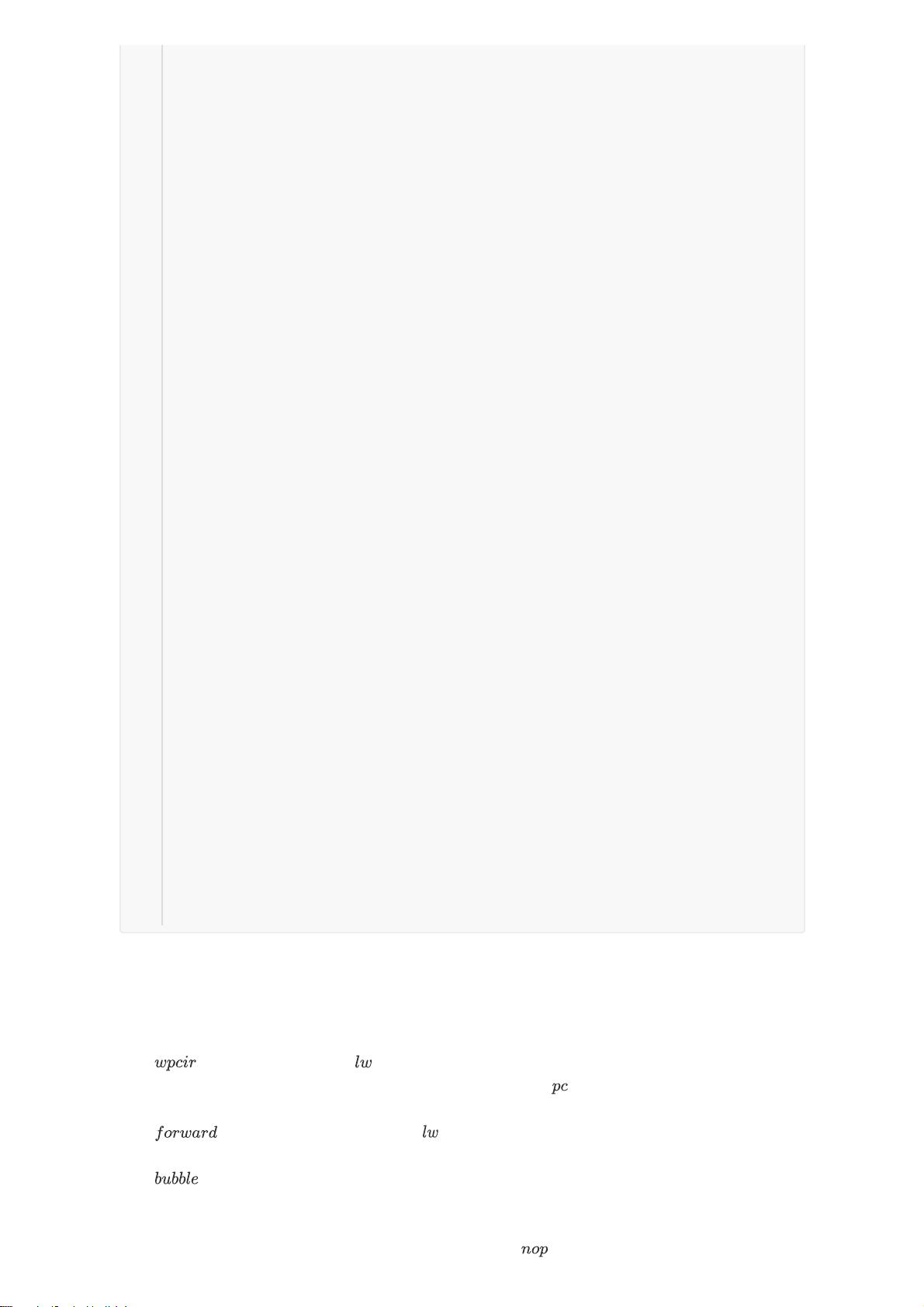

阶段实现的是根据 值从指令ROM中取出指令。同时该阶段还将定义一个32位四选一多选器,

根据控制单元给出的 决定下一条指令 值的来源。 是 合 指令跳转的下一条指

令地址; 来自寄存器,用来解决 指令的跳转, 用来解决 指令和 指令带来的跳转, 而

则是无跳转时按照顺序执行的下一条语句。

实现

是连接 和 阶段的数据寄存器,合其他寄存器不同,除去清零信号之外,该寄存器还受

信号的控制,用来在流水线中加入气泡以解决 造成的数据冒险。

实现

阶段几乎是整个五段流水线中最复杂也最核心的部分,一方面它要完成对寄存器堆的读写操作,

另一方面该阶段还要实现控制单元对整个CPU工作信号的生成,包括但不限于后续执行阶段的信号,内

存读写信号以及设定旁路直通信号和气泡解决数据冒险和跳转造成的控制冒险。

顶层设计

顶层代码结构和单周期CPU设计并无很大差别,尤其是寄存器堆部分并无发生任和改变,因此不做过多

赘述。该阶段重点在于控制单元的设计。

module pipeif(pcsource,pc,bpc,da,jpc,npc,pc4,ins,mem_clock);

input mem_clock;

input [ 1:0] pcsource;

input [31:0] pc, bpc, da, jpc;

output wire [31:0] npc, pc4, ins;

assign pc4 = pc + 4;

mux4x32 nextpc(pc4, bpc, da, jpc, pcsource, npc);

sc_instmem imem(pc, ins, mem_clock);

endmodule

1

2

3

4

5

6

7

8

9

10

module pipeir(pc4,ins,wpcir,clock,resetn, dpc4,inst);

input [31:0] pc4, ins;

input wpcir, clock, resetn;

output reg [31:0] dpc4, inst;

always @(posedge clock or negedge resetn)

begin

if(resetn == 0)

begin

inst <= 0;

dpc4 <= 0;

end

else

if(wpcir != 0)

begin

inst <= ins;

dpc4 <= pc4;

end

end

endmodule

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

module pipeid(

mwreg,mrn,ern,ewreg,em2reg,mm2reg,dpc4,inst,

1

2

控制单元设计

和单周期CPU相同的是,控制单元仍然承担着解码并且进一步生成控制信号的作用。与单周期不同的是

控制单元在流水线设计中要多出三个信号:

1. 信号,该信号用来解决 造成的数据冒险,当这种情况发生时,CPU应当停止流水线上这

条指令的操作(控制信号置零),插入一个气泡,同时阻止 和 的更新迭代,直到下一个周期这

条指令可以获得正确的操作数据。

2. 信号,这些信号用来处理除了 之外其他造成的数据冒险,旁路直通的设计和原理在

理论课程上已经完备叙述过,此处不进行过多赘述。

3. 信号,这条信号解决由跳转产生的控制冒险问题。本次CPU设计未采用延迟槽设计,因此

我们需要避免紧跟在跳转指令之后那条指令的执行,即当跳转发生时,我们应该对流水线进行冲

刷,将跳转指令的下一条指令所有控制信号置零。或者我们可以认为当bubble信号有效时,进入

译码阶段的这条指令不应被执行,因此我们把它替换为 指令来防止流水线的运行错误。

wrn,wdi,ealu,malu,mmo,wwreg, clock,resetn,

bpc,jpc,pcsource,wpcir,dwreg,dm2reg,dwmem,daluc,

daluimm,da,db,dimm,drn,dshift,djal,dbubble, ebubble, dsa

);

input [ 4:0] mrn, ern, wrn;

input ewreg, mwreg, wwreg, mm2reg, em2reg, clock, resetn,

ebubble;

input [31:0] inst, wdi, ealu, malu, mmo, dpc4;

output [31:0] jpc, bpc, da, db, dimm, dsa;

output [ 1:0] pcsource;

output wpcir, dwreg, dm2reg, dbubble, dwmem, daluimm, dshift,

djal;

output [ 3:0] daluc;

output [ 4:0] drn;

wire [31:0] q1, q2, da, db;

wire [ 1:0] forwarda, forwardb;

wire z = (da == db);

wire regrt, sext;

wire e = sext & inst[15];

wire [15:0] imm = {16{e}}; // high 16 sign bit

wire [31:0] dimm = {imm,inst[15:0]};

wire [31:0] dsa = { 27'b0, inst[10:6] }; // extend to 32 bits from sa

for shift instruction

wire [31:0] offset = {imm[13:0],inst[15:0],1'b0,1'b0};

wire [31:0] bpc = dpc4 + offset;

wire [31:0] jpc = {dpc4[31:28],inst[25:0],1'b0,1'b0};

wire dbubble = (pcsource[1:0] != 2'b00);

regfile rf( inst[25:21], inst[20:16], wdi, wrn, wwreg, clock, resetn,

q1, q2 );

mux4x32 muxda(q1, ealu, malu, mmo, forwarda, da);

mux4x32 muxdb(q2, ealu, malu, mmo, forwardb, db);

mux2x5 muxrn(inst[15:11], inst[20:16], regrt, drn);

sc_cu cu_inst(inst[31:26], inst[5:0], z, dwmem, dwreg, regrt, dm2reg,

daluc, dshift,

daluimm, pcsource, djal, sext, forwarda, forwardb, wpcir,

inst[25:21], inst[20:16], mrn, mm2reg, mwreg, ern, em2reg,

ewreg, ebubble);

endmodule

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

剩余17页未读,继续阅读

woo静

- 粉丝: 23

- 资源: 347

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0