LS-CPU-EXB-003cpu设计与体系结构实验指导手册v1.0(教师版)_20170315-old1

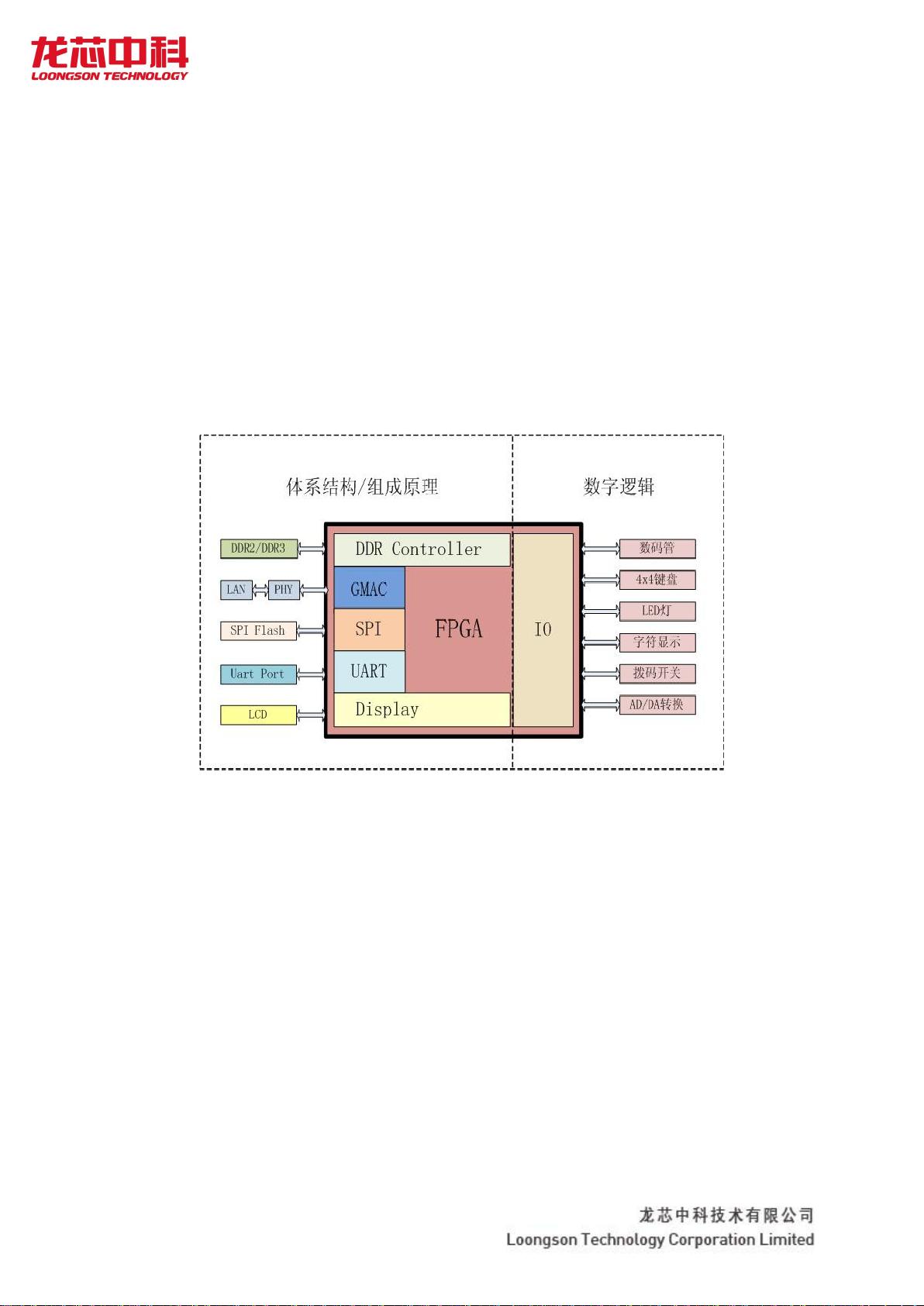

LS-CPU-EXB-003 CPU设计与体系结构实验指导手册主要针对教育领域,旨在帮助学生和教师深入理解CPU的基本构造和工作原理。该手册基于LS-CPU-EXB-002实验箱,这是一个专为学习CPU设计与体系结构而设计的教学工具。下面我们将详细探讨手册中的关键知识点。 LS-CPU-EXB-002实验箱提供了硬件和软件平台,让学生能够亲手操作,实践CPU设计。硬件部分包含了各种基本的数字逻辑部件,如门电路、触发器、加法器等;软件平台则可能包括逻辑仿真工具,用于设计、测试和调试CPU的逻辑电路。通过熟悉这个实验箱,学生可以直观地了解CPU组件,并学习如何将这些组件连接起来形成一个完整的计算系统。 实验一介绍了定点加法,这是CPU中最基础的数据运算。加法器的设计和理解至关重要,因为它是大多数算术运算的基础。定点加法涉及固定小数点位置的二进制数的相加,理解其工作原理有助于掌握其他复杂的算术运算单元(如ALU)的设计。 实验二和三分别涵盖了定点乘法和寄存器堆的实现。定点乘法器比加法器更复杂,需要处理溢出和进位问题。寄存器堆则是CPU中的临时存储单元,用于存储中间运算结果和指令操作数,对提高CPU性能有直接影响。 实验四到六逐步引导学生实现ALU(算术逻辑单元)、存储器和单周期CPU。ALU是CPU的核心,执行基本的算术和逻辑操作;存储器是保存数据的地方,包括随机访问存储器(RAM)和只读存储器(ROM);单周期CPU在每个时钟周期内完成一个指令的执行,虽然效率较低,但便于理解和分析。 实验七和八则进一步升级到多周期CPU,这种设计通过拆分指令执行过程为多个阶段,提高了处理速度。静态5级流水线CPU设计在实验九中介绍,流水线技术是现代CPU提高执行效率的关键,它将指令的执行分解为取指、译码、执行、写回等多个阶段,允许多条指令同时在不同阶段进行。 课程设计部分鼓励学生对CPU进行优化,可能涉及到指令集的扩展和流水线的改进,例如,通过添加新的指令来增强CPU的功能,或者优化流水线以减少数据依赖导致的延迟。 附录中列出了实现的MIPS指令集和cp0寄存器,MIPS是一种广泛使用的精简指令集计算机(RISC)架构,用于教学和实际应用。cp0寄存器是MIPS处理器中的系统控制寄存器,管理系统的状态和控制功能。 LS-CPU-EXB-002实验箱及其配套手册提供了一个全面的学习环境,让学生能够从基础到高级,逐步掌握CPU设计与体系结构的各个方面,为未来深入研究计算机硬件打下坚实基础。通过动手实践,学生不仅可以理解理论知识,还能培养解决实际问题的能力,这对于成为一名成功的IT专业人士至关重要。

剩余216页未读,继续阅读

- 粉丝: 29

- 资源: 332

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (源码)基于ESP8266和Arduino的HomeMatic水表读数系统.zip

- (源码)基于Django和OpenCV的智能车视频处理系统.zip

- (源码)基于ESP8266的WebDAV服务器与3D打印机管理系统.zip

- (源码)基于Nio实现的Mycat 2.0数据库代理系统.zip

- (源码)基于Java的高校学生就业管理系统.zip

- (源码)基于Spring Boot框架的博客系统.zip

- (源码)基于Spring Boot框架的博客管理系统.zip

- (源码)基于ESP8266和Blynk的IR设备控制系统.zip

- (源码)基于Java和JSP的校园论坛系统.zip

- (源码)基于ROS Kinetic框架的AGV激光雷达导航与SLAM系统.zip

信息提交成功

信息提交成功

评论0